Ampliación de la arquitectura RISC-V con aceleradores específicos de dominio

Cuando comenzó el mercado de RISC-V, la prisa inicial fue la de reducir los costos de diseños que de otro modo habrían utilizado arquitecturas de conjuntos de instrucciones (ISA) de CPU patentadas en aplicaciones profundamente integradas. Cuando estos sistemas en chips (SoC) comenzaron a fabricarse en la tecnología de proceso de semiconductores FinFET, los costos de la máscara se volvieron tan caros que muchas máquinas de estados finitos fueron reemplazadas por micro secuenciadores programables basados en el conjunto de instrucciones RISC-V. Estos crearon la emoción inicial y luego la mercantilización de núcleos RISC-V simples de 2014 a 2018.

A medida que la arquitectura RISC-V se volvió más madura y los diseñadores de SoC se familiarizaron con ISA, encontró adopción en aplicaciones en tiempo real que exigían un alto rendimiento:en particular, sirviendo como interfaz para motores de aceleración altamente especializados para aplicaciones como inteligencia artificial. . Una razón clave para esta adopción es que RISC-V es una arquitectura abierta para que los usuarios agreguen instrucciones, por lo que los procesadores RISC-V no tenían que tratar los aceleradores como dispositivos de E / S asignados en memoria, como era el caso de las arquitecturas tradicionales. . En su lugar, pueden utilizar un coprocesador de baja latencia.

La disponibilidad de procesadores RISC-V con extensión vectorial permitió a los aceleradores especializados procesar las capas entre los bucles internos del kernel para aplicaciones como inteligencia artificial (IA), realidad aumentada / realidad virtual (AR / VR) y visión por computadora. Pero esto no es posible sin extensiones especialmente diseñadas, como una instrucción de carga personalizada para llevar datos de un acelerador externo a registros vectoriales internos.

El motor de este cambio es el modelo de programación que demandan estas aplicaciones. El acelerador de propósito especial, que es una gran variedad de multiplicadores, es altamente eficiente, aunque bastante inflexible, tanto en las operaciones que realiza como en el movimiento de datos. Compare esto con un procesador de uso general como el x86 que le permite al programador la máxima flexibilidad para programar sin tener en cuenta las limitaciones del motor de cálculo, si solo el diseño tiene 100 W de potencia para quemar, lo que la mayoría no tiene.

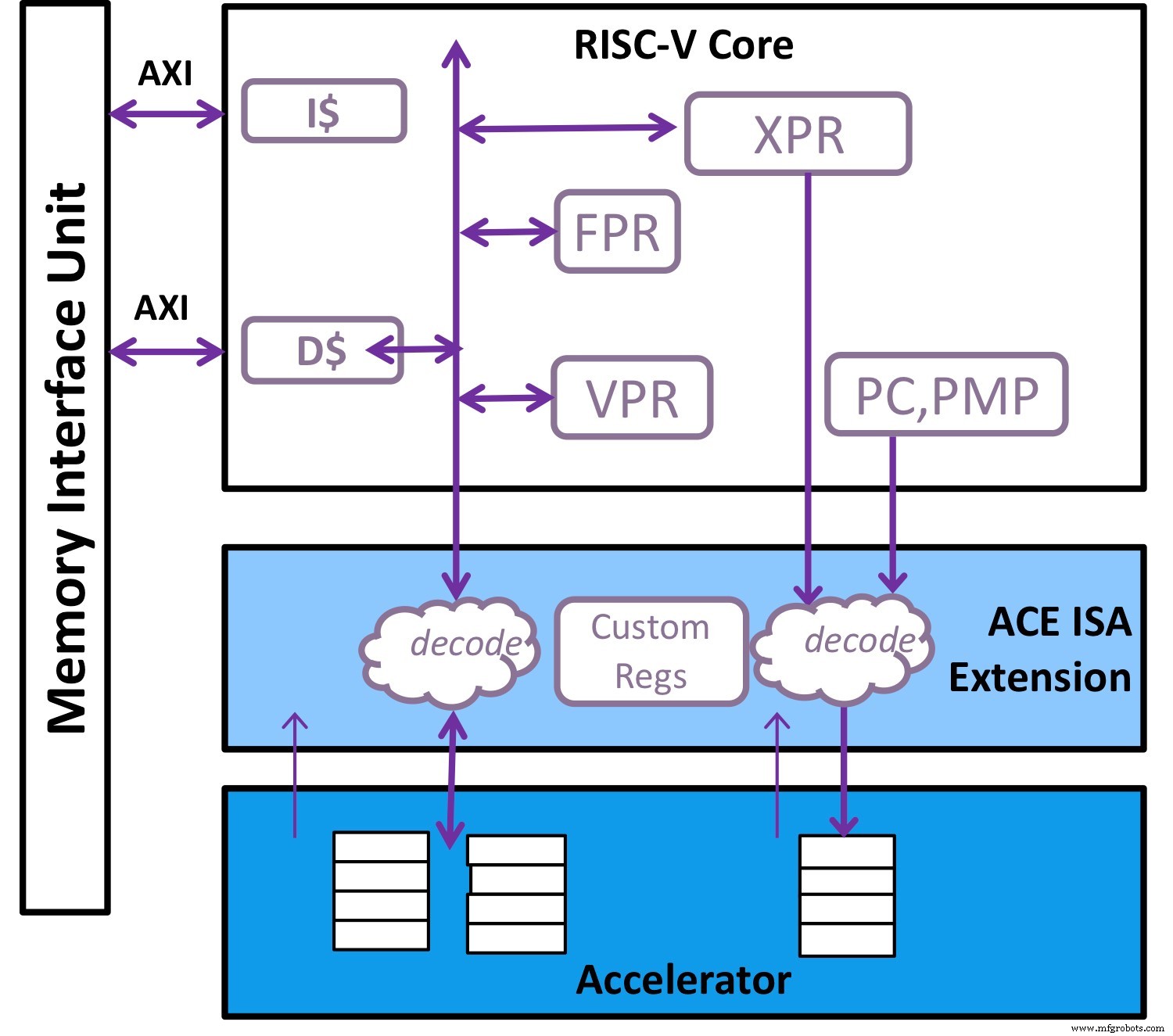

La extensión vectorial estándar en RISC-V aumentada con instrucciones personalizadas especializadas es un complemento ideal para el acelerador (Imagen:Tecnología Andes)

La solución obvia es combinar la flexibilidad de una CPU de propósito general con un acelerador que puede manejar una tarea muy específica (ver figura anterior). En RISC-V, la extensión de vector estándar en maduración aumentada con instrucciones personalizadas especializadas es un compañero ideal para el acelerador, y esta adopción se ha hecho evidente en los últimos 18 meses a medida que las soluciones de aceleración de dominio específico (DSA) convergen en plataformas RISC-V.

Para hacer posible esta visión, hemos observado que el acelerador debe poder ejecutar su propio conjunto de comandos utilizando sus propios recursos, incluida la memoria. Para agilizar la ejecución del acelerador, el RISC-V también debería poder aplanar el microcódigo lo más ancho que sea necesario y empaquetar toda la información de control requerida en el acelerador en un solo comando. Además, este conjunto de comandos del acelerador debe conocer los registros escalares y vectoriales del procesador RISC-V, así como sus propios recursos, como los archivos de registro de control y la memoria.

Cuando el acelerador necesita ayuda para reordenar o manipular datos de formas especiales, la arquitectura de Andes se ocupa de esto con una unidad de procesamiento vectorial (VPU) para manejar el complicado trabajo de permutaciones de datos:cambio, recopilación, compresión y expansión. Entre capas, hay algunos granos que involucran complicaciones. Aquí, la VPU proporciona la flexibilidad para ayudar a abordar esa necesidad. En estos sockets, el acelerador y la VPU realizan una gran cantidad de cálculos en paralelo; por lo tanto, agregamos hardware para aumentar significativamente el ancho de banda del subsistema de memoria para que coincida con la demanda de cómputo, incluidas, entre otras, transacciones de captura previa y sin bloqueo con devolución fuera de orden.

El primer procesador vectorial RISC-V de Andes Technology que admite la última versión 0.8 de extensión V, el NX27V, realiza cada cálculo en la unidad de enteros de 8, 16 y 32 bits a puntos flotantes de 16 y 32 bits. También es compatible con los formatos Bfloat16 e Int4 para reducir el almacenamiento y el ancho de banda de transferencia para los valores de peso de los algoritmos de aprendizaje automático. La especificación vectorial RISC-V es muy flexible al permitir a los diseñadores configurar los parámetros de diseño clave, como la longitud del vector, el número de bits en cada registro vectorial y el ancho de SIMD, el número de bits procesados por el motor vectorial en cada ciclo.

El NX27V tiene una longitud de vector de hasta 512 bits y se puede expandir a 4096 bits combinando hasta ocho registros de vector. Con múltiples unidades funcionales agregadas que operan en tuberías paralelas, puede mantener los rendimientos de cómputo necesarios en aplicaciones diversificadas. En una implementación configurada con una longitud de vector de 512 bits y el mismo ancho de SIMD, alcanza una velocidad de 1 GHz en 7 nm en el peor de los casos dentro de un área de 0,3 mm 2 . Para el soporte de desarrollo de software, además del compilador, el depurador, las bibliotecas vectoriales y el simulador de ciclo, una herramienta de visualización para la tubería NX27V, Clarity, ayuda a analizar y optimizar el rendimiento de los bucles críticos. Esta solución ya ha comenzado a distribuirse en nuestro programa de acceso anticipado.

En los últimos 15 meses, hemos visto una gran demanda de alto rendimiento con la adición de una potente extensión vectorial RISC-V, combinándola con un subsistema de memoria de gran ancho de banda y acercando el acelerador a la CPU. Este es el tipo de requisito informático que creemos que impulsará la demanda de procesamiento vectorial y RISC-V.

>> Este artículo se publicó originalmente el nuestro sitio hermano, EE Times.

Incrustado

- Presentamos la IIC, ¡ahora con OpenFog!

- La segunda versión de la arquitectura de referencia de Internet industrial está disponible con Databus en capas

- Lucha contra incendios forestales con IoT

- Alcanzando lo inalcanzable con IoT satelital

- Una guía para acelerar aplicaciones con las instrucciones personalizadas de RISC-V adecuadas

- Diseñando el futuro con robótica

- Impresión del fusible 1 con el fusible 1

- ¡¿Qué hago con los datos ?!

- Edge computing:la arquitectura del futuro

- Protección del vector de amenazas de IoT

- En la carretera con IoT