Una guía para acelerar aplicaciones con las instrucciones personalizadas de RISC-V adecuadas

La arquitectura de conjunto de instrucciones abierto (ISA) de RISC-V permite una amplia flexibilidad en la implementación y ofrece características opcionales que pueden permitir nuevos enfoques para resolver las compensaciones de diseño de hardware y software. Sobre la base de una estructura modular, se pueden utilizar una serie de extensiones y opciones estándar para configurar el procesador base como punto de partida. Sin embargo, el verdadero valor radica en las oportunidades que RISC-V ofrece a los desarrolladores para crear nuevas extensiones, instrucciones y configuraciones que satisfagan de manera única las necesidades de sus ideas de aplicaciones innovadoras.

El desafío del software para las ISA fijas

Tradicionalmente, las ISA han sido propiedad intelectual (PI) de organizaciones comerciales que querían vender microprocesadores o microcontroladores, o que querían licenciar sus diseños para que otros los usaran. Los desarrolladores integrados deben ejecutar software de evaluación comparativa para determinar qué solución está mejor optimizada para las necesidades de sus aplicaciones. Debido al costo de desarrollar una ISA independiente con todo el ecosistema necesario, los proveedores de semiconductores dependían cada vez más de las ISA fijas estándar ofrecidas por los principales proveedores de IP, confiando en la Ley de Moore y los periféricos integrados para brindar diferenciación, como potencia ultrabaja. , a sus clientes.

El desafío aquí es que las instrucciones utilizadas para ejecutar el código no se pueden cambiar. Por lo tanto, no se pueden realizar las eficiencias que podrían obtenerse potencialmente mediante, por ejemplo, una instrucción optimizada para un algoritmo de cifrado. Esto puede significar que la aplicación del desarrollador es demasiado lenta, que potencialmente consume demasiada energía o que regularmente no cumple con una fecha límite estricta en tiempo real en un ciclo de control. Incluso con la mejor voluntad del mundo, estos son factores que son difíciles de resolver únicamente con mejoras en la fabricación de semiconductores o reducciones de procesos.

El RISC-V ISA comenzó como un proyecto en la Universidad de California, Berkeley y ahora es mantenido por la Asociación Internacional RISC-V, un grupo sin fines de lucro con más de 300 miembros. Estos contribuyen a las especificaciones de ISA, herramientas de software, como simuladores y compiladores, y el resto del ecosistema que se necesita para respaldar tal empresa. Si tiene sentido usarlo o no, depende de si se puede aprovechar uno de dos factores:es gratis en términos de licencia o la libertad que ofrece.

Al ser abierto y de libre acceso, proporciona una plataforma de procesamiento básica que puede ser utilizada fácilmente tanto por la academia para la enseñanza y la investigación como para aplicaciones comerciales. Una ISA abierta también admite una serie de modelos comerciales para desarrolladores que buscan obtener IP de semiconductores, desde el proveedor de IP comercial hasta proyectos de código abierto y diseños autoconstruidos. Las organizaciones comerciales también encuentran esto atractivo, utilizándolo en FPGA, SoC o incluso en el núcleo de un microcontrolador o una oferta de producto estándar.

Gracias a la libertad que ofrece, el mundo académico puede investigar nuevos enfoques para abordar los desafíos informáticos, implementando cualquier cosa, desde nuevas instrucciones y otros aceleradores, diseños heterogéneos de múltiples núcleos y muchos núcleos, además de diferentes opciones de microarquitectura. Muchas de estas opciones también son atractivas para las empresas emergentes y las empresas que buscan abordar desafíos complejos, como los conjuntos de chips de inteligencia artificial (AI) de bajo consumo que operan en el borde, agregando instrucciones personalizadas ajustadas a los requisitos de la aplicación final.

Como el ecosistema se ha establecido con la flexibilidad RISC-V incorporada, cualquier configuración estándar o extensión personalizada debería poder aprovechar las herramientas y el software dentro del marco compatible con ISA.

Comprensión de la flexibilidad del ISA RISC-V abierto

Gracias a la accesibilidad del RISC-V ISA y las herramientas asociadas, es sencillo iniciar un proyecto de investigación para evaluar su idoneidad para su uso en una aplicación específica. Las herramientas de simulación permiten probar un ISA base estándar para determinar el rendimiento listo para usar. Por ejemplo, un buen punto de partida sería una configuración RISC-V de 32 bits con un número entero "I" y extensiones "M" multiplicadas (que pueden denominarse RV32IM) que brinden soporte para un conjunto de instrucciones de números enteros de 32 bits básicos; hay más opciones disponibles, pero esto es suficiente para este ejemplo. A continuación, se crea una instancia junto con una memoria simulada que incluye retrasos de acceso y estados de espera.

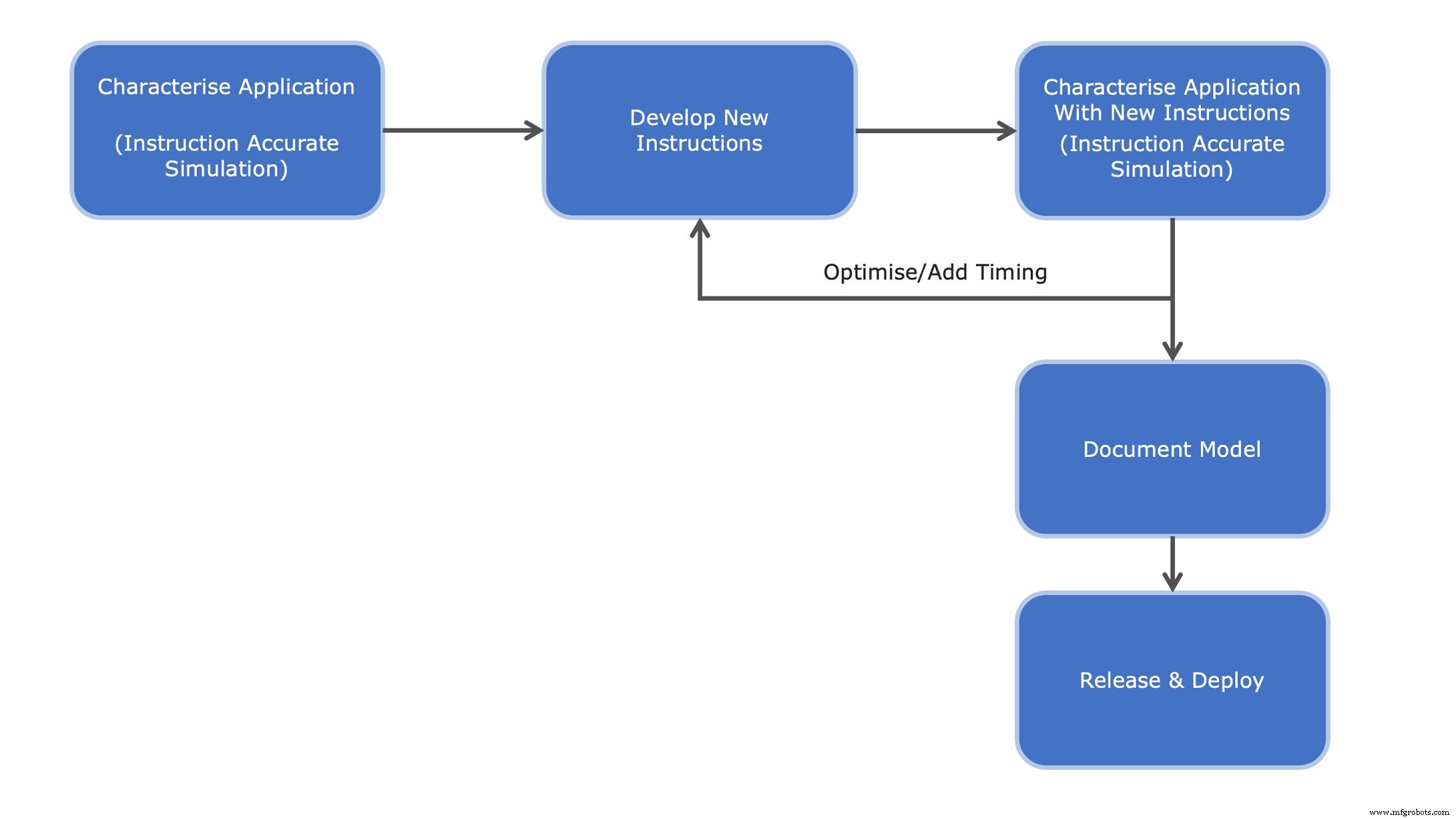

Una aplicación escrita en C / C ++ se puede compilar de forma cruzada utilizando cadenas de herramientas estándar. Esto podría ejecutarse en bare metal o como parte de un sistema operativo (en tiempo real) (RTOS / OS). El código binario resultante se ejecuta luego utilizando herramientas como un simulador de conjunto de instrucciones (ISS) que permite integrar y simular el modelo de procesador base elegido (figura 1). Este entorno también proporciona funcionalidad estándar de entrada / salida y acceso al sistema de archivos del host. Las herramientas de entorno de desarrollo integrado (IDE) estándar, como Eclipse, se pueden utilizar para controlar la ejecución del código, interactuando a través del depurador GNU GDB.

A partir de aquí, a través de un proceso de elaboración de perfiles y análisis, se identifican, diseñan y modelan los candidatos a la instrucción. Al utilizar el código de la aplicación original como modelo funcional básico, la mejora resultante se puede probar, verificar y comparar el rendimiento rápidamente. Esta rápida iteración de creación de perfiles y análisis permite una rápida selección y optimización de las instrucciones que vale la pena implementar. La documentación se puede generar a partir del modelo y forma la base de una especificación de función para el diseño de lógica de transferencia de registro (RTL) y un modelo optimizado.

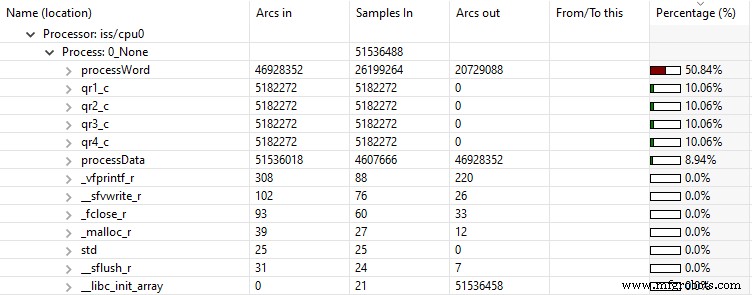

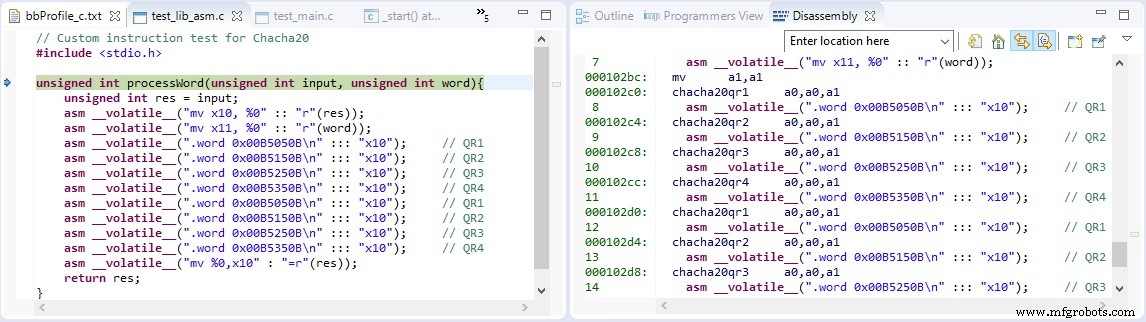

Por ejemplo, un algoritmo de cifrado como ChaCha20 puede ser fundamental para una aplicación en particular. El código fuente disponible puede compilarse para una base RV32IM “básica”, ejecutarse y luego analizarse con el tiempo estimado del ciclo de instrucción utilizando un perfil de bloque básico para determinar cuánto tiempo se dedicó a qué secciones del código. El núcleo del algoritmo ChaCha20 hace un uso intensivo de XOR y las instrucciones de rotación conocidas como cuartos de ronda (figura 2). Los resultados de la creación de perfiles de bloques destacan inmediatamente que la mayor parte del tiempo de ejecución se dedica a estas funciones.

La visualización gráfica de estos puntos de acceso también se puede generar mediante el uso de una herramienta de verificación, análisis y elaboración de perfiles (VAP). En lugar de proporcionar una salida textual, el tiempo de ejecución se proporciona como un árbol de estadísticas plegables, lo que ayuda a visualizar mejor los puntos de acceso con una alta proporción de instrucciones ejecutadas. Esto se puede ver en la figura 3 donde la función processWord () implementa el algoritmo ChaCha20, llamando a su vez a los cuatro qrx_c funciones para implementar las funciones de cuarto de ronda requeridas.

Revisando el código de ensamblador generado por el compilador y / o ejecutando un perfil de bloques básico, es posible determinar qué instrucciones y combinaciones de instrucciones se han usado para implementar el algoritmo. A partir de aquí, el siguiente paso es determinar qué instrucciones personalizadas, dentro de los límites de las especificaciones de la ISA, podrían potencialmente aumentar la velocidad de ejecución.

Determinación de la mejora potencial que podría ofrecer RISC-V

El algoritmo ChaCha20 hace un uso intensivo de un XOR junto con una rotación a la izquierda de 7, 8, 12 y 16 bits. El uso de las instrucciones disponibles de la especificación básica RV32IM muestra que esto requiere una instrucción XOR seguida de una instrucción de desplazamiento a la izquierda. Esto significa que existe la posibilidad de optimizar estos dos pasos en cuatro instrucciones dedicadas que implementan un XOR junto con 7, 8, 12 o 16 bits de rotación a la izquierda.

Al ser una arquitectura de almacenamiento de carga, cualquier instrucción personalizada debe asumir que los datos que se van a manipular ya residen en uno de los registros de 32 bits de este RISC-V. Esto determina inmediatamente que se necesitará una instrucción de tipo R (registro) que se puede ubicar en custom-1 decodificar el espacio (figura 4).

La ISA proporciona una estructura clara para tales instrucciones. Siguiendo estas reglas, podemos determinar rápidamente cómo codificar nuestras nuevas instrucciones. Los 7 bits inferiores se definen como el código de operación al que se le asigna un valor que lo marca como una instrucción personalizada en custom-1 decodificar el espacio. Esto es a diferencia del OP o OP-IMM códigos de operación que se utilizan para las instrucciones XOR existentes y shift-left respectivamente.

La ISA proporciona una estructura clara para tales instrucciones. Siguiendo estas reglas, podemos determinar rápidamente cómo codificar nuestras nuevas instrucciones. Los 7 bits inferiores se definen como el código de operación al que se le asigna un valor que lo marca como una instrucción personalizada en custom-1 decodificar el espacio. Esto es a diferencia del OP o OP-IMM códigos de operación que se utilizan para las instrucciones XOR existentes y shift-left respectivamente.

Se reservan tres bloques de bits predefinidos en la definición de ISA para prescribir los dos registros de origen y el registro de destino para el resultado. Esto deja un bloque de bits conocido como funct3 . Estos tres bits nos proporcionan espacio para codificar ocho posibles instrucciones, cuatro de las cuales se utilizarán en este ejemplo.

Sin requerir la implementación de hardware detallada del RTL para estas instrucciones, es posible simularlas en el entorno ISS para ver si serían de algún beneficio para el desafío que se enfrenta. Las cuatro nuevas instrucciones se modelan utilizando la interfaz de programación de aplicaciones (API) VMI de plataformas virtuales abiertas (OVP). Esto permite al desarrollador iterar rápidamente el diseño de las instrucciones que proporcionan el resultado deseado óptimo basado en las nuevas instrucciones para la aplicación de destino. Solo una vez que esto se haya logrado, es necesario comprometer recursos para una implementación de RTL.

A los efectos de la evaluación funcional inicial de las instrucciones, existen dos enfoques posibles. La primera es llamar a la versión original C / C ++ del algoritmo, vinculando las nuevas instrucciones a esta función (figura 5a). El segundo es implementarlos como instrucciones morph VMI que crean el mismo comportamiento (figura 5b). Esto tiene la ventaja de ser más eficiente y es el enfoque recomendado.

Por supuesto, la mera existencia de nuevas instrucciones no significa que un compilador pueda hacer uso de ellas inmediatamente. Por lo tanto, la aplicación C / C ++ original necesita ser reescrita usando ensamblador en línea y compilada de manera cruzada para hacer uso de las nuevas instrucciones. Como la elaboración de perfiles y el análisis de las instrucciones candidatas pueden ser una tarea iterativa, el enfoque basado en intrínsecos proporciona la forma más eficaz de adaptar la aplicación C original para utilizar las nuevas instrucciones personalizadas.

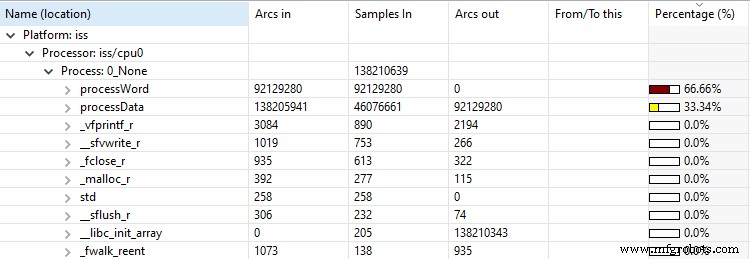

La implementación básica de RISC-V cargada en el simulador también necesita conocer las nuevas instrucciones para poder beneficiarse de ellas. Esto se logra incluyéndolos en el modelo antes de volver a ejecutar la simulación. En este ejemplo en particular, repetir el perfil indica menos tiempo total dedicado a realizar el algoritmo (figura 6). La herramienta de creación de perfiles Imperas VAP muestra que processWord () La función, que utiliza las instrucciones en línea dedicadas, ahora representa el 66% de la ejecución general del algoritmo, pero el tiempo de ejecución general del algoritmo se reduce considerablemente (figura 6b).

Resultados con la implementación de C original

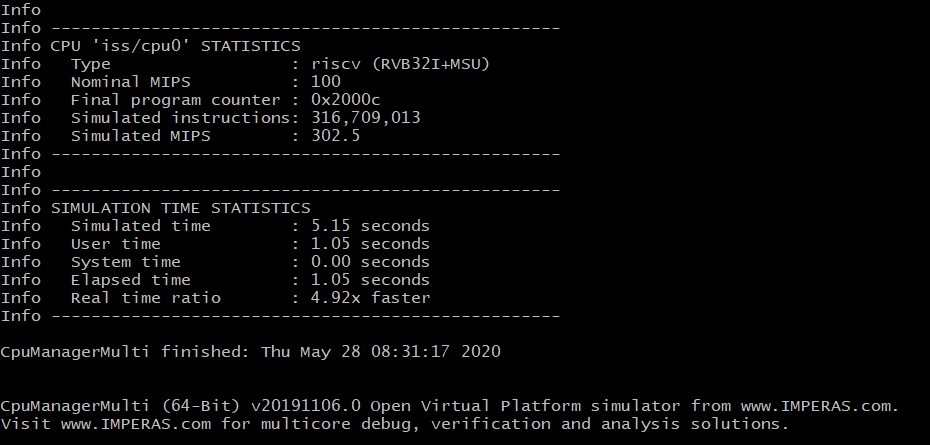

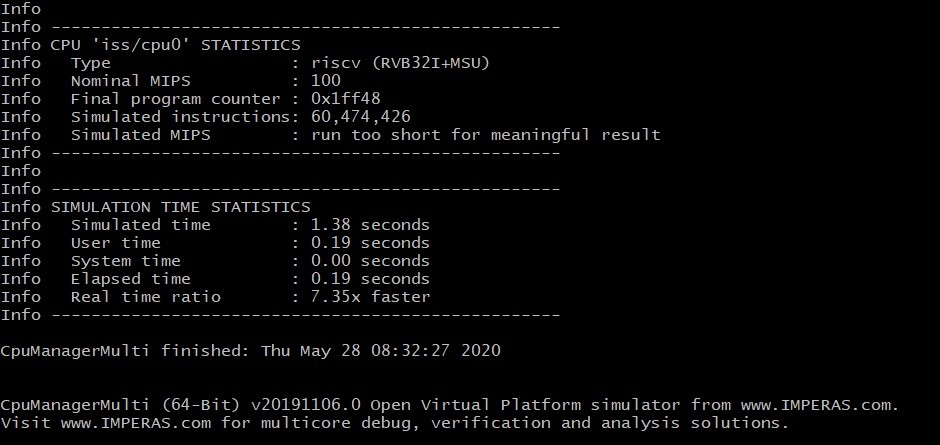

Información Instrucciones simuladas:316,709,013

Información Tiempo simulado:5,15 segundos

Resultados con instrucciones personalizadas

Información Instrucciones simuladas:60,474,426

Información Tiempo simulado:1,38 segundos

Una vez que se ha determinado la funcionalidad correcta, el modelo se refina aún más declarando el tiempo de ejecución de cada instrucción en ciclos de procesador. Luego, se pueden usar más rondas de simulación para determinar cualquier mejora en el rendimiento, incluso teniendo en cuenta los estados de espera asociados con los accesos a la memoria que pueden ocurrir en una eventual implementación de hardware.

Gracias a la estrecha integración con IDE de código abierto y herramientas GDB comunes, se puede realizar una depuración completa de la solución junto con el diseño optimizado de RISC-V antes de comprometer el diseño con una implementación de hardware (figura 7).

Pasar de la simulación a la implementación

Una vez determinada la mejora potencial del rendimiento, el siguiente paso requiere la implementación de las cuatro nuevas instrucciones en RTL. Gracias al trabajo preliminar realizado, esto se convierte en la especificación funcional que define los requisitos y también se puede utilizar como parte del plan de prueba de verificación RTL como modelo de referencia de oro. Si bien el uso de funciones intrínsecas en la aplicación C ayudó a la elaboración de perfiles y el análisis de instrucciones personalizadas, este enfoque también se puede utilizar para el desarrollo futuro del código de producción o se puede considerar para posibles mejoras en la cadena de herramientas del compilador.

La otra tarea esencial restante, la documentación, también es un proceso simple. Todos los modelos de procesadores rápidos de plataformas virtuales abiertas (OVP) incluyen documentación que se puede ampliar para cubrir la funcionalidad de cambios y modificaciones. Siguiendo la plantilla proporcionada, las nuevas instrucciones se pueden declarar y describir, lo que permite a la comunidad de desarrolladores descubrir su capacidad y hacer uso de ellas. Luego, la documentación se convierte en un archivo TeX desde el cual se puede generar un PDF (figura 8).

Resumen

Con las libertades del ISA abierto de RISC-V, además de las opciones y características estándar definidas en la especificación, los usuarios pueden desarrollar más extensiones e instrucciones personalizadas. En su forma más simple, permite modelos de negocios nuevos y creativos, incluidas implementaciones comerciales y de código abierto, y además permite una libertad más amplia para explorar características de valor agregado más allá de los enfoques tradicionales convencionales.

Sin embargo, el verdadero valor proviene de tomar un núcleo base completo, documentado y compatible y modificarlo para satisfacer las necesidades específicas de la aplicación. Mediante un análisis cuidadoso de la aplicación, la elaboración de perfiles de código y la simulación, se pueden lograr mejoras de rendimiento significativas que no se podrían lograr mediante ISA fijas. Todo esto se puede desarrollar y perfilar con cargas de trabajo de aplicaciones reales antes de comenzar la implementación detallada del hardware.

Incrustado

- Perfilado de aplicaciones distribuidas con Perf

- Una breve guía para la impresión 3D con Binder Jetting

- Una guía para la impresión 3D con titanio

- Microchip:escale aplicaciones espaciales con MCU Core tolerantes a la radiación de COTS

- Renesas:MCU RX72M con soporte EtherCAT para aplicaciones industriales

- Axiomtek:sistema integrado con conmutador PoE gestionado de capa 2 integrado

- Renegociación de costos con proveedores existentes:una guía

- Enrutador CNC para madera:con impresionantes aplicaciones

- Introducción a la IA en seguros:una guía introductoria

- 5 aplicaciones del mundo real de la IA en medicina (con ejemplos)

- Una guía para zapatas y pastillas de freno personalizadas para aplicaciones ferroviarias de alta velocidad