Una referencia de voltaje sin resistencia de baja potencia a nanoescala con PSRR alto

Resumen

En este artículo, se presenta una referencia de voltaje subumbral sin resistencia de nanovatios con una tasa de rechazo de la fuente de alimentación alta (PSRR). Se propone un divisor de voltaje MOS autopolarizado para proporcionar corriente de polarización para toda la referencia de voltaje, que es una corriente de coeficiente de temperatura positivo (TC) que contiene características de voltaje umbral. Al inyectar la corriente generada en un transistor con un voltaje de umbral diferente, se realiza un voltaje de umbral delta con un TC negativo muy reducido y se compensa la temperatura mediante un elemento TC positivo generado al mismo tiempo. Por lo tanto, se logra una referencia de voltaje estable a la temperatura en el método compactado propuesto con bajo consumo de energía y alto PSRR. Los resultados de la verificación con tecnología CMOS de 65 nm demuestran que el voltaje de suministro mínimo puede ser tan bajo como 0,35 V con 0,00182 mm 2 área activa. El voltaje de referencia generado es 148 mV, con un TC de 28 ppm / ° C para el rango de temperatura de - 30 a 80 ° C. La sensibilidad de la línea es de 1,8 mV / V y el PSRR sin ningún condensador de filtrado a 100 Hz es de 53 dB con un consumo de energía de 2,28 nW.

Introducción

La referencia de voltaje es uno de los módulos centrales en los sistemas electrónicos, que se usa ampliamente en electrónica médica, administración de energía, sensores ambientales inalámbricos y circuitos de comunicación. A medida que el voltaje de suministro de los sistemas electrónicos continúa disminuyendo con la mejora de la tecnología, los requisitos para una referencia de voltaje de baja potencia con tecnología a nanoescala aumentan de manera crítica [1, 2].

Las referencias de voltaje convencionales se basan en un circuito de referencia de banda prohibida (BGR), que es una suma ponderada de V SER y voltaje térmico [3, 4]. Sin embargo, debido al comportamiento de temperatura no lineal de V SER , es esencial utilizar enfoques de compensación de curvatura para mejorar la precisión de BGR [5, 6]. Otra desventaja de BGR es el consumo de energía. La V SER es de alrededor de 0,7 V sin contraerse con la mejora del proceso, lo que restringe absolutamente la tensión de alimentación. Esto hace que los BGR no sean adecuados para aplicaciones de baja tensión y nanoescala.

Para lograr un funcionamiento de baja potencia, se adoptan gradualmente referencias de voltaje subumbral solo MOS [7,8,9,10]. Como los transistores en una región de inversión débil tienen ventajas inherentes en aplicaciones de baja potencia con una corriente bastante pequeña, el consumo de energía de las referencias de voltaje relativo se puede reducir de manera efectiva. Además, dado que las características del transistor de efecto de campo semiconductor de óxido metálico (MOSFET) son consistentes con la mejora del proceso, la referencia de voltaje basada en MOSFET es más adaptable a tecnologías avanzadas. Además, también debe evitarse el uso de resistencias en aplicaciones de baja potencia. Dado que la corriente en la referencia de voltaje suele ser inversamente proporcional al valor de resistencia, la disipación de baja potencia significa resistencias de alta resistencia [10], que pueden inducir un gran ruido que ocupa un área de chip grande.

La relación de rechazo de la fuente de alimentación (PSRR) es otro parámetro importante de referencia de voltaje. Las soluciones convencionales para mejorar la PSRR tienen como costo el área del chip y el consumo de energía, como amplificadores adicionales [11], transistores de canal largo [12], estructuras de cascodo y etapa de ganancia adicional [13].

Para superar los problemas mencionados anteriormente, en este informe se propone una referencia de voltaje subumbral sin resistencia basada en MOSFET de nano vatios con alto PSRR, que es adecuada para tecnología avanzada, como el proceso a nanoescala. En la referencia de voltaje propuesta se adopta un divisor de voltaje MOSFET autopolarizado para la mejora de PSRR, que puede generar una corriente de coeficiente de temperatura positivo (TC) que contiene características de voltaje umbral. La corriente sirve como corrientes de polarización para toda la referencia de voltaje. Además, el voltaje de umbral incrustado en la corriente de polarización se reproduce inyectando corriente de polarización en el MOSFET con diferentes voltajes de umbral en el papel. Con el método propuesto, un voltaje de umbral delta ( ∆V TH ) con TC negativo muy reducido. Además, también se obtiene un ítem ponderado proporcional a la temperatura absoluta (PTAT), mientras que una suma ponderada de ∆V TH y el voltaje PTAT se realiza al mismo tiempo. Debido a la cancelación mutua de TC de dos voltajes de umbral diferentes, el voltaje PTAT requerido se puede reducir en gran medida para la compensación de temperatura. Con este método, se logra una referencia de voltaje sin resistencia solo MOSFET mediante una estructura compacta con bajo consumo de energía.

Método

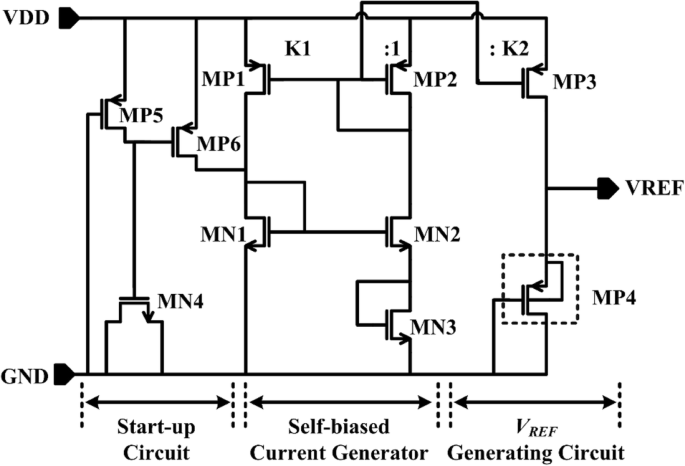

Como se muestra en la Fig.1, la referencia de voltaje propuesta se compone de un circuito de arranque, un generador de corriente autopolarizado y un V REF circuito generador. Todos los MOSFET de canal n son un semiconductor de óxido metálico de tipo N de voltaje de umbral medio (mvt NMOS). MP4 es un semiconductor de óxido de metal de tipo P con transistor de voltaje de umbral alto (hvt PMOS), y los otros MOSFET de canal p son un PMOS de voltaje de umbral medio (mvt PMOS). Todos los transistores que se muestran en la Fig. 1 operan en la región del subumbral, excepto los del circuito de arranque.

Esquema de la referencia de voltaje propuesta

Circuito de puesta en marcha

El circuito de puesta en marcha consta de MP5, MP6 y MN4. Al comienzo de una etapa de encendido, el potencial de puerta de MP6 es bajo y MP6 está encendido. La corriente generada por MP6 hace que el potencial de puerta de MN1 y MN2 aumente, y todo el circuito comienza a funcionar. Al mismo tiempo, MP5 carga el condensador de arranque, MN4. Con el procedimiento de carga de MN4, el transistor MP6 se apaga gradualmente, lo que hace que el circuito de arranque se separe del núcleo de la referencia de voltaje propuesta sin disipación de potencia adicional. Mediante este método, la referencia de voltaje propuesta puede funcionar en un punto de operación deseado mientras se evita un punto de degeneración.

Generador de corriente autodidacta

La parte central en la Fig. 1 es un generador de corriente autopolarizado, que se basa en un divisor de voltaje solo MOSFET. En esta parte se genera la corriente de polarización con TC positivo para toda la referencia de voltaje, que es relevante para el voltaje de umbral medio de NMOS. La característica única de la corriente de polarización presentada se adopta para realizar la referencia de voltaje propuesta de una manera conveniente, que se analizará en la sección "Método".

Con respecto a la característica de corriente de voltaje de un transistor en la región del subumbral, la corriente de drenaje del transistor en el subumbral se vuelve casi independiente de V DS con V DS > 4 V T , donde V T =kT / q es el voltaje térmico, k es la constante de Boltzmann, q es la carga elemental, y T es la temperatura absoluta. Por lo tanto, la corriente se puede expresar como:

$$ {I} _ {\ mathrm {D}} ={SI} _ {\ mathrm {SQ}} \ exp \ left (\ frac {V _ {\ mathrm {GS}} - {V} _ {\ mathrm { T} \ mathrm {H}}} {mV _ {\ mathrm {T}}} \ derecha) $$ (1)donde S =W / L es la relación de aspecto, m es el factor de pendiente subumbral, V TH es el voltaje de umbral, y I SQ representa la corriente específica y se presenta mediante:

$$ {I} _ {\ mathrm {SQ}} =\ mu {C} _ {\ mathrm {OX}} \ left (m-1 \ right) {V_T} ^ 2 $$ (2)donde μ es la movilidad del portador y C OX es la capacitancia de óxido por unidad de área.

Por lo tanto, las corrientes a través del divisor de voltaje solo MOSFET, formado por MN1, MN2 y MN3, se pueden expresar de la siguiente manera:

$$ {I} _ {\ mathrm {D} \ _ \ mathrm {MN} 1} ={S} _ {\ mathrm {MN} 1} {I} _ {\ mathrm {SQN}} \ exp \ left ( \ frac {V _ {\ mathrm {GS} \ _ \ mathrm {MN} 1} - {V} _ {\ mathrm {T} \ mathrm {HN}}} {mV _ {\ mathrm {T}}} \ right) $$ (3) $$ {I} _ {\ mathrm {D} \ _ \ mathrm {MN} 2} ={S} _ {\ mathrm {MN} 2} {I} _ {\ mathrm {SQN}} \ exp \ left (\ frac {V _ {\ mathrm {GS} \ _ \ mathrm {MN} 2} - {V} _ {\ mathrm {T} \ mathrm {HN}}} {mV _ {\ mathrm {T} }} \ derecha) $$ (4) $$ {I} _ {\ mathrm {D} \ _ \ mathrm {MN} 3} ={S} _ {\ mathrm {MN} 3} {I} _ {\ mathrm {SQN}} \ exp \ left (\ frac {V _ {\ mathrm {GS} \ _ \ mathrm {MN} 3} - {V} _ {\ mathrm {T} \ mathrm {HN}}} {mV_ { \ mathrm {T}}} \ right) $$ (5)donde yo SQN es la corriente específica de NMOS y V THN es el voltaje umbral de NMOS.

Dado que las relaciones de aspecto de MN2 y MN3 son las mismas y I D_MN2 =yo D_MN3 , V GS_MN2 = V GS_MN3 Está garantizado. Esto hace que V GS_MN1 =2 V GS_MN2 . Además, los transistores PMOS forman los espejos de corriente y definen las relaciones de corriente K 1 =S MP1 / S MP2 y K 2 =S MP3 / S MP2 . La relación de las corrientes de drenaje entre MN1 y MN2 se puede expresar como:

$$ {I} _ {\ mathrm {D} \ _ \ mathrm {MN} 1} ={K} _1 {I} _ {\ mathrm {D} \ _ \ mathrm {MN} 2} $$ (6)Combinado con las Ecs. (3) - (6), la V GS_MN2 y yo D_MN2 puede ser dado por:

$$ {V} _ {\ mathrm {GS} \ _ \ mathrm {MN} 2} ={mV} _ {\ mathrm {T}} \ ln \ left (\ frac {K_1 {S} _ {\ mathrm { MN} 2}} {S _ {\ mathrm {MN} 1}} \ right) $$ (7) $$ {I} _ {\ mathrm {D} \ _ \ mathrm {MN} 2} ={S} _ {\ mathrm {MN} 2} {I} _ {\ mathrm {SQN}} \ exp \ left (\ ln \ frac {K_1 {S} _ {\ mathrm {MN} 2}} {S _ {\ mathrm {MN } 1}} - \ frac {V _ {\ mathrm {T} \ mathrm {HN}}} {mV _ {\ mathrm {T}}} \ derecha) $$ (8)Para la conveniencia del análisis, Eq. (8) se puede abreviar como:

$$ {I} _ {\ mathrm {D} \ _ \ mathrm {MN} 2} ={aT} ^ {2- {n} _1} \ exp \ left (b- \ frac {V _ {\ mathrm {T } \ mathrm {HN}}} {mV _ {\ mathrm {T}}} \ derecha) $$ (9)donde a =S MN2 μ n 0 C OX ( m - 1) ( k / q ) 2 y b = En ( K 1 S MN2 / S MN1 ) son independientes de la temperatura, μ n 0 es un factor de movilidad del portador independiente de la temperatura, y n 1 es el término exponente de temperatura absoluta de la movilidad del portador, que suele rondar 1,5.

Como se muestra en la ecuación. (9), voltaje de umbral V THN es complementario a la temperatura absoluta (CTAT), mientras que el voltaje térmico V T es proporcional a la temperatura absoluta (PTAT). A medida que aumenta la temperatura, V THN / ( mV T ) se reducirá, de modo que se mejorarán las características de corriente positiva de la corriente de polarización.

Mediante este método, se logra una corriente de polarización TC positiva mediante la estructura de solo MOSFET, que lleva las características del voltaje umbral NMOS.

V REF Circuito generador

La V REF El circuito generador se muestra en la parte derecha de la Fig. 1, que solo está formado por dos transistores, MP3 y MP4. Debido a la operación de la región de subumbral, I D_MP4 se puede escribir como:

$$ {I} _ {\ mathrm {D} \ _ \ mathrm {MP} 4} ={S} _ {\ mathrm {MN} 4} {I} _ {\ mathrm {SQP}} \ exp \ left ( \ frac {\ mid {V} _ {\ mathrm {GS} \ _ \ mathrm {MP} 4} \ mid - \ mid {V} _ {\ mathrm {T} \ mathrm {HP}} \ mid} {mV_ {\ mathrm {T}}} \ right) $$ (10)donde yo SQP es la corriente específica de PMOS y V THP es la V TH de PMOS.

Desde yo D_MP4 =K 2 yo D_MN2 , las características del voltaje umbral NMOS, V THN , se puede transferir al nodo de salida y superponerse con las características del voltaje umbral de PMOS, V THP . De las Ecs. (8) y (10), V REF se puede escribir como:

$$ {V} _ {\ mathrm {REF}} =\ mid {V} _ {\ mathrm {T} \ mathrm {HP}} \ mid - {V} _ {\ mathrm {T} \ mathrm {HN} } + {mV} _ {\ mathrm {T}} \ ln \ left (\ frac {K_2 {S} _ {\ mathrm {MN} 2} {I} _ {\ mathrm {SQn}}} {S _ {\ mathrm {MP} 4} {I} _ {\ mathrm {SQP}}} \ right) + {mV} _ {\ mathrm {T}} \ ln \ left (\ frac {K_1 {S} _ {\ mathrm { MN} 2}} {S _ {\ mathrm {MN} 1}} \ right) $$ (11)Como se muestra en los dos primeros elementos de la ecuación. (11), se realiza un voltaje de umbral delta. Desde V TH = V TH0 - βT , donde V TH0 es el voltaje umbral a 0 K y β es el TC del voltaje umbral, el voltaje umbral delta generado es un complemento del voltaje de temperatura absoluta (CTAT) con un TC muy reducido con | βV THP |> βV THN . Además, dos voltajes PTAT adicionales se realizan simultáneamente y se muestran en los dos últimos elementos de la ecuación. (11), que se adoptan para cancelar el TC reducido del voltaje umbral delta. Por lo tanto, se logra un voltaje de referencia compactado estable a la temperatura sin una estructura complicada, que es estable a | V THP0 | - V THN0 .

En base al análisis anterior, en este documento se realiza una referencia de voltaje de solo MOSFET de baja potencia que solo requiere tres ramas en el núcleo. Con las características únicas de una fuente de corriente autopolarizada, se adopta un PMOS conectado por diodo para lograr un voltaje CTAT con TC reducido, generador de voltaje PTAT y suma ponderada al mismo tiempo. Además, la estructura propuesta solo está construida por MOSFET, y el voltaje de referencia generado es proporcional al voltaje del umbral delta. Por lo tanto, la referencia de voltaje propuesta es más adecuada para aplicaciones de bajo consumo de energía con tecnología a nanoescala, que puede extenderse aún más a tecnologías más avanzadas.

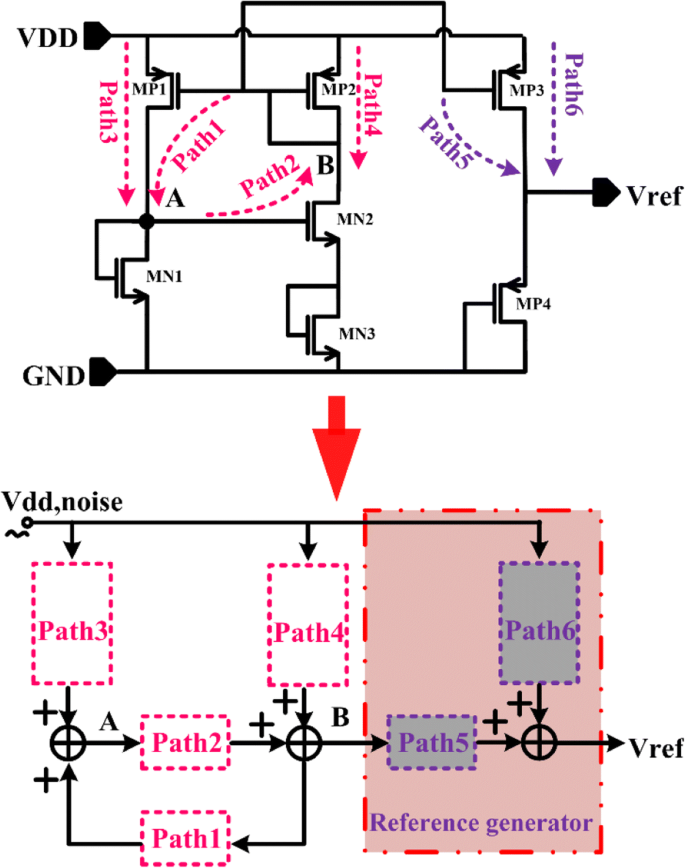

PSRR de referencia de voltaje propuesto

Para ilustrar el rendimiento del PSRR, las rutas desde el ruido de la tensión de alimentación hasta V REF y los diagramas de funciones equivalentes correspondientes se muestran en la Fig. 2.

Las rutas del ruido de la tensión de alimentación

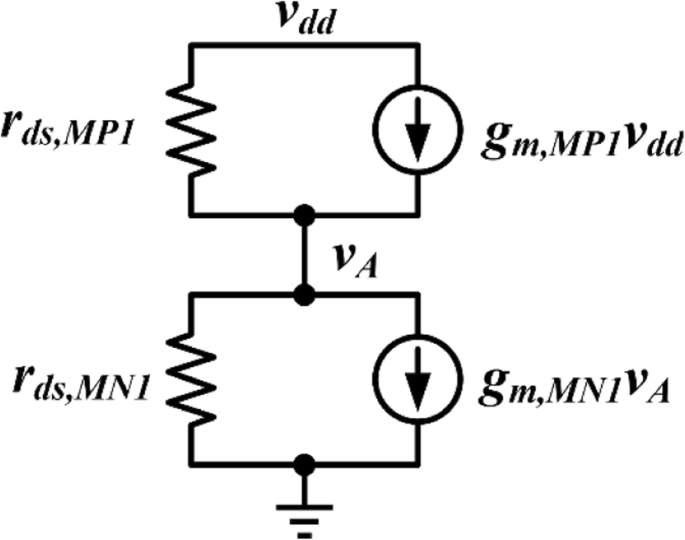

Con base en la Fig. 2, el modelo de pequeña señal de la ruta 3 se muestra en la Fig. 3, y se puede obtener la siguiente ecuación:

$$ \ frac {v _ {\ mathrm {dd}} - {v} _ {\ mathrm {A}}} {r _ {\ mathrm {ds}, \ mathrm {MP} 1}} + {g} _ {\ mathrm {m}, \ mathrm {MP} 1} {v} _ {\ mathrm {dd}} =\ frac {v _ {\ mathrm {A}}} {r _ {\ mathrm {ds}, \ mathrm {MN} 1}} + {g} _ {\ mathrm {m}, \ mathrm {MN} 1} {v} _ {\ mathrm {A}} $$ (12)

Modelo de pequeña señal de la ruta 3

De la ecuación. (12), la expresión del ruido de suministro a través de la ruta 3 al nodo A puede estar dada por:

$$ {Av} _ {\ mathrm {ruta} 3} =\ frac {v _ {\ mathrm {A}}} {v _ {\ mathrm {dd}}} =\ frac {r _ {\ mathrm {ds}, \ mathrm {MN} 1} + {g} _ {\ mathrm {m}, \ mathrm {MP} 1} {r} _ {\ mathrm {ds}, \ mathrm {MN} 1} {r} _ {\ mathrm {ds}, \ mathrm {MP} 1}} {r _ {\ mathrm {ds}, \ mathrm {MP} 1} + {r} _ {\ mathrm {ds}, \ mathrm {MN} 1} + {g } _ {\ mathrm {m}, \ mathrm {MN} 1} {r} _ {\ mathrm {ds}, \ mathrm {MN} 1} {r} _ {\ mathrm {ds}, \ mathrm {MP} 1}} $$ (13)La transconductancia del transistor que opera en la región del subumbral es g m = yo D / mV T . Por lo tanto, la relación entre g m, MP1 y g m, MN1 con la misma corriente se puede dar como g m, MP1 = g m, MN1 . Entonces, Eq. (13) se puede simplificar como:

$$ {Av} _ {\ mathrm {ruta} 3} \ aproximadamente 1 $$ (14)El nodo B también tiene un efecto en el nodo A a través de la ruta 1, pero el efecto es opuesto a la ruta 3, que se puede expresar como:

$$ {Av} _ {\ mathrm {ruta} 1} \ approx -1 $$ (15)Para V A =2 V GS, MN2 , la ganancia de la ruta 2 se da como:

$$ {Av} _ {\ mathrm {ruta} 2} =- \ frac {1} {2} {g} _ {\ mathrm {m}, \ mathrm {MN} 2} \ left (2 {r} _ {\ mathrm {ds}, \ mathrm {MN} 2} \ Big \ Vert \ frac {1} {g _ {\ mathrm {m}, \ mathrm {MP} 2}} \ right) \ approx - \ frac {1 } {2} $$ (16)El efecto de v dd en el nodo B a través de la ruta 4 se puede escribir como:

$$ {Av} _ {\ mathrm {ruta} 4} =\ frac {2 {r} _ {\ mathrm {ds}, \ mathrm {MN} 2}} {\ left (1 / {g} _ {\ mathrm {m}, \ mathrm {MP} 2} \ right) +2 {r} _ {\ mathrm {ds}, \ mathrm {MN} 2}} =\ frac {2 {g} _ {\ mathrm {m }, \ mathrm {MP} 2} {r} _ {\ mathrm {ds}, \ mathrm {MN} 2}} {1 + 2 {g} _ {\ mathrm {m}, \ mathrm {MP} 2} {r} _ {\ mathrm {ds}, \ mathrm {MN} 2}} $$ (17)Desde el nodo A al nodo B en la Fig.2, se pueden obtener dos ecuaciones adicionales, que son:

$$ {Av} _ {\ mathrm {ruta} 4} {v} _ {\ mathrm {dd}} + {Av} _ {\ mathrm {ruta} 2} {V} _ {\ mathrm {A}} ={V} _ {\ mathrm {B}} $$ (18) $$ {Av} _ {\ mathrm {ruta} 3} {v} _ {\ mathrm {dd}} + {Av} _ {\ mathrm { ruta} 1} {V} _ {\ mathrm {B}} ={V} _ {\ mathrm {A}} $$ (19)Según las ecuaciones (18) y (19), el ruido en V B puede ser dado por:

$$ {V} _ {\ mathrm {B}} =\ frac {2 {g} _ {\ mathrm {m}, \ mathrm {MP} 2} {r} _ {\ mathrm {ds}, \ mathrm { MN} 2} -1} {1 + 2 {g} _ {\ mathrm {m}, \ mathrm {MP} 2} {r} _ {\ mathrm {ds}, \ mathrm {MN} 2}} {v } _ {\ mathrm {dd}} \ approx {v} _ {\ mathrm {dd}} $$ (20)Con la ayuda de la fuente de corriente autopolarizada propuesta, el nodo de salida de la parte del generador de corriente, B, puede rastrear la variación de pequeña señal del voltaje de suministro, lo cual es beneficioso para la mejora del PSRR de toda la referencia de voltaje.

Con un método similar, las ganancias de ruido de suministro de la ruta 5 y la ruta 6 pueden presentarse mediante las ecuaciones. (21) y (22), respectivamente:

$$ {Av} _ {\ mathrm {ruta} 5} ={g} _ {\ mathrm {m}, \ mathrm {MP} 3} \ left ({r} _ {\ mathrm {ds}, \ mathrm { MP} 3} \ Big \ Vert \ frac {1} {g _ {\ mathrm {m}, \ mathrm {MP} 4}} \ right) $$ (21) $$ {Av} _ {\ mathrm {ruta} 6} \ aproximadamente 1 $$ (22)Teniendo en cuenta la relación de conexión de la ruta de ruido del generador de referencia que se muestra en la Fig.2, el efecto del ruido de suministro a la tensión de referencia, V REF , se puede determinar mediante la ruta 5 y la ruta 6:

$$ {v} _ {\ mathrm {REF}} ={Av} _ {\ mathrm {ruta} 5} {V} _ {\ mathrm {B}} + {Av} _ {\ mathrm {ruta} 6} {v} _ {\ mathrm {dd}} =\ frac {1} {1+ {g} _ {\ mathrm {m}, \ mathrm {MP} 4} {r} _ {\ mathrm {ds}, \ mathrm {MP} 3}} {v} _ {\ mathrm {dd}} =\ frac {1} {1+ \ frac {\ exp \ left ({V} _ {\ mathrm {DS}, \ mathrm {MP } 3} / {V} _ {\ mathrm {T}} \ right) -1} {m}} {v} _ {\ mathrm {dd}} $$ (23)Para V DS > 4 V T , el término exponencial en la ecuación. (23) es muy grande. Esto hace que el rendimiento de PSRR se mejore enormemente con V DS, MP3 creciente. En el diseño propuesto, el mínimo V DS, MP3 es superior a 200 mV, lo que significa que el cambio en el voltaje de suministro tiene poco efecto en el V REF . Por lo tanto, la estructura propuesta tiene un buen rendimiento de PSRR.

Resultados y discusión

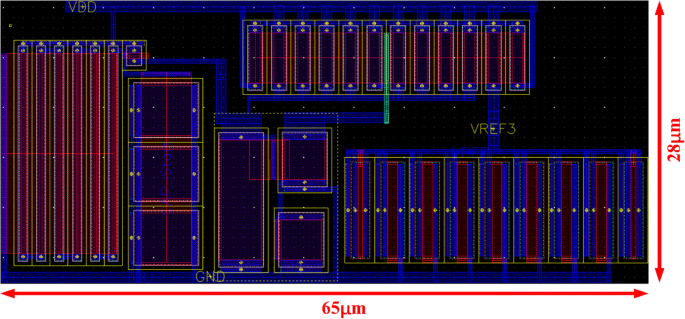

La referencia de voltaje se implementa en un proceso CMOS de 65 nm, cuyo diseño se muestra en la Fig.4 ocupando un 0,00182 mm 2 área activa.

Disposición del circuito propuesto

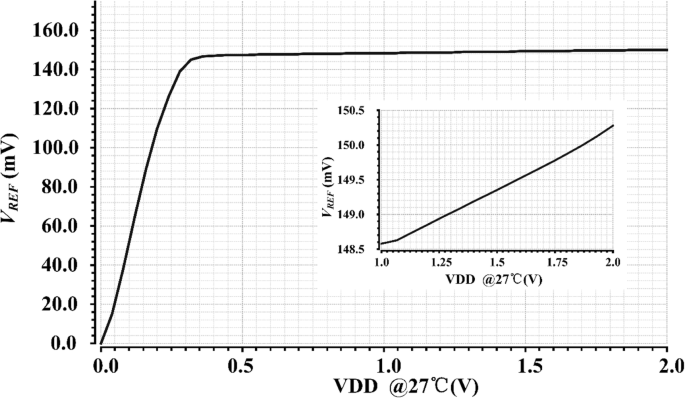

La Figura 5 muestra la regulación de línea de la referencia de voltaje propuesta a 27 ° C. Como se muestra en la Fig.5, el voltaje de suministro mínimo puede ser tan bajo como 350 mV y el voltaje de referencia generado, V REF , ronda los 148 mV . La sensibilidad de línea (LS) es 1.8 mV / V.

Forma de onda de V REF versus voltaje de suministro

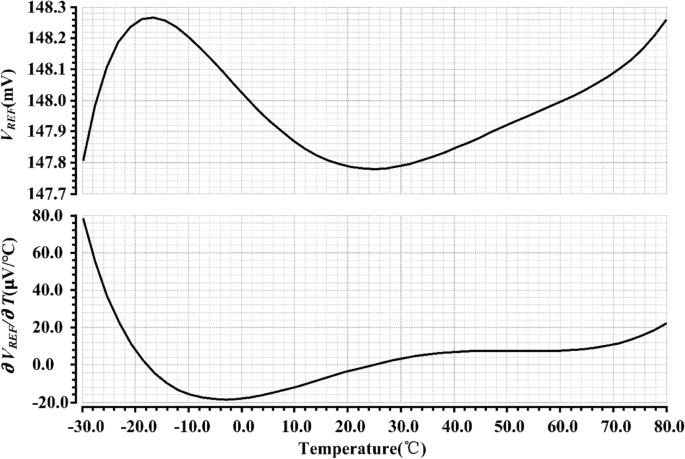

El rendimiento de temperatura de V REF con voltaje de alimentación de 350 mV se muestra en la Fig. 6. El TC de V REF es 28 ppm / ° C desde - 30 a 80 ° C. V REF muestra características de temperatura positivas por debajo de -15 ° C y por encima de 25 ° C, mientras que características de temperatura negativas en la región de temperatura media.

Dependencia de la temperatura de V REF

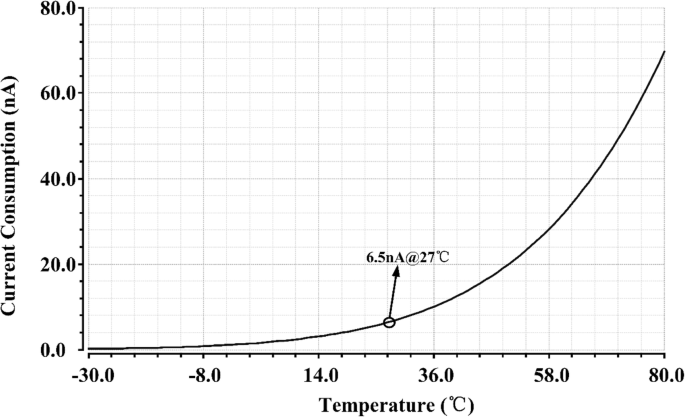

La Figura 7 muestra el consumo de corriente frente a la temperatura con una tensión de alimentación de 350 mV. La corriente muestra un TC positivo. El consumo de energía a temperatura ambiente es de alrededor de 2,28 nW.

Consumo actual frente a temperatura

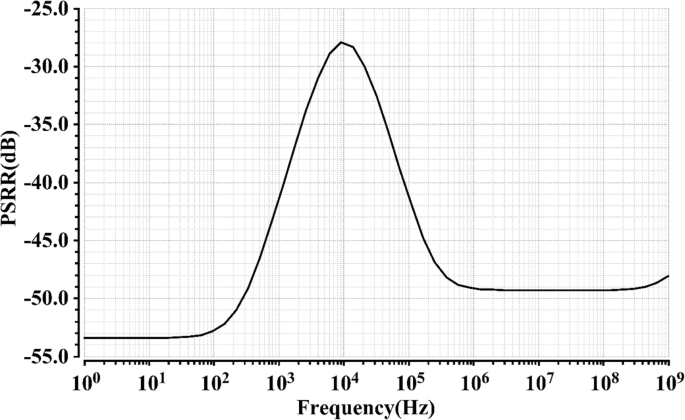

La Figura 8 muestra el resultado de PSRR a 27 ° C con voltaje de suministro de 350 mV, donde el PSRR sin ningún condensador de filtro de salida está por encima de 53 dB hasta 100 Hz. Como se mencionó anteriormente, el rendimiento del PSRR se puede mejorar aún más con un aumento del voltaje de suministro, lo que significa que el PSRR que se muestra en la Fig. 8 es el peor caso de la referencia de voltaje propuesta.

PSRR de la referencia de voltaje propuesta

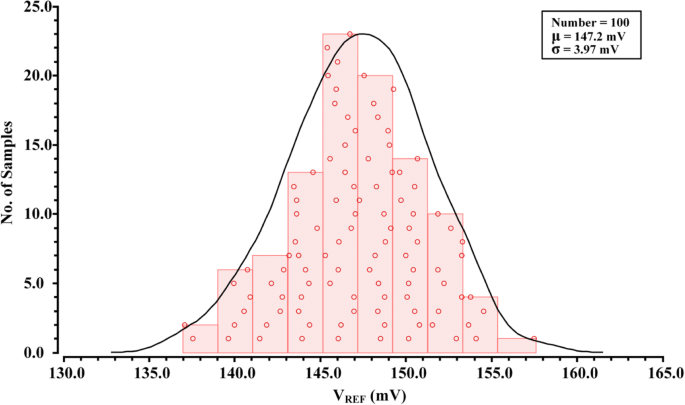

Las distribuciones de V sin recortar REF a 27 ° C con 100 muestras se muestra en la Fig. 9. El valor medio y la desviación estándar de V REF es de 147 mV y 3,97 mV, respectivamente, lo que da como resultado un margen (σ / μ) del 2,7%.

Distribuciones de V sin recortar REF

La Tabla 1 resume las características de la referencia de voltaje propuesta y la compara con algunas referencias de voltaje informadas anteriormente.

Conclusión

En este documento se presenta una referencia de voltaje de baja potencia sin resistencia con alto PSRR, que es adecuado para aplicaciones a nanoescala y puede extenderse a procesos más avanzados. Con la ayuda de una fuente de corriente autopolarizada basada en el divisor de voltaje MOSFET, el voltaje CTAT requerido, el voltaje PTAT y la suma ponderada se pueden realizar simultáneamente en una estructura compactada. Es más, se elige un voltaje de umbral delta como voltaje CTAT, que tiene un TC negativo muy reducido. Esto también hace que se reduzca el valor requerido de voltaje PTAT. Por lo tanto, se puede reducir la tensión de alimentación y el consumo de corriente. Todas las piezas solo están construidas por MOSFET, que tiene prioridad en aplicaciones altamente integradas sensibles a la energía, como SOC.

Abreviaturas

- BGR:

-

Referencia de bandgap

- CTAT:

-

Complementario a la temperatura absoluta

- hvt:

-

Voltaje de umbral alto

- LS:

-

Sensibilidad de línea

- mvt:

-

Voltaje de umbral medio

- PSRR:

-

Relación de rechazo de la fuente de alimentación

- PTAT:

-

Proporcional a la temperatura absoluta

- TC:

-

Coeficiente de temperatura

Nanomateriales

- Ohmímetros de alto voltaje

- Algunos ejemplos con circuitos de CA

- ST:regulador de conmutación con amplios rangos de voltaje

- Impresión 3D de alta velocidad con AFPM

- Impresión 3D de alta velocidad con AION500MK3

- Fabricación de pozos a nanoescala con alto rendimiento en película delgada de polímero utilizando litografía de arado dinámico basada en puntas AFM

- Convertidor de polarización con birrefringencia controlable basado en metauperficie híbrida de grafeno totalmente dieléctrico

- Célula solar híbrida de silicio nanoestructurado orgánico de alto rendimiento con estructura de superficie modificada

- Ge pMOSFET de alta movilidad con pasivación de Si amorfo:impacto de la orientación de la superficie

- Solución de problemas de fallas en la fuente de alimentación de alto voltaje

- Materiales y diseño de PCB para alta tensión