La importancia de la verificación de confiabilidad en los procesadores AI / ML

Con la adopción de la inteligencia artificial y el aprendizaje automático en una amplia variedad de aplicaciones, la verificación de la confiabilidad de los procesadores AI / ML es fundamental, ya que las fallas pueden tener consecuencias importantes para la validez y legitimidad de la tecnología AI / ML.

En los últimos años, ha habido una rápida expansión en la cantidad de empresas que implementan inteligencia artificial (IA) y aprendizaje automático (ML) en una amplia gama de aplicaciones. De hecho, los estudios muestran que 2019 fue un año récord para las empresas que adoptaron AI y ML, y que estas empresas consideran estas dos características como las más necesarias para lograr sus estrategias y objetivos comerciales. Esta creciente adopción se debe principalmente a la mejora en los algoritmos, los avances en el diseño de hardware y el aumento en el volumen de datos creado por la digitalización de la información.

Sin embargo, para respaldar y sostener el crecimiento de AI / ML, las empresas deben continuar demostrando al mercado que se puede confiar en los resultados que obtienen con las tecnologías de AI / ML. Esa confianza comienza con el diseño y la verificación de los circuitos integrados (CI) que subyacen a la funcionalidad AI / ML.

Clasificación de IA y ML

El procesamiento de IA se puede clasificar ampliamente en centro de datos / basado en la nube o integrado, dependiendo de si se realiza en un sitio de centro de datos / nube, o en el lado del usuario final (incorporando un chip de IA dedicado o un motor de coprocesador de IA con un sistema en chip (SOC) dentro de los dispositivos o en el borde). Edge en este contexto se refiere a un servidor local o una máquina que está más cerca del dispositivo que un centro de datos o una nube.

En términos de la aplicación de destino, un dispositivo de borde se puede clasificar en entrenamiento (ML) o inferencia. Históricamente, la parte de capacitación se realizaba en el sitio de la nube, y la parte de inferencia se manejaba en la nube o en el dispositivo de borde. Con el desarrollo de nuevas soluciones de computación en el borde de alto rendimiento, estamos siendo testigos de un cambio de paradigma a medida que se transfiere progresivamente más actividad de capacitación al lado del borde.

Diseño de chip AI / ML

Los chips AI / ML en soluciones de computación de borde o integrados dentro de dispositivos locales están diseñados para su uso en entornos específicos, como empresas, automotrices, industriales, de atención médica, Internet de las cosas (IoT), etc. Algunas de estas aplicaciones son de misión crítica, lo que significa cualquier falla puede tener consecuencias desastrosas en el mundo real. Por ejemplo, considere los sistemas avanzados de asistencia al conductor (ADAS) que se utilizan dentro de los automóviles. Si un procesador ADAS experimenta más de una latencia determinada mientras lee datos del sensor y hace una inferencia, puede causar una colisión.

Los circuitos integrados utilizados en aplicaciones AI / ML se caracterizan por grandes unidades de procesamiento en paralelo, alta disipación de potencia y circuitos complejos que pueden ofrecer el máximo rendimiento dentro de un estricto presupuesto de energía. Si bien algunas empresas emplean unidades de procesamiento central (CPU) tradicionales para tareas relacionadas con la IA, algunos expertos de la industria argumentan que el uso de CPU no es muy eficiente debido a la naturaleza distribuida de los algoritmos de IA de última generación. Estos algoritmos se adaptan bien a las soluciones de computación en paralelo, como las proporcionadas por las unidades de procesamiento de gráficos (GPU). Debido a su naturaleza reconfigurable, las matrices de puertas programables en campo (FPGA) también han atraído interés para su uso como aceleradores para chips de IA.

ASIC en aplicaciones AI / ML

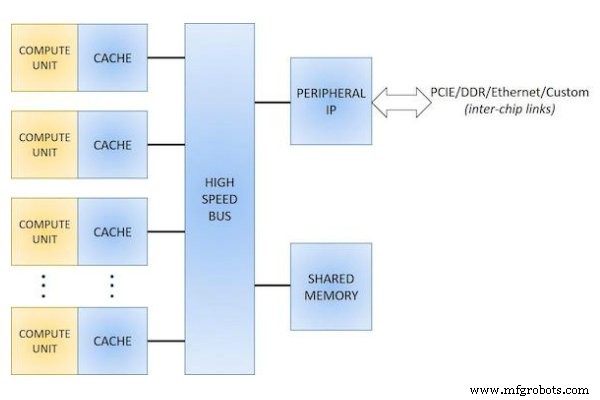

En general, existe un consenso cada vez mayor de que los complicados problemas de la inteligencia artificial y el aprendizaje automático no se prestan a una solución de diseño única para todos. Para combatir este problema, muchas empresas desarrollan sus propios CI específicos de la aplicación (ASIC), que optimizan junto con la pila de software para ofrecer el mejor valor para una aplicación de AI / ML determinada (Figura 1).

Figura 1. Diagrama de bloques para un diseño de chip ASIC AI.

Estas empresas reclaman varios beneficios del uso de estos ASIC, como un mejor rendimiento, más operaciones por ciclo, un diseño más simple y determinista en comparación con una CPU o GPU, ahorro de área (debido a la exclusión de construcciones y mecanismos complejos utilizados en una CPU), menor uso de energía y tiempo de desarrollo más rápido.

Computación heterogénea

También ha habido un aumento en el uso de computación heterogénea:sistemas que usan una combinación de diferentes tipos de núcleos de computación en un esfuerzo por combinar lo mejor de diferentes capacidades. Por ejemplo, en un sistema que usa una combinación de CPU y GPU, la computación heterogénea puede ser beneficiosa al descargar las tareas paralelas a la GPU, mientras que la CPU maneja tareas como el control de procesos, que es serial por naturaleza.

Un aspecto común entre las diferentes clases de procesadores de IA es que están optimizados para un alto rendimiento y baja latencia, y a menudo ofrecen multiplicadores de rendimiento de teraoperaciones por segundo (TOPS). Para obtener una ventaja en este mercado altamente competitivo, la eficiencia energética (medida por el rendimiento por vatio) se ha vuelto tan importante como el rendimiento bruto. La eficiencia energética a menudo se logra mediante el uso de una combinación de una o más técnicas de diseño, como la alimentación y el reloj, escalado dinámico de voltaje y frecuencia, diseños de múltiples Vt, etc.

Asegurar el diseño y la verificación confiables de estos circuitos integrados complejos es fundamental, ya que las fallas en los circuitos de estos chips pueden tener consecuencias importantes para la validez de la tecnología y la legitimidad de los resultados que brindan.

Verificación de confiabilidad de AI / ML IC

La verificación de la confiabilidad es un desafío enorme en los chips AI / ML, debido al tamaño y la complejidad de estos diseños, con recuentos de transistores del orden de millones, a veces incluso miles de millones. Por ejemplo, la GPU TESLA P100 de NVIDIA cuenta con una asombrosa cantidad de transistores de 15,3 mil millones, mientras que Loihi IC de Intel contiene 128 núcleos neuromórficos y 3 núcleos X-86, con 2,070 millones de transistores. Y, debido a que los requisitos de confiabilidad para cada entorno de uso son diferentes, los diseñadores deben comprender el conjunto de requisitos aplicables y asegurarse de que se cumplan probando sus diseños con especificaciones de requisitos de confiabilidad bien definidas.

Métodos de verificación de confiabilidad del diseño

Tradicionalmente, los diseñadores utilizaban una variedad de métodos para garantizar la confiabilidad del diseño, incluidas las técnicas de simulación e inspección manual, basándose principalmente en la experiencia y los conocimientos de su equipo de diseño. Sin embargo, la inspección manual no es un enfoque viable para estos chips AI / ML grandes y complejos, ya que requiere mucho tiempo y es propenso a errores humanos, y es prácticamente imposible proporcionar una cobertura suficiente. Los enfoques tradicionales de simulación tipo SPICE tampoco son prácticos para estos circuitos integrados, debido a su falta de escalabilidad para diseños grandes.

Para superar los problemas de capacidad y tiempo de ejecución, muchos equipos de diseño dividen manualmente un diseño y verifican diferentes bloques de propiedad intelectual (IP) de forma independiente mediante simulación o herramientas tradicionales. Sin embargo, hay muchas interacciones entre diferentes bloques de IP en un diseño (por ejemplo, entre diferentes núcleos de cómputo y el bus o enlace o memoria de gran ancho de banda), y las interacciones entre interfaces a menudo tienden a pasarse por alto durante un proceso de partición manual. Las herramientas tradicionales de verificación de circuitos integrados luchan con tiempos de ejecución excesivamente largos para verificar estos diseños complejos, lo que a menudo demora días en verificar diseños grandes y potencialmente retrasa el tiempo de comercialización.

Las deficiencias en cada uno de estos procesos resaltan la necesidad de una solución integral de automatización de diseño electrónico automatizado (EDA) que pueda aprovechar la potencia de cálculo de múltiples CPU y dispositivos simultáneamente. Con la verificación de confiabilidad calificada y automatizada, los equipos de diseño y verificación de productos pueden converger más rápidamente en la verificación y las correcciones de confiabilidad, lo que reduce su tiempo de respuesta general (TAT) de días a horas.

La plataforma de confiabilidad PERC de Calibre

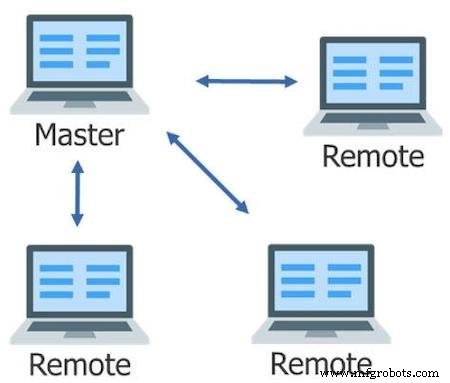

En los últimos años, ha surgido una nueva clase de herramientas de verificación de confiabilidad de CI que resuelven estos problemas de procesos. Herramientas como la plataforma de confiabilidad Caliber ™ PERC ™ aprovechan un amplio conjunto de características y funcionalidades para brindar una verificación de confiabilidad rápida y calificada para la fundición. Por ejemplo, la plataforma de confiabilidad Caliber PERC aprovecha el escalado multiproceso (MT) y multiproceso flexible (MTflex) de la plataforma Caliber, que distribuye las tareas a múltiples CPU y / o máquinas remotas para proporcionar una ejecución rápida y eficiente de los procesos de verificación. en chips grandes y complejos como CI AI / ML (Figura 2).

Figura 2. El escalado flexible de subprocesos múltiples distribuye las tareas a varios controles remotos para una ejecución general más rápida.

Más allá de estos mecanismos básicos pero esenciales, la plataforma de confiabilidad PERC de Caliber proporciona un procesamiento innovador que combina la lista de redes y la información de diseño de un diseño para evaluar de manera rápida y precisa una amplia gama de posibles problemas de confiabilidad. Al permitir que los diseñadores reduzcan de manera eficiente y segura la susceptibilidad de un diseño a fallas operativas y de rendimiento, este enfoque de verificación avanzada de confiabilidad ayuda a respaldar el crecimiento continuo y la adopción de tecnología confiable de AI / ML.

Fiabilidad a nivel de transistor

La mayoría de los diseños de ML / AI utilizan múltiples dominios de potencia para una variedad de propósitos, como proporcionar una fuente de alimentación limpia y sin ruido para IP analógica, lo que permite la capacidad de conectar o desconectar la energía a un área determinada de un chip, escalando voltajes hacia arriba o hacia abajo de forma independiente para IP seleccionadas, o satisfaciendo altas demandas de corriente utilizando múltiples reguladores de voltaje. Por ejemplo, el procesador Skylake de Intel contiene nueve dominios de energía primarios.

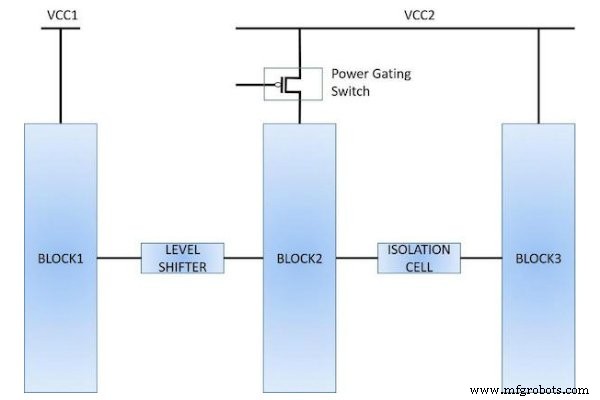

La implementación de un diseño de dominio de energía múltiple requiere el uso de elementos de circuito especiales, como reguladores de voltaje, interruptores de encabezado y pie de página, cambiadores de nivel, celdas de aislamiento y celdas de retención de estado. Estos elementos presentan un conjunto único de desafíos para la verificación de confiabilidad. Por ejemplo, los diseñadores deben verificar que se usen celdas de aislamiento o cambiadores de nivel apropiados en cada interfaz de dominio y que estén conectadas correctamente (Figura 3).

Figura 3. El uso de elementos especiales (como cambiadores de nivel, celdas de aislamiento e interruptores de puerta de potencia) dentro de un diseño de baja potencia requiere técnicas de verificación especializadas.

También deben asegurarse de que están utilizando los tipos adecuados de dispositivos en diferentes dominios de potencia, como dispositivos de óxido grueso para suministro de alto voltaje. Verificar estas condiciones requiere conocimientos y procesos muy específicos.

La técnica de formato de energía unificada

El formato de energía unificado (UPF) es una técnica ampliamente utilizada que permite a los diseñadores emplear una descripción coherente de la intención de energía a lo largo del flujo de diseño. Sin embargo, los flujos de verificación tradicionales basados en UPF se utilizan para validar IP a nivel lógico o de puerta, pero carecen de la capacidad para validar las implementaciones finales a nivel de transistor, en particular las conexiones de pozo y masivas.

La plataforma de confiabilidad Calibre PERC puede leer el archivo UPF para un diseño y aprovechar la información UPF para realizar varios análisis a nivel de transistor, como identificar cambiadores de nivel faltantes o conectados incorrectamente, condiciones de sobrecarga eléctrica (EOS), pozos flotantes y mucho más. . Al utilizar la plataforma de confiabilidad Caliber PERC junto con los datos de la UPF, los diseñadores pueden evaluar las interacciones de los dispositivos de manera programática para proporcionar una verificación de confiabilidad repetible y determinista.

Fiabilidad de por vida de chips AI / ML

La seguridad operativa es un aspecto crítico para la mayoría de los chips AI / ML, que se espera que funcionen a lo largo de su vida útil diseñada sin fallas o fallas. Es posible que algunos problemas de confiabilidad eléctrica, como la inestabilidad de la temperatura de polarización (BTI) y EOS, no se manifiesten como fallas inmediatas, pero pueden causar una rápida degradación y envejecimiento con el tiempo si no se corrigen antes de la fabricación. La verificación de confiabilidad puede ayudar a garantizar un funcionamiento sólido durante un período prolongado al verificar varios problemas, como resistencia de punto a punto, BTI positivo y negativo, densidad de corriente y electromigración (EM), todos los cuales pueden crear una degradación del rendimiento o fallas catastróficas.

Considere el caso en el que un dispositivo de dominio de alto voltaje está impulsando un dispositivo de óxido delgado que no está clasificado para manejar el alto voltaje. Durante el diseño, el diseñador no puede insertar una palanca de cambios de nivel alto-bajo. Aunque esta condición no necesariamente afectará la funcionalidad al principio, con el tiempo, tensionará el dispositivo de óxido delgado y eventualmente causará fallas. El tiempo de falla real depende del valor de voltaje, el tiempo en el que el suministro está ENCENDIDO o APAGADO y los parámetros del proceso.

EM (la migración de átomos en un conductor debido a la corriente eléctrica) es otro problema importante que afecta la solidez a largo plazo de las interconexiones utilizadas en los CI de AI / ML. Esta migración hace que se formen huecos y montículos en los cables. Los vacíos provocan un aumento significativo de la resistencia, mientras que los montículos pueden crear cortocircuitos, los cuales conducen a fallas en el circuito. El efecto EM depende de muchos factores, como la longitud y el ancho de la línea de metal, el material de interconexión, la temperatura de funcionamiento, las corrientes unidireccionales frente a las bidireccionales, etc.

Las fundiciones proporcionan a las empresas de diseño límites EM para la corriente máxima que pueden manejar los cables, según las condiciones de uso esperadas del producto. Por ejemplo, los límites de EM para un IC utilizado dentro de un teléfono móvil serían considerablemente más bajos que para un IC utilizado en un entorno industrial. Algunas empresas tienen equipos dedicados que se involucran activamente con la fundición para definir las especificaciones apropiadas, crear estructuras de prueba y realizar la calificación del producto para la tolerancia EM. Obviamente, es más difícil definir estos límites para un producto que podría usarse en múltiples entornos, por lo que los diseñadores suelen diseñar estos chips para las peores condiciones operativas. En todos los casos, es crucial probar el diseño contra los límites EM definidos por la fundición y validar que el diseño puede resistir los efectos EM.

No detectar y corregir los diferentes problemas de confiabilidad durante la fase de verificación previa al silicio puede resultar en una amplia gama de impactos, incluidos múltiples giros de cinta, retrasos en la comercialización del producto, pérdida de la confianza del cliente, reacción negativa significativa del mercado, productos retirados del mercado e incluso consecuencias catastróficas, como lesiones físicas o la muerte. La identificación y reparación de las violaciones de confiabilidad antes de la eliminación de la cinta minimiza la posibilidad de que los circuitos funcionen incorrectamente o fallas que pueden resultar costosas.

El análisis y la gestión de la confiabilidad de AI / ML son cruciales

El éxito reciente y la expansión de la funcionalidad AI / ML se basan en gran medida en los avances en la tecnología de semiconductores. A medida que se desarrollan estos nuevos diseños, la comunidad de diseño de hardware debe ser consciente de la necesidad de analizar y gestionar los aspectos de confiabilidad de un diseño, como el entorno objetivo, las condiciones de operación, los criterios de confiabilidad, etc. Potentes herramientas de verificación de confiabilidad de EDA diseñadas para abordar Los problemas y requisitos de confiabilidad específicos de estos chips grandes y complejos pueden ayudar a las casas de diseño a garantizar que sus productos funcionen según lo previsto a lo largo de su vida útil diseñada. A su vez, eso se traduce en confianza en los resultados logrados mediante el uso de aplicaciones de IA / ML en los mercados más amplios, lo que respalda su uso y expansión continuos.

Los artículos de la industria son una forma de contenido que permite a los socios de la industria compartir noticias, mensajes y tecnología útiles con los lectores de All About Circuits de una manera que el contenido editorial no es adecuado. Todos los artículos de la industria están sujetos a estrictas pautas editoriales con la intención de ofrecer a los lectores noticias útiles, experiencia técnica o historias. Los puntos de vista y las opiniones expresados en los artículos de la industria son los del socio y no necesariamente los de All About Circuits o sus redactores.

Tecnología de Internet de las cosas

- La importancia de la seguridad eléctrica

- ¿Cuál es la función del ingeniero de confiabilidad?

- La clave n. ° 1 para el éxito de la confiabilidad

- La importancia de las competencias básicas

- El lado no técnico de la confiabilidad

- La importancia de las tendencias en la confiabilidad de los motores eléctricos

- La importancia del mantenimiento de rutina en el equipo

- La importancia del mecanizado rápido en la fabricación

- La importancia del análisis de causa raíz

- La importancia de la planificación de contingencias

- La importancia del agua