Las soluciones CXL 2.0 / PCIe 5.0 desbloquean cuellos de botella heterogéneos de cómputo y datos

La startup de semiconductores sin fábrica Astera Labs ha anunciado nuevas soluciones de conectividad CXL 2.0 y PCIe 5.0 especialmente diseñadas para desbloquear arquitecturas informáticas heterogéneas y abordar cargas de trabajo sensibles a la latencia en el centro de datos. La compañía dijo que el objetivo de estas nuevas soluciones es abordar los cuellos de botella de rendimiento de todo el sistema en aplicaciones centradas en datos.

La proliferación de datos y la integración de cargas de trabajo especializadas, como la inteligencia artificial (IA) y el aprendizaje automático (ML), requieren aceleradores especialmente diseñados para trabajar en paralelo con CPU de uso general en la misma placa base o dentro del mismo rack mientras compartiendo un espacio de memoria común. La interconexión CXL 2.0 es clave para habilitar tales topologías de sistema coherentes en caché.

El primer producto del nuevo portafolio de Astera Labs es su portafolio de retimer inteligente Aries Compute Express Link (CXL 2.0) (PT5161LX, PT5081LX) para conectividad CXL.io de baja latencia, que se está probando activamente para clientes estratégicos. El director ejecutivo de la empresa, Jitendra Mohan, dijo:"Con nuestra expansión en el ecosistema CXL, Astera Labs está dando otro gran paso para proporcionar soluciones diseñadas específicamente que desbloquean topologías de sistemas de desagregación componibles y computación heterogénea compleja".

La especificación CXL 2.0 fue lanzada por el Consorcio CXL en noviembre de 2020. CXL es una interconexión estándar de la industria abierta que ofrece coherencia y semántica de memoria que utiliza conectividad de alto ancho de banda y baja latencia entre el procesador host y dispositivos como aceleradores, búferes de memoria y dispositivos inteligentes. Dispositivos de E / S. La especificación CXL 2.0 agrega soporte para la conmutación de distribución en abanico para conectarse a más dispositivos; agrupación de memoria para aumentar la eficiencia en el uso de la memoria y proporcionar capacidad de memoria a pedido; y soporte para la memoria persistente. Todo esto al mismo tiempo que se preservan las inversiones de la industria al admitir la compatibilidad total con versiones anteriores de CXL 1.1 y 1.0.

El presidente del Consorcio CXL, Barry McAuliffe, dijo:“Como miembro temprano del Consorcio CXL, Astera Labs contribuyó con su experiencia en conectividad al avance del estándar CXL. Es fantástico ver que su primera implementación de silicio CXL llega al mercado en apoyo de un ecosistema CXL de rápido crecimiento ”.

Nuevas soluciones PCIe 5.0 en colaboración con Intel

Astera Labs también anunció la disponibilidad de un nuevo modo de baja latencia en su cartera de retimer inteligente Aries para conectividad PCIe con procesadores escalables Intel Xeon. Este desarrollo fue el resultado de una estrecha colaboración con Intel Corporation para reducir aún más la latencia en los enlaces PCIe a sub-10ns y mejorar el rendimiento en cargas de trabajo centradas en datos. Astera Labs afirmó que es el primer proveedor en demostrar una sólida interoperabilidad PCIe 5.0 con procesadores escalables Intel Xeon con nombre en código "Sapphire Rapids".

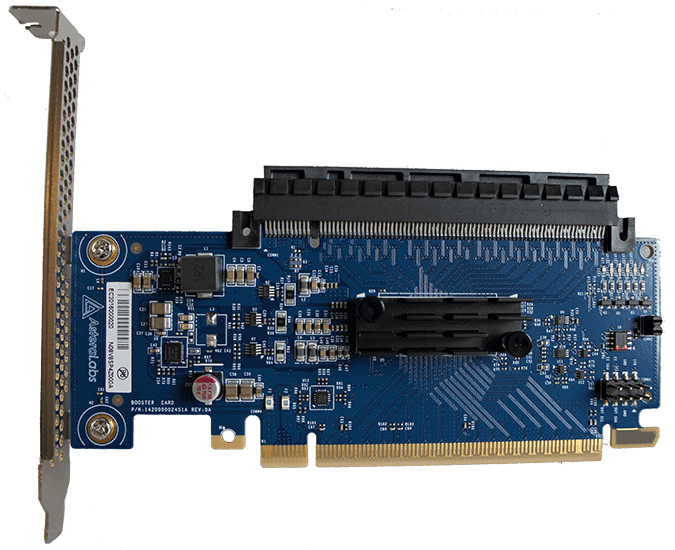

También se lanzó al mismo tiempo una nueva tarjeta adicional plug-and-play Smart retimer para aplicaciones PCIe / CXL, llamada Equinox. También desarrollada en asociación con Intel, la tarjeta y el firmware asociado especialmente diseñado simplificarán el desarrollo de sistemas habilitados para PCIe 5.0 con los últimos procesadores escalables Xeon de Intel. Esto representa la transición de Astera Labs para ofrecer placas plug-and-play fáciles de usar para implementar rápidamente topologías de sistema complejas.

“PCIe Gen5 y CXL son tecnologías fundamentales para cargas de trabajo informáticas heterogéneas y arquitecturas de centros de datos hoy y mañana”, dijo Zane Ball, vicepresidente corporativo y gerente general de ingeniería y arquitectura de centros de datos en Intel. "Intel está colaborando con líderes de ecosistemas como Astera Labs para reducir significativamente la latencia de interconexión PCIe y CXL en la próxima plataforma escalable Intel Xeon con nombre en código 'Sapphire Rapids' y plataformas adicionales".

Contenidos relacionados:

- Reprogramación de USB4 a través de USB-C

- Construyendo interconexiones de alto rendimiento con múltiples generaciones de PCIe

- Xilinx apunta a la descarga del centro de datos con hardware "componible"

- Cómo la supercomputación perimetral transformará el gran diluvio de datos

Incrustado

- Problemas legales en la computación en la nube y sus soluciones

- DATA MODUL:soluciones de señalización digital orientadas al cliente en exhibición en ISE

- Microchip:los búferes de reloj cumplen con los estándares DB2000Q / QL más las especificaciones de baja fluctuación de fase de PCIe Gen 4 y 5

- Apacer:SSD PCIe NVMe Gen3, el siguiente paso lógico para el almacenamiento de nivel industrial

- Swissbit:soluciones de seguridad basadas en hardware para proteger datos y dispositivos

- TECHWAY:plataforma Kintex-7 FPGA PCIe para aumentar el rendimiento de la velocidad de datos con 12 enlaces HSS

- Estrategia y soluciones del ejército para el mantenimiento basado en condiciones

- Los beneficios de adaptar IIoT y soluciones de análisis de datos para EHS

- Combatiendo inundaciones en áreas urbanas con soluciones de red de IoT

- Cómo Internet de las cosas está transformando la cadena de suministro:Parte 2, Soluciones futuras

- El diseño electrónico está utilizando soluciones habilitadas por IA para brindar un servicio de primer nivel