El procesador cruzado de bajo costo admite la inferencia de puntos finales

BRISTOL, Reino Unido - XMOS ha adaptado su núcleo de procesador Xcore para el aprendizaje automático, creando un procesador cruzado para aplicaciones AIoT. El Xcore.ai estará disponible desde $ 1.

Xcore.ai, la tercera generación de productos basados en el diseño central patentado de la empresa, está diseñado para la inferencia de IA en tiempo real y la toma de decisiones en dispositivos de punto final, y también puede manejar funciones de procesamiento, control y comunicaciones de señales.

Una novedad en este chip de tercera generación es una capacidad de canalización vectorial para aplicaciones de aprendizaje automático. Es el único procesador cruzado de su tipo que admite redes neuronales binarizadas (1 bit), que están adquiriendo una importancia cada vez mayor para la IA de potencia ultrabaja en las aplicaciones de punto final, ya que ofrecen una mejora de orden de magnitud en el rendimiento y la densidad de memoria negociada. para una reducción modesta en la precisión (el Xcore.ai también admite números de 32 bits, 16 bits y 8 bits).

El Xcore.ai se une a una nueva clase de sistema con capacidad de inteligencia artificial en chips para aplicaciones de punto final, el procesador cruzado (Imagen:XMOS)

Xcore.ai se une a una clase emergente de procesador de punto final con capacidad de inteligencia artificial, el procesador cruzado. Acuñado por NXP, este término describe una nueva categoría importante de dispositivos con el rendimiento de un procesador de aplicaciones combinado con la facilidad de uso, el bajo consumo de energía y el funcionamiento en tiempo real de un microcontrolador.

“Si habla con los clientes sobre 'microcontroladores', ellos piensan en los dispositivos Cortex-M0, M3 o M4 que cuestan 75 centavos o menos, con un rendimiento relativamente bajo, cien MIPS más o menos. Entonces, los "SoC" podrían ser algo con núcleos cuádruples A53, que se ejecutan en un gigahercio. Hay una gran brecha entre los elementos intermedios, como los procesadores de voz, que es un problema matemático particularmente difícil que requiere miles de MIPS. Así que existe una gran brecha con un área de aplicación realmente grande e importante ubicada justo en el medio, y merece un nombre ", dijo Mark Lippett, CEO de XMOS, en una entrevista exclusiva con EETimes.

Interfaces de voz

El producto de segunda generación previamente anunciado por la compañía, el XVF3510, se lanzó en julio de 2019 como un ASIC para interfaces de voz, pero bajo el capó, el silicio también se basa en el diseño Xcore patentado de la compañía, enviado con firmware. Los diseños de referencia para soluciones de voz de campo lejano basadas en el XVF3510 están calificados para el servicio de voz Alexa de Amazon.

Dado el historial de XMOS en el sector de la voz, no es de extrañar que el chip Xcore.ai se dirija inicialmente a aplicaciones de interfaz de voz que requieren inteligencia artificial para la detección de palabras clave o funciones de diccionario.

“Seamos absolutamente claros, la voz es la carga de trabajo de IA más importante en el punto final y probablemente lo seguirá siendo durante bastante tiempo. Pero para mejorar las interfaces de voz, encontrará que los dispositivos se volverán más multimodales ”, dijo Lippett, describiendo una tendencia para usar diferentes tipos de sensores para hacer que las aplicaciones sean más sensibles al contexto, ya sea detectando la presencia de una persona o detectando dónde. están hablando desde.

Mark Lippett (Imagen:XMOS)

"Hay muchas oportunidades para mejorar la experiencia del usuario no solo escuchando audio, sino haciendo más que eso", dijo.

Muchas aplicaciones de inteligencia artificial en dispositivos de IoT dependen de una combinación de privacidad, seguridad y protección que requiere que el procesamiento se realice en el punto final. Lippett describió las características de seguridad en los electrodomésticos que usan voz y radar para apagar el horno si solo hay niños presentes en la cocina, por ejemplo.

Por lo tanto, Xcore.ai saldrá al mercado con bibliotecas para la creación de interfaces de voz, pero Lippett dijo que tiene capacidad de sobra para que los clientes construyan sus propios sistemas. Se incluye una interfaz MIPI para la entrada de la cámara.

Arquitectura Xcore

El chip Xcore.ai ofrece hasta 3200 MIPS, 51,2 GMACC y 1600 MFLOPS. Tiene 1 Mbyte de SRAM integrado más una interfaz DDR de bajo consumo para expansión.

En comparación con un dispositivo Cortex-M7 que proporciona aproximadamente el mismo nivel de integración que Xcore.ai, funcionando a una frecuencia operativa similar, las propias cifras de XMOS ponen su parte en 32 veces el rendimiento de procesamiento de AI y 15 veces el rendimiento de DSP.

"En el mundo de los terminales, tiene que ser precio-rendimiento, no tiene sentido hablar de uno sin el otro", dijo Lippett. “Hemos sido muy agresivos con el precio, podemos bajar a $ 1 por esta parte [en volumen]. En términos generales, somos aproximadamente la mitad del costo [del dispositivo Cortex-M7 comparable] y lo estamos superando en términos de rendimiento ".

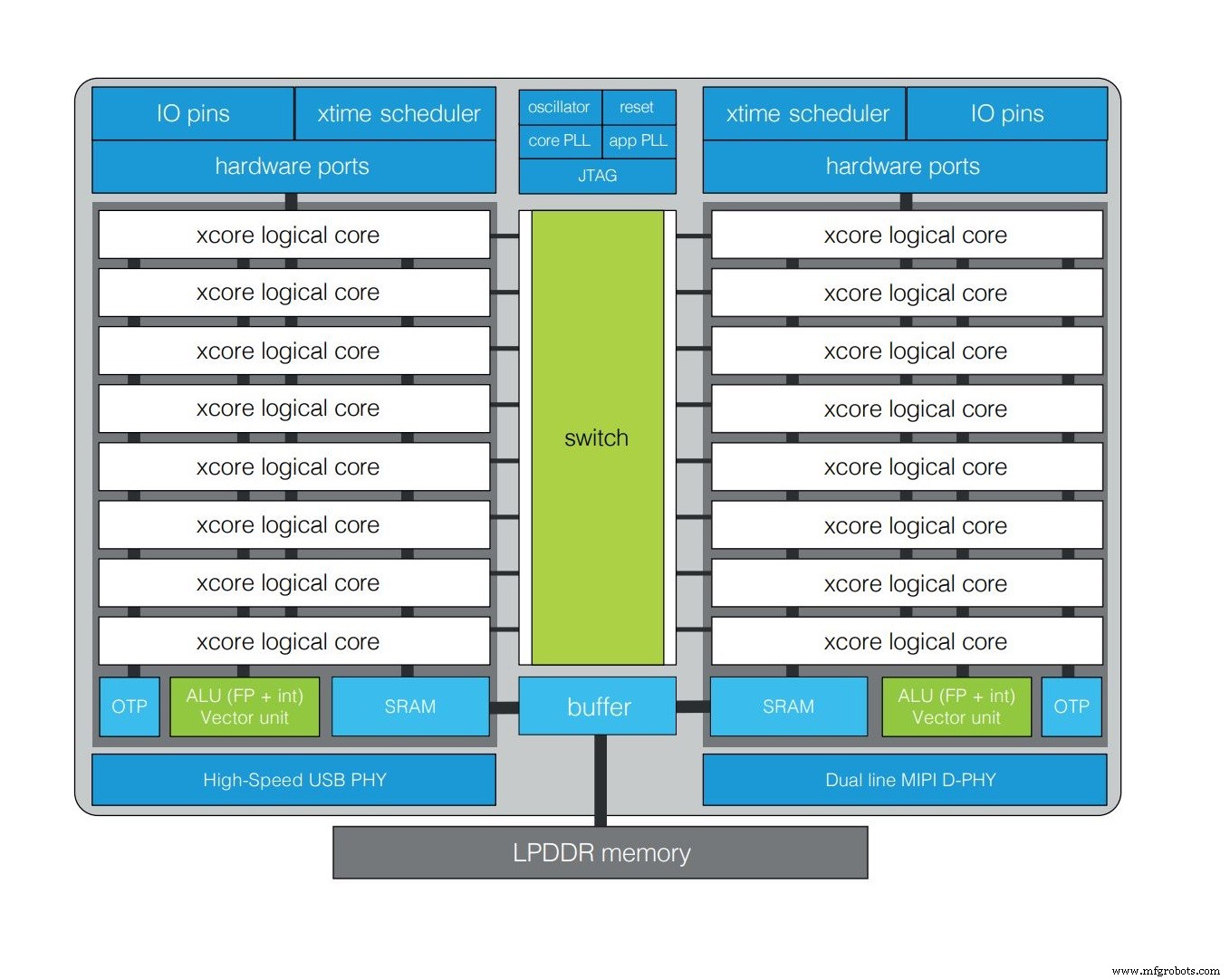

El Xcore se basa en núcleos lógicos dispuestos en mosaicos con memoria,

ALU y unidades vectoriales (Imagen:XMOS)

Xcore.ai se basa en la arquitectura Xcore patentada de XMOS. El Xcore en sí está construido sobre bloques de construcción llamados núcleos lógicos, que se pueden usar para E / S, DSP, funciones de control o aceleración de IA. Hay ocho núcleos lógicos en cada mosaico, con dos mosaicos en cada chip Xcore.ai, y los diseñadores pueden elegir cuántos núcleos asignar a cada función. Cada mosaico también contiene memoria, ALU y una unidad vectorial a la que los núcleos lógicos comparten acceso.

“Fundamentalmente, [comparten el acceso] de una manera muy predecible”, dijo Lippett. “Esto es lo que tiene de especial el Xcore. Inicialmente, queríamos ofrecer flexibilidad de E / S a los ingenieros de software, y el hardware no es muy tolerante si no cumple con los plazos. Entonces, el Xcore es de múltiples núcleos, no porque queramos agrupar cargas de trabajo y hacer las cosas muy rápido, podemos hacerlo, pero en realidad es de múltiples núcleos porque queremos darles a partes particulares de la aplicación sus propios recursos, de modo que cuando es necesario, está listo. Está diseñado de abajo hacia arriba para ofrecer ese tipo de precisión de sincronización ".

La asignación de diferentes funciones (E / S, DSP, control, AI) a los núcleos lógicos en el firmware permite la creación de un "SoC virtual", completamente escrito en software. En el siguiente ejemplo, un núcleo está realizando tareas que normalmente se realizarían en hardware, como I 2 S, yo 2 C y controladores LED, y algunos núcleos procesan la red neuronal, mientras que otros realizan tareas que normalmente se realizarían en software. Definir todo esto en software es más rápido, para adaptarse a las demandas transitorias de los dispositivos de IoT. El desarrollo también es más barato, dijo Lippett, lo que permite a las empresas crear soluciones que son económicas incluso en segmentos de mercado más pequeños.

Una aplicación de ejemplo asignada a un dispositivo Xcore.ai (Imagen:XMOS)

“La forma en que vemos la evolución del mercado es que el mercado exige características más diversas y las empresas deberán responder más rápidamente”, dijo Lippett. “Es muy difícil hacer una apuesta de dos años en el IoT sin construir una plataforma muy genérica que podría no ser [eventualmente] lo suficientemente buena para ningún segmento. [Con Xcore.ai], es mucho más fácil llevar los dispositivos al mercado mucho más rápido, con menos gastos de capital, y hacer apuestas más pequeñas de manera efectiva en mercados más pequeños y hacer que esos mercados sean económicos ".

¿Cómo competirá XMOS contra los grandes fabricantes de microcontroladores que se trasladen a este espacio de procesadores cruzados?

“¡No construyendo SoC basados en ARM! Porque lo hacen muy bien ”, dijo Lippett. “La única forma de competir contra esos tipos es tener una ventaja arquitectónica. Se trata de las capacidades intrínsecas del Xcore en términos de rendimiento, pero también de flexibilidad ".

Incrustado

- Renesas destaca la inteligencia de endpoints en el mundo embebido 2019

- Las MCU apuntan a diseños de extremos y bordes de IoT seguros

- Los módulos de procesador inalámbrico precertificados cuentan con conectividad de malla Bluetooth

- El uso de varios chips de inferencia requiere una planificación cuidadosa

- PMIC simplifica los diseños de procesadores de múltiples carriles

- Tiny háptico IC admite dispositivos portátiles de bajo consumo

- El procesador multinúcleo integra la unidad de procesamiento neuronal

- El radar en chip de 60 GHz admite los requisitos de la industria automotriz

- El IC de administración de energía es compatible con la familia de procesadores de aplicaciones

- Los procesadores especializados aceleran las cargas de trabajo de AI de punto final

- Se estrena el procesador de radar de imágenes automotrices de 30 fps