Cómo crear una declaración concurrente en VHDL

Una declaración concurrente en VHDL es una asignación de señal dentro de la arquitectura, pero fuera de una construcción de proceso normal. La instrucción concurrente también se conoce como asignación concurrente o proceso concurrente.

Cuando crea una declaración concurrente, en realidad está creando un proceso con ciertas características claramente definidas. Las declaraciones concurrentes siempre son equivalentes a un proceso que usa una lista de sensibilidad, donde todas las señales a la derecha del operador de asignación de señal están en la lista de sensibilidad.

Estos procesos de notación abreviada son útiles cuando desea crear una lógica simple que resulte en la asignación de una sola señal. En lugar de escribir una construcción de proceso completa con listas de sensibilidad y todo eso, simplemente puede asignar la señal de destino directamente en la arquitectura.

Esta publicación de blog es parte de la serie Tutoriales básicos de VHDL.

Cuando se usa correctamente, la intención del código seguirá siendo bastante clara. No es necesario crear un proceso para cada bit que desee voltear.

Ejercicio

En este video, aprendemos cómo crear una declaración concurrente:

El código final que creamos en este tutorial:

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T13_ConcurrentProcsTb is

end entity;

architecture sim of T13_ConcurrentProcsTb is

signal Uns : unsigned(5 downto 0) := (others => '0');

signal Mul1 : unsigned(7 downto 0);

signal Mul2 : unsigned(7 downto 0);

signal Mul3 : unsigned(7 downto 0);

begin

process is

begin

Uns <= Uns + 1;

wait for 10 ns;

end process;

-- Process multiplying Uns by 4

process is

begin

Mul1 <= Uns & "00";

wait on Uns;

end process;

-- Equivalent process using sensitivity list

process(Uns) is

begin

Mul2 <= Uns & "00";

end process;

-- Equivalent process using a concurrent statement

Mul3 <= Uns & "00";

end architecture;

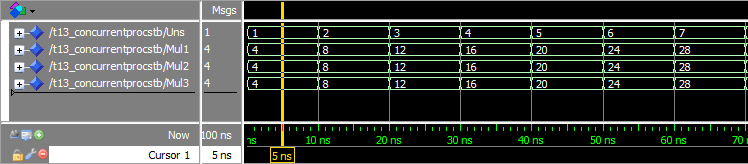

La ventana de forma de onda en ModelSim después de presionar Ejecutar y hacer zoom en la línea de tiempo:

Análisis

Podemos ver en la forma de onda que Mul1 , Mul2 y Mul3 comportarse exactamente igual. Esto se debe a que la instrucción concurrente y los dos procesos que creamos son equivalentes.

Una declaración concurrente funciona como un proceso. Todas las señales a la derecha del <= se agregan automáticamente a la lista de sensibilidad. Esto significa que la señal a la izquierda del <= se actualizará cada vez que cambie una de las señales que se evalúan.

Hay muchas formas de multiplicar números en VHDL. En este ejercicio multiplicamos el Uns señal por 4, usando bit shifting. Todas nuestras señales son de unsigned tipo, lo que significa que se interpretan mediante números. Agregar un 0 a la derecha de un número binario es lo mismo que multiplicarlo por 2.

Esta es una ilustración de lo que sucede en el cursor en la forma de onda:

Para llevar

- Una declaración concurrente es una asignación de señal directamente en la región de la arquitectura

- Las declaraciones concurrentes son equivalentes a un proceso con todas las señales evaluadas en la lista de sensibilidad

Ir al siguiente tutorial »

VHDL

- Declaración de procedimiento:ejemplo de VHDL

- Cómo crear una lista de cadenas en VHDL

- Cómo crear un banco de pruebas controlado por Tcl para un módulo de bloqueo de código VHDL

- Cómo detener la simulación en un banco de pruebas VHDL

- Cómo crear un controlador PWM en VHDL

- Cómo crear un FIFO de búfer de anillo en VHDL

- Cómo crear un banco de pruebas de autocomprobación

- Cómo crear una lista enlazada en VHDL

- Cómo usar un procedimiento en un proceso en VHDL

- Cómo usar una función impura en VHDL

- Cómo usar una función en VHDL