Procesamiento isométrico diferencial y verificación de simulación del diseño de PCB de alta velocidad

Influencia del retraso relativo en las señales

Las señales transmitidas en líneas de señal diferencial contienen un componente de modo diferencial y un componente de modo común de las señales.

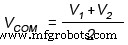

La cantidad de señales diferenciales se refiere a la diferencia entre dos señales siguiendo la fórmula Vdiff =V1 - V2 . La cantidad de señales de modo común se refiere a la mitad de la suma de dos señales siguiendo la fórmula  . Por lo tanto, el cambio de voltaje de una sola línea conduce definitivamente a la influencia simultánea en las señales de modo diferencial y las señales de modo común. A continuación, se aplica el software gráfico para dibujar el diagrama de función matemática para estudiar respectivamente la influencia en las señales de modo diferencial y las señales de modo común. Para facilitar la investigación, las señales pueden analizarse simulándolas en forma de onda trapezoidal con el mismo tiempo superior e inactivo.

. Por lo tanto, el cambio de voltaje de una sola línea conduce definitivamente a la influencia simultánea en las señales de modo diferencial y las señales de modo común. A continuación, se aplica el software gráfico para dibujar el diagrama de función matemática para estudiar respectivamente la influencia en las señales de modo diferencial y las señales de modo común. Para facilitar la investigación, las señales pueden analizarse simulándolas en forma de onda trapezoidal con el mismo tiempo superior e inactivo.

• Influencia en las señales diferenciales

La señal de terminal de fase positiva, la señal de terminal de fase negativa y la señal diferencial de los pares de líneas diferenciales se muestran en la Figura 1 a continuación, en la que la línea completa representa la onda de señal diferencial.

Si se lleva a cabo una colocación de fase desde el terminal de fase positiva al terminal de fase negativa, habrá un cambio de diferencia entre la señal del terminal de fase positiva y la señal del terminal de fase negativa en el borde superior o inferior y este cambio cambiará con el cambio de fase. Tr se utiliza para representar el tiempo más corto entre el tiempo ascendente y el descendente. Se puede indicar que cuando la colocación de fase es menor que el punto dos de Tr , la distorsión de la señal es relativamente pequeña y el aumento de la ubicación de la fase conduce a una fuerte distorsión de la forma de onda diferencial. Cuando la ubicación de la fase excede Tr , el área no monótona tendrá lugar en la forma de onda. Aquí el área no monótona es una línea recta. Sin embargo, para señales prácticas, debido a los reflejos, pueden tener lugar grandes subidas y bajadas en áreas no monótonas con pulsos de interferencia formados que conducen a disparos falsos, que deben evitarse. Además, el borde superior de la forma de onda diferencial se vuelve lento con el aumento de la ubicación de la fase, lo que puede generar un tiempo de establecimiento insuficiente para la señal de datos y un tiempo de retención insuficiente para la señal del reloj.

• Influencia en la señal de modo común

La ubicación de la fase de la señal de un solo terminal no tendrá influencia en la forma de onda diferencial, pero cambiará la forma de onda de las señales de modo común. Cuando la colocación de fase se lleva a cabo en la señal del terminal positivo, el cambio de onda se llevará a cabo a señales de modo común. Se puede indicar que el rango de fluctuación está relacionado con la cantidad de colocación de fase. Cuando la cantidad de colocación de fase es respectivamente 0.05Tr , 0.1Tr , 0.2Tr y 0.5Tr , el rango de fluctuación del modo común es respectivamente 5%, 10%, 20% y 50% del rango de fluctuación original. Cuando la fase aumenta a Tr o más, la fluctuación aumentará hasta aproximadamente el 100 %, que es el rango de fluctuación más alto. El cambio de la señal de modo común puede provocar un problema de EMI y, dado que la señal de código común no se recibe en el terminal en muchas condiciones, se formará una reflexión en el terminal receptor, lo que provocará un timbre de señal. Por lo tanto, el rango de fluctuación de la señal de modo común debe reducirse tanto como sea posible.

En conclusión, un retardo relativo demasiado grande entre los pares diferenciales puede provocar una activación falsa de las señales, reflejo de la señal, EMI y problemas de secuenciación en el tiempo. Sin embargo, el grado de influencia de la señal de retardo relativo depende del factor de escala compatible con la señal Tr . Cuando el factor de escala es 0,05, la distorsión de las señales diferenciales casi se puede ignorar. Sin embargo, para las señales de modo común, cuando el factor de escala es 0,05, la fluctuación de voltaje de las señales de modo común se puede controlar en aproximadamente un 5 %. Entonces, incluso en la situación de reflexión total, el voltaje de reflexión acumulado en las líneas de señal es solo el 10 % de la fluctuación original, que suele ser un valor aceptable. Por lo tanto, en el proceso de diseño de PCB de alta velocidad, el retraso relativo de la línea de señal diferencial en las reglas de regulación de enrutamiento se puede establecer en 0,05 Tr que es capaz de cumplir con el requisito de integridad de la señal.

Determinación de la categoría de retraso relativo

Con base en el análisis anterior, la clave para la determinación de la categoría isométrica diferencial, es decir, la determinación del retraso relativo de los pares diferenciales, radica en la determinación de Tr refiriéndose al valor más pequeño entre el tiempo superior e inferior de las señales diferenciales. La salida del tiempo de subida y el tiempo de caída es en realidad la salida de la combinación de impedancia y capacitancia. Por lo tanto, el tiempo de subida/bajada sin carga es en realidad un tiempo de subida/bajada inherente.

Los tres métodos siguientes se pueden aplicar para obtener el valor de Tr :

• El tiempo de subida/bajada se puede obtener directamente de los manuales de los componentes. Sin embargo, en la mayoría de las situaciones, este parámetro no se proporciona.

• Valor de Tr se puede obtener de las palabras clave Ramp del modelo IBIS (Especificación informativa del búfer de entrada/salida) del componente. Los parámetros de tiempo de subida/bajada bajo las palabras clave Ramp generalmente se miden en el puerto de salida conectado con una resistencia de 50 Ω, que generalmente es del 20% al 80% del tiempo de voltaje final. Dado que los parámetros se obtienen sin considerar la influencia del paquete, es estricto para nosotros usar el tiempo de subida/bajada como el valor de Tr .

• El valor de Tr se puede estimar de acuerdo con la frecuencia de reloj mínima o la frecuencia de reloj máxima de las señales de salida. Debido a que el flanco de subida distributivo es aproximadamente el 10 % de la frecuencia de reloj en la mayoría de los sistemas digitales de alta velocidad, el valor de Tr se puede estimar con el período de reloj mínimo Tclk proporcionado según la fórmula:Tr =Tclk x 10%.

El valor estimado obtenido a través del período del reloj suele ser estricto porque los parámetros parásitos del paquete o la carga de los componentes harán que el tiempo de subida/bajada inherente en los transistores sea muy lento.

En el trabajo práctico, en la mayoría de las situaciones, los diseñadores de circuitos no proporcionan información de Tr a los ingenieros de diseño de PCB que solo reciben algunas demandas ambiguas en términos de control isométrico diferencial. El tercer método, sin duda, proporciona un esquema simple para los ingenieros de diseño de PCB siempre que se obtenga la frecuencia de reloj más alta en la línea de señal. La frecuencia de reloj más alta se considera el parámetro de diseño más confiable para los diseñadores de circuitos y, por lo general, se proporciona a los ingenieros de diseño de PCB al comienzo del diseño de PCB.

El tercer método generalmente conduce a una lista de valores de referencia dentro de la categoría de control de retardo relativo entre pares diferenciales, como se muestra en la siguiente tabla.

| Frecuencia de reloj/ns | Frecuencia de reloj/MHz | Categoría de retraso relativo/ps | Longitud de la línea de transmisión/mil |

| 3.75 | 266 | 18.8 | 105 |

| 3 | 333 | 15 | 84 |

| 2.5 | 400 | 12.5 | 70 |

| 1.87 | 533 | 9.4 | 52 |

| 1.5 | 667 | 7.5 | 42 |

| 1.25 | 800 | 6.3 | 35 |

Verificación de simulación

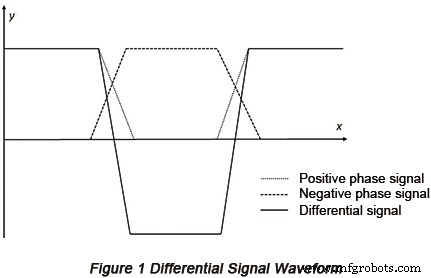

Tome la señal diferencial DQS (Data Strobe) entre TSM320 y MT41J256M16 como ejemplo, el software de simulación Cadence se aplica para transmitir la señal DOS a la memoria DRR3 para simular el chip de control de memoria, analizar su influencia en el tiempo de retención del establecimiento de la señal de datos y verificar el análisis anterior. El circuito de simulación se muestra en la Figura 2 a continuación.

Según la Figura 2, el voltaje de referencia de los pines de salida es de 1,5 V; el chip de control de memoria está conectado directamente con el chip de memoria a través del modo ODT (terminación en matriz) con una línea de transmisión de 800 mil; la impedancia diferencial es de 100Ω y la frecuencia del reloj de simulación de 800MHz. Una línea de transmisión de 50 Ω está conectada en serie con un terminal de fase positiva DQS para simular el fenómeno de discrepancia de pares diferenciales. En la situación de diferenciales isométricos, la longitud de la línea de transmisión de un solo terminal de 50 Ω es 0 mil.

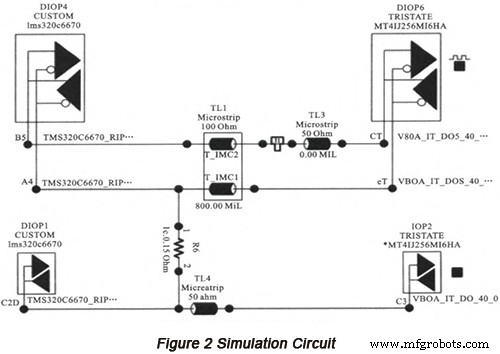

Se realiza la simulación al circuito isométrico diferencial. La figura 3 ilustra la señal de salida en el terminal de fase positiva de las señales diferenciales. A través de la medición, el tiempo de subida es de aproximadamente 216ps mientras que el tiempo de caída es de 219ps, por lo que el tiempo mínimo de subida/bajada Tr debería ser 216ps.

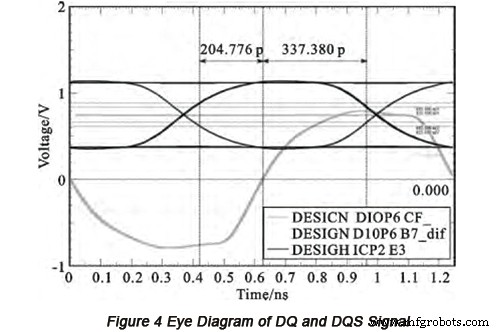

La Figura 4 es un diagrama de ojo de la señal de datos DQ y la señal de puerta DQS a través de la simulación con el tiempo de establecimiento 205ps y el tiempo de retención 337ps. De acuerdo con la tasa de rotación de las señales DQS y DQ a través de la simulación y según el manual de datos, el tiempo mínimo de establecimiento de las señales de datos por parte del terminal receptor debe ser de 85ps y el tiempo mínimo de retención es de 95ps. Por tanto, la sobremedida del tiempo mínimo de establecimiento es de 120ps y del tiempo de mantenimiento de 242ps.

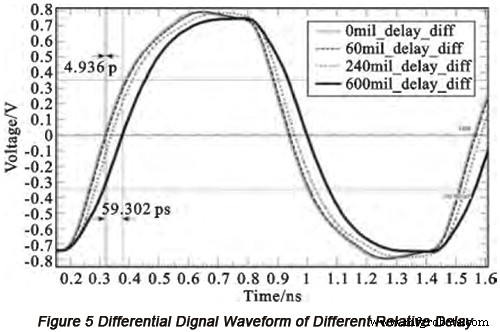

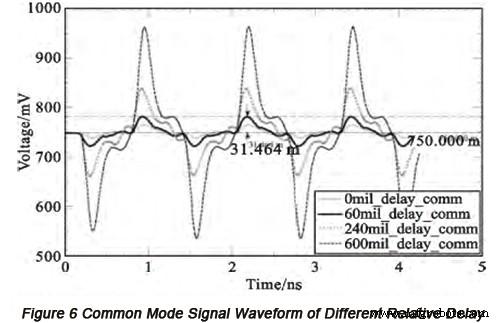

La situación de la existencia de 0.05Tr colocación de fase, 0.2Tr colocación de fase y 0.5Tr se debe considerar la ubicación de la fase en el terminal de fase positiva. El circuito se puede simular con una longitud de línea de transmisión de un solo terminal que se establece respectivamente en 60 mil, 240 mil y 600 mil. La forma de onda de la señal diferencial y la forma de onda de la señal de modo común a través de la simulación 4 veces se ilustran en las Figuras 5 y 6.

Según la Figura 5, la distorsión es mínima cuando los retrasos relativos de 0.05Tr y 0.2Tr tener lugar. Especialmente cuando el retraso relativo es 0.05Tr , solo la colocación de alrededor de 5ps de la señal diferencial a la forma de onda de la señal diferencial sin demora relativa para que la sobremedida del establecimiento de la señal de datos aumente en alrededor de 5ps con el tiempo de sobremedida de mantenimiento disminuido en 5ps. Aunque se reduce el tiempo de sobremedida de espera, esta cantidad de colocación es muy pequeña para el tiempo de espera de 242 ps. Se puede evitar la secuenciación temporal. Para la situación en la que el retraso relativo es 0.5Tr , la colocación de la forma de onda de la señal DQS ha alcanzado aproximadamente 60ps. Aunque esta ubicación todavía se encuentra dentro de la categoría de sobremedida, se debe prestar suficiente atención.

Según la Figura 6, el aumento de la ubicación de la fase conduce a una fluctuación periódica obvia en las ondas y al aumento gradual del rango. Cuando el retraso relativo es respectivamente 0.05Tr , 0.2Tr y 0.5Tr , el valor máximo medido de la señal de modo común es respectivamente 61 mV, 176 mV y 430 mV, entre los cuales el valor más alto es siete veces el más bajo. El mayor rango de fluctuación es respectivamente 4,3 %, 12 % y 29 %.

En conclusión, el resultado de la simulación es compatible con el resultado obtenido a través del análisis del diagrama de funciones matemáticas. Cuando el retardo relativo entre pares diferenciales es inferior a 0,05Tr , la influencia en las señales es bastante pequeña.

El período de reloj mínimo de la señal de salida en el terminal de salida se aplica para estimar la categoría de control de retardo relativo. Según el manual del componente, el período de reloj mínimo de los componentes es de 1,25 ns con una frecuencia de reloj de 800 MHz. De acuerdo con la Tabla 1, el retraso relativo debe controlarse dentro de los 6,3 ps con una longitud de línea de transmisión de 35 mil. Aparentemente, este valor es mucho menor que la categoría de control del retraso relativo de 0.05Tr a través de la simulación. Por lo tanto, la categoría de control de demora relativa estimada es relativamente conservadora, que es más específica que el resultado simulado.

Recursos útiles

• Investigación sobre el diseño de PCB de alta velocidad en el sistema de aplicaciones integradas

• Cómo diseñar planos de imagen para PCB de alta velocidad

• Desafíos del diseño de PCB de alta velocidad sobre la integridad de la señal y sus soluciones

• Simulación de PCB usando OrCAD PSpice

• Servicio completo de fabricación de PCB de PCBCart:múltiples opciones de valor agregado

• Servicio avanzado de ensamblaje de PCB de PCBCart:comience desde 1 pieza

Tecnología Industrial

- Directrices para el diseño de RF y microondas

- Materiales y diseño de PCB para alta tensión

- Capacidades de curvatura flexible y rígido-flexible en el diseño de PCB

- Pasos y proceso Aprenda a proteger su diseño de PCB

- Retrocesos y soluciones en el diseño de PCB RF

- 3 técnicas de enrutamiento en el diseño de circuito de señal de alta velocidad de PCB

- Sugerencias de diseño de alta velocidad

- Método de supresión del reflejo de la señal en el diseño de PCB de alta velocidad

- Discusión sobre potencia y tierra en la compatibilidad electromagnética de PCB

- Análisis de integridad de señal y diseño de PCB en circuito mixto digital-analógico de alta velocidad

- Desafíos del diseño de PCB de alta velocidad en la integridad de la señal y sus soluciones