El chip AI Edge renuncia a la matriz de acumulación múltiple para alcanzar 55 TOPS / W

Una startup de Silicon Valley afirma que ha reinventado las matemáticas de las redes neuronales y ha producido un chip de IA de borde complementario, ya muestreado, que no utiliza la gran variedad habitual de unidades de acumulación múltiple. El chip puede ejecutar el equivalente a 4 TOPS, con un impresionante consumo de energía de 55 TOPS / W y, según la empresa, logra una inferencia de clase de centro de datos en menos de 20 mW (YOLOv3 a 30 fps).

Perceive, con sede en San José, ha estado en modo súper sigiloso hasta ahora; como un derivado de Xperi, ha sido financiado en su totalidad por su matriz desde que se formó oficialmente hace dos años. El equipo es de 41 personas, con un número similar dentro de Xperi trabajando en aplicaciones para el chip. El CEO fundador Steve Teig también es CTO de Xperi; anteriormente fue fundador y CTO de Tabula, la startup de lógica programable 3D que cerró sus puertas hace cinco años, y antes de eso, CTO de Cadence.

Teig explicó que la idea inicial era combinar el conocimiento clásico de Xperi del procesamiento de imágenes y audio con el aprendizaje automático. Xperi posee marcas como DTS, IMAX Enhanced y HD Radio; su cartera de tecnología incluye software de procesamiento de imágenes para funciones como ojos rojos y estabilización de imagen que se utilizan ampliamente en cámaras digitales, además de software de procesamiento de audio para reproductores de discos Blu-Ray.

Steve Teig (Imagen:Percibir)

“Comenzamos con una hoja de papel en blanco y usamos la teoría de la información para preguntar:¿qué cálculos están haciendo realmente las redes neuronales? ¿Y hay una forma diferente de abordar ese cálculo que podría cambiar lo que es posible [en el borde]? " Dijo Teig. "Después de un par de años de hacer este trabajo, descubrimos que lo era, y luego decidimos ... deberíamos hacer un chip que incorpore estas ideas".

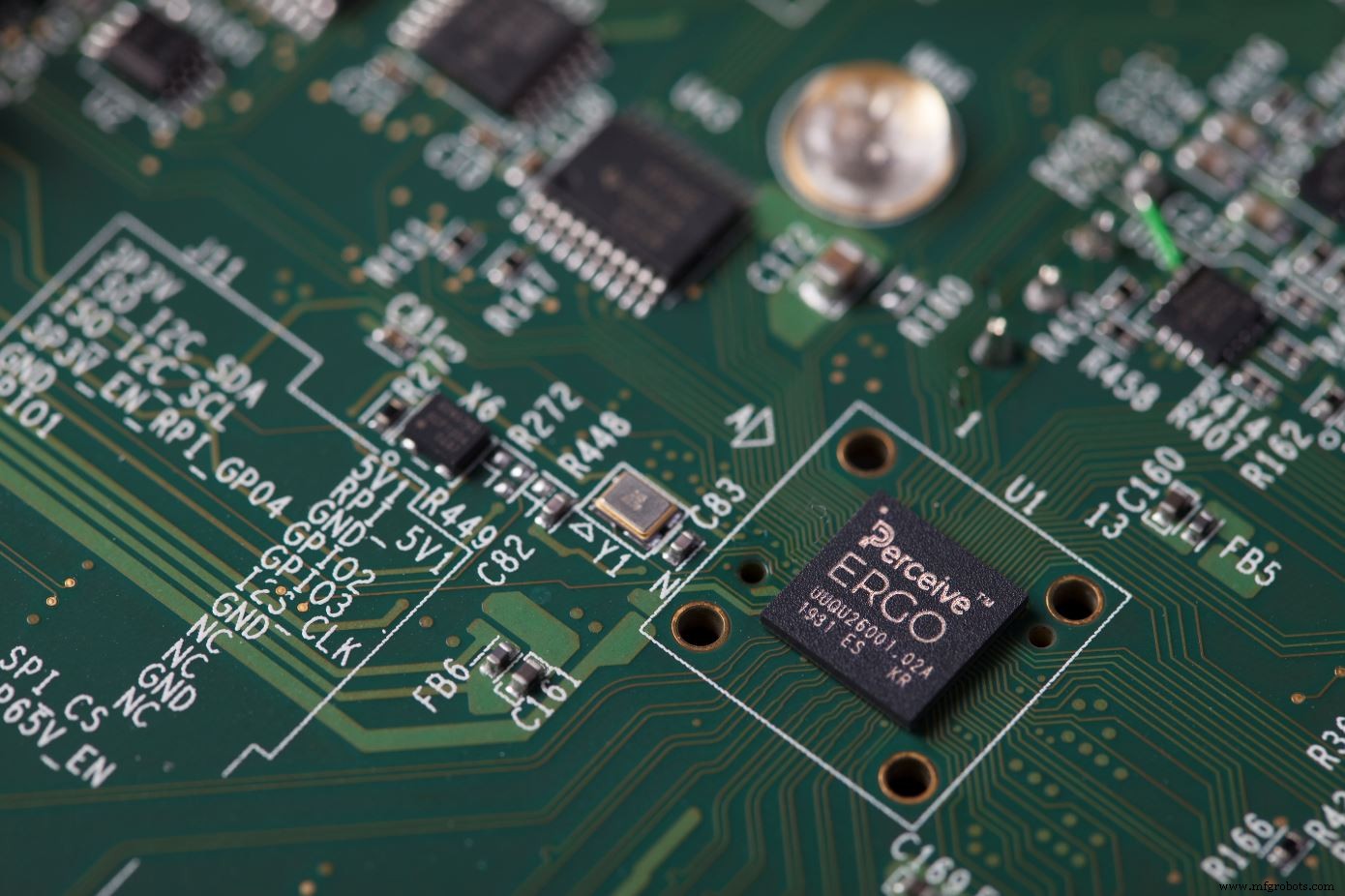

La idea que Teig presentó a la placa Xperi fue crear una empresa para hacer un chip que pudiera hacer inferencias significativas en dispositivos periféricos con un presupuesto de energía de 20 mW. El resultado, un chip de 7x7 mm llamado Ergo, puede ejecutar 4 TOPS sin RAM externa (de hecho, está ejecutando el equivalente a lo que puede lograr una GPU con 4 TOPS, explicó Teig). Ergo admite muchos estilos de redes neuronales, incluidas las redes convolucionales (CNN) y las redes recurrentes (RNN), en contraste con muchas soluciones en el mercado que están diseñadas para CNN. Ergo puede incluso ejecutar varias redes heterogéneas simultáneamente.

"Lo único que limita la cantidad de redes que podemos ejecutar es la memoria total que se requiere para la combinación", dijo Teig, y agregó que Perceive ha demostrado ejecutar simultáneamente YOLOv3 o M2Det, con 60 o 70 millones de parámetros, más ResNet 28 con varios millones. parámetros, más un LSTM o RNN para realizar procesamiento de voz y audio. En una aplicación, esto podría corresponder a la inferencia de imágenes y audio al mismo tiempo.

Perceive también afirma que su chip Ergo es extraordinariamente eficiente en el consumo de energía, alcanzando 55 TOPS / W. Esta cifra es un orden de magnitud por encima de lo que afirman algunos competidores. Las cifras de Perceive lo muestran ejecutando YOLOv3, una gran red con 64 millones de parámetros, a 30 fotogramas por segundo mientras consume solo 20 mW.

Perceive afirma que la eficiencia de su chip Ergo es de hasta 55 TOPS / W, ejecutando YOLOv3 a 30 fps con solo 20 mW (Imagen:Perceive)

Esta eficiencia energética se debe a algunas técnicas agresivas de sincronización de energía y sincronización de reloj, que explotan la naturaleza determinista del procesamiento de la red neuronal; a diferencia de otros tipos de código, no hay ramas, por lo que los tiempos se conocen en tiempo de compilación. Esto permite que Perceive sea preciso sobre qué se debe encender y cuándo.

“En un entorno alimentado por batería, [el chip] puede estar literalmente apagado - cero milivatios - y tener algún tipo de sensor de movimiento de microvatios o micrófono analógico para detectar algo que pueda ser de interés”, dijo Teig. “Podemos despertarnos, cargar una red neuronal gigante de clase de centro de datos y ejecutarla en aproximadamente 50 milisegundos, incluido el descifrado. Así que dejamos solo dos fotogramas de vídeo en el suelo ".

Pero el diseño cuidadoso del hardware es solo una parte del panorama.

Teoría de la información

"Hemos ideado una forma diferente de representar el cálculo subyacente en sí mismo y la aritmética que lo acompaña", dijo Teig. "Representamos a la red en sí de una nueva manera, y de ahí proviene nuestra ventaja".

Perceive comenzó con la teoría de la información, una rama de la ciencia que incluye formas matemáticas de distinguir la señal del ruido, y usó sus conceptos para ver cuántos cálculos se requieren para extraer la señal del ruido. Teig usa una red de detección de objetos como ejemplo.

"Le entregas a la red millones de píxeles y todo lo que quieres saber es, ¿hay un perro en esta imagen o no?" él dijo. “Todo lo demás en la imagen es ruido, excepto la perridad [la señal]. La teoría de la información la hace cuantificable:¿cuánto hay que saber [para saber si hay un perro en la imagen]? De hecho, puede hacerlo matemáticamente preciso ".

Como lo describe Teig, las redes neuronales convencionales pueden generalizar basándose en ver muchas imágenes de perros porque han encontrado al menos parte de la señal en el ruido, pero esto se ha hecho de manera empírica en lugar de con un enfoque matemáticamente riguroso. Esto significa que el ruido se transmite con la señal, lo que hace que las redes neuronales convencionales sean muy grandes y las hace susceptibles a ejemplos de adversarios y otros trucos.

"Cuanto más matemático pueda ser para determinar qué partes deben conservarse y qué partes son solo ruido, mejor trabajo podrá hacer en la generalización y menos gastos indirectos tendrá que llevar consigo", dijo Teig. "Yo diría que incluso las redes neuronales actuales extraen la señal del ruido, simplemente no lo hacen de una manera tan rigurosa y, como resultado, llevan un peso adicional".

Este punto de vista de la teoría de la información es la base de la estrategia de aprendizaje automático de Perceive, que representa las redes neuronales de una manera nueva.

"Realmente, este es un matrimonio entre una perspectiva teórica de la información sobre cómo hacer aprendizaje automático y un chip que encarna esas ideas", dijo Teig.

Arquitectura de chip

Con la experiencia de Teig como director de tecnología de Tabula, podría esperar hardware basado en lógica programable, pero ese no es el caso aquí.

“He estado fuertemente influenciado por pensar en lógica programable durante una década y cómo construir arquitecturas de interconexión ricas para permitir computación muy paralela de alto rendimiento, porque mucho de lo que sucede en una FPGA también es masivamente paralelo y muy intensivo en su interacción entre la computación y la memoria ”, dijo Teig. “Ese trabajo definitivamente ha influido en mi trabajo en Perceive, pero lo que tenemos no es lógica programable per se . Ha sido influenciado por esa forma de pensar, pero la arquitectura en sí gira en torno a las redes neuronales ".

El tejido de la red neuronal de Perceive es escalable, con el chip Ergo inicial que tiene cuatro clústeres de cómputo, cada uno con su propia memoria. Si bien los detalles exactos aún están en secreto, Teig dijo que estos clústeres son significativamente diferentes a los que se encuentran en otros aceleradores de IA, que generalmente usan matrices de unidades de acumulación múltiple (MAC) para calcular productos escalares de vectores y matrices.

La tecnología de Perceive se basa en reinventar las matemáticas de redes neuronales utilizando técnicas de la teoría de la información (Imagen:Perceive)

"No estamos haciendo eso", dijo Teig. “No tenemos una variedad de MAC. Como resultado ... somos de 20 a 100 veces más eficientes energéticamente que cualquier otra cosa en el mercado, la razón es que todos los demás están haciendo lo mismo y nosotros no. Nuestra representación de las redes es bastante nueva y eso es lo que nos ha permitido lograr una eficiencia tan grande. Eso, más la tecnología de aprendizaje automático que puede encontrar esta representación de las redes y entrenar las redes de una manera que las haga compatibles con lo que el chip quiere ver ".

Imagen y audio

Ergo puede admitir dos cámaras e incluye una unidad de procesamiento de imágenes que funciona como un preprocesador, manejando cosas como corrección de distorsión de imágenes de lentes de ojo de pez, corrección de gamma, balance de blancos y recorte.

"No es sofisticado, pero el preprocesamiento que obviamente es útil para hacer en hardware, lo hacemos en hardware", dijo Teig. "Y también tenemos el equivalente de audio:podemos tomar varios micrófonos estéreo y hacer formación de haz, por ejemplo".

También hay un microprocesador Synopsis ARC con un bloque DSP que también se puede utilizar para el preprocesamiento, además de un bloqueo de seguridad, también de Synopsis.

“Una de las cosas que hemos hecho es cifrar absolutamente todo para mantener un nivel de seguridad en un entorno de IoT. Encriptamos las redes, encriptamos el código que se ejecuta en el microprocesador, encriptamos las interfaces, encriptamos todo ”, dijo Teig.

El chip cuenta con E / S apropiadas para sensores fuera de imagen y audio, y es compatible con una memoria Flash externa y / o un microprocesador que permite actualizaciones inalámbricas. Esto podría usarse para actualizar las redes neuronales cargadas en el chip o cargar diferentes redes según sea necesario.

Ergo está tomando muestras ahora junto con un tablero de referencia adjunto. Se espera una producción en masa en el segundo trimestre de 2020.

Incrustado

- Una perspectiva brillante para EDA en la nube

- Diseñar con Bluetooth Mesh:¿Chip o módulo?

- La arquitectura del chip AI apunta al procesamiento de gráficos

- El pequeño módulo Bluetooth 5.0 integra una antena de chip

- Pequeño módulo de IA basado en Google Edge TPU

- Los investigadores crean una pequeña etiqueta de identificación de autenticación

- Se estrena el procesador de radar de imágenes automotrices de 30 fps

- El chip de radar de baja potencia utiliza redes neuronales con picos

- La placa del sensor inteligente acelera el desarrollo de la IA de borde

- La cámara inteligente ofrece inteligencia artificial de borde de visión artificial de borde llave en mano

- Informe:La escasez de chips y el borde / IoT impulsarán el cambio de TI en 2022