Diseño e implementación de tableros de interruptores de interconexión FDR de alta densidad

Hoy en día, la velocidad de transmisión de la red de interconexión de computadoras de alto rendimiento con la aplicación de transmisión en serie de alta velocidad se ha convertido en FDR (Fourteen Data Rate, 14 Gb/s), la cuarta generación del SDR principal (Single Data Rate, 2,5 Gb/s). s), DDR (velocidad de datos doble, 5 Gb/s) y QDR (velocidad de datos cuádruple, 10 Gb/s). El diseño de PCB (placa de circuito impreso) con interconexión y placa de conmutación y tarjetas de interfaz que son esenciales para la formación de Internet ha entrado en el campo de alta velocidad y alta frecuencia de FDR. Dado que el tiempo de subida de la señal FDR se ha reducido drásticamente a la magnitud de 10ps, una serie de problemas relacionados con la integridad de la señal se han convertido en las características clave para determinar la posibilidad de implementación de funcionalidad y operación confiable, como atenuación, diafonía, reflexión, interferencia electromagnética, etc. Basado en las características de los chips de interconexión FDR que incluyen múltiples puertos, múltiples canales, múltiples categorías de energía y alto consumo de energía, siempre se requiere que múltiples chips de interconexión estén integrados en una sola placa de interconexión para aumentar la tasa de rendimiento. En una placa con espacio limitado, por un lado, se deben cumplir algunos requisitos, como la disposición de los componentes y la disipación de calor, el enrutamiento con alta densidad, la transmisión a larga distancia en la parte posterior de la placa y la integridad de todo tipo de señales. Por otro lado, se deben tener en cuenta algunos elementos, incluido el período de diseño de PCB, las limitaciones de la técnica de fabricación de PCB y el control de costos. Por lo tanto, es extremadamente difícil para la implementación del diseño y la verificación de la simulación. Basado en el ejemplo de diseño de PCB de interconexión FDR y placa de conmutación, este artículo presenta algunos métodos de optimización en términos de selección de material de sustrato, diseño de apilamiento, reglas de enrutamiento y diseño antiinterferencias para resolver el problema de integridad de todo tipo de señales en el proceso de diseño de PCB de alta velocidad FDR.

Atributo de atenuación y selección de material de sustrato

Para las señales de alta frecuencia FDR, la pérdida de la línea de transmisión es el problema relacionado con la integridad de la señal. Cuando las señales FDR se transmiten desde el terminal transmisor al terminal receptor a lo largo de los canales de interconexión, debido a que la atenuación de alta frecuencia es mucho mayor que la atenuación de baja frecuencia, se ha producido una deformación grave en la forma de onda de la señal que llega al terminal receptor. La deformación se clasifica principalmente en dos aspectos:la oscilación de voltaje de las señales ha disminuido considerablemente, mientras que se ha producido una mala degradación en el borde de subida de la señal. El primero limita la distancia de transmisión de las señales, mientras que el segundo provoca interferencias entre códigos. La pérdida de la línea de transmisión A puede considerarse como la suma de la pérdida del conductor Acond y pérdida dieléctrica Adiel como se muestra en la Fórmula (1):A =Adiel + Acontra .

La pérdida del conductor se refiere a la pérdida causada por la resistencia en serie en el conductor de cobre entre la ruta de la señal y la ruta de retorno. En la situación de alta frecuencia, el efecto piel hace que la corriente fluya en la superficie de los conductores de cobre circundantes. Con el aumento de la resistencia en serie equivalente de los conductores de cobre, la pérdida del conductor aumentará con el aumento de la frecuencia que es positivamente proporcional a la raíz cuadrada de la frecuencia, que se ilustra en la Fórmula (2): .

.

La pérdida dieléctrica se refiere a la pérdida generada por el medio del material del sustrato, determinada principalmente por el atributo del material y no relacionada con la construcción geométrica, incluido el ancho del conductor, proporcional positiva a la frecuencia, que se muestra en la Fórmula (3): .

.

Con base en la Fórmula (2), el aumento del ancho de la línea es capaz de reducir la pérdida del conductor. Sin embargo, en el diseño práctico de PCB, el ancho de los conductores nunca puede ser indefinidamente ancho como resultado de la limitación del espacio entre los pines, la placa, el número de capas de señal y la impedancia. El ancho/espaciado/ancho del conductor comúnmente aplicado en el diseño FDR es generalmente 7mil/7mil/7mil o 8mil/10mil/8mil. Cuando el ancho del conductor es el mismo, la pérdida del conductor es positiva proporcional a la longitud del conductor, sin ninguna relación con el material. Por lo tanto, para reducir la pérdida de transmisión total, solo se debe tener en cuenta la pérdida dieléctrica. Según la fórmula (3), la pérdida dieléctrica es proporcional al factor de disipación y la aplicación de pequeños factores de disipación puede ser útil para reducir la pérdida dieléctrica, lo que conduce a la pérdida de transmisión general.

La Tabla 1 enumera los parámetros de atributos de tres materiales de placa de alta velocidad ordinarios y los valores de pérdida calculados de acuerdo con la fórmula (1), (2) y (3) cuando la tasa de transmisión es de 14 Gb/s, el ancho del conductor es de 8 mil y la impedancia es de 50 Ω.

| Parámetros del material de la placa | FR4 | Nelco4000-13SI | Megtron6 |

| [email protected] | 0.02 | 0.008 | 0.004 |

| [email protected] | 4.10 | 3.200 | 3.600 |

| Acondición @7GHz/entrada | 0.24 | 0,240 | 0,240 |

| Adiel @7GHz/entrada | 0.65 | 0,230 | 0.120 |

| [email protected]/en | 0.89 | 0,470 | 0,360 |

| [email protected]/30in | 27,00 | 14.000 | 11.000 |

| Coste relativo | 1,00 | 3.500 | 8.000 |

Se puede indicar que con una velocidad de transmisión de 14 Gb/s y una longitud de transmisión de 30 pulgadas, la pérdida de transmisión general de Nelco4000-13SI es de aproximadamente 14 dB, mientras que la atenuación de oscilación de voltaje que puede soportar un chip FDR típico está en el rango de 20 dB a 25dB. Por lo tanto, este tipo de material de placa se puede aplicar en el diseño de placa de interruptor de interconexión FDR con una distancia de transmisión inferior a 30 pulgadas. Sin embargo, la atenuación de transmisión general de FR4 es de aproximadamente 27 dB y FR4 no se puede aplicar para el diseño FDR de diseño de larga distancia, pero las tarjetas de interfaz de interconexión FDR con distancia de transmisión corta pueden seleccionar FR4 para reducir el costo. En cuanto a Megtron6, cuya atenuación de transmisión general es la más pequeña, presenta el costo más alto y su aplicación en FDR conduce al aumento de las tarifas de arquitectura del sistema. En conclusión, para PCB de alta frecuencia, el material de la placa es la base y la selección del material de la placa determina la longitud de transmisión de las señales.

Disposición y diseño de pila

Para el diseño de PCB, primero se debe tener en cuenta la estructura y la pila de la placa de circuito. Por lo general, se ha determinado el patrón y la forma de la placa de circuito y la determinación del número de pila se basa en la frecuencia de la señal, la densidad de pines de la placa de circuito, el costo de fabricación de PCB, el período de fabricación y los requisitos de confiabilidad. Los tableros de interruptores de interconexión FDR tienen alta frecuencia y densidad, y la aplicación de tableros multicapa es el paso necesario para reducir la interferencia. Además, la determinación del número de pila es crucial.

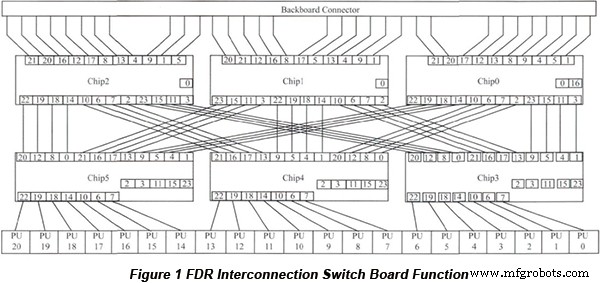

Hay 24 puertos en el chip de interconexión FDR y cada puerto presenta 8 canales Tx y 8 canales Rx en el método de operación de interacoplamiento. La placa de interconexión FDR aplica 6 chips de interconexión y 3 chips de enlace descendente y se accede a 32 puertos a través del conector de la placa trasera. 3 chips de enlace ascendente acceden a 21 puertos a través de fibras ópticas QSFP (Quad Small Form-factor Pluggable). El chip de enlace ascendente y el chip de enlace descendente están conectados entre sí a través de 4 puertos, como se muestra en la Figura 1.

FDR cuenta con el paquete de BGA (Ball Grid Array) con un área de 50 mm x 50 mm, 1157 pines y espaciado de 1,0 mm y pines P/N en los puertos de Tx y Rx se distribuyen de acuerdo con 3 círculos concéntricos. Teóricamente, se pueden aplicar 3 capas de señal para sacar todos los pines de todos los puertos de BGA. Con los siguientes dos elementos considerados, se pueden usar dos capas de señal para acceder a un grupo de pines de círculos concéntricos.

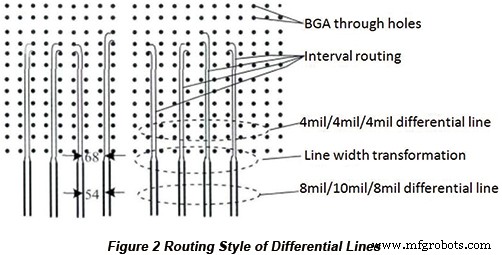

a. Debido a la limitación del espaciado, el ancho de línea/espaciado/ancho de las líneas diferenciales es de 4 mil/4 mil/4 mil y se expandirá a 8 mil/10 mil/8 mil saliendo de BGA y la distancia entre los pares de líneas diferenciales no debe ser inferior a 50 mil Por lo tanto, un par de líneas diferenciales deben ocupar un ancho de 2 mm y 48 pares de señales se encuentran a lo largo del borde con la mayor densidad. Entonces es difícil implementar este método.

b. El espacio entre los pines BGA es de 1 mm. Si se aplica una capa de señal para acceder a un grupo de señales de círculos concéntricos, el espacio entre los pares de líneas diferenciales bajo BGA es de solo 14 mil, lo que está lejos de los 50 mil requeridos. Además, la longitud máxima de enrutamiento paralelo es de solo 20 mm, lo que generará cierta diafonía.

Para evitar los factores negativos mencionados anteriormente, se aplican dos capas de señal para acceder a un grupo de señales de círculos concéntricos y la señal diferencial en cada capa de señal debe salir de BGA de acuerdo con un espacio de 50 mil. Por lo tanto, las placas de interconexión FDR requieren al menos 6 capas para hacer que todas las señales diferenciales salgan de BGA. Teniendo en cuenta la conectividad y la cantidad de enrutamiento de la placa y suficiente superficie de placa para intercambiar el condensador de acoplamiento, se aplican 8 señales internas y 22 capas de pila.

Análisis de diafonía y medidas de reducción

La diafonía es la primera consideración en términos de diseño de circuitos de alta velocidad y alta densidad. Cuando el voltaje y la corriente en la línea ofensiva cambian, el acoplamiento electromagnético tendrá lugar a través de la capacitancia mutua y la inductancia mutua entre la línea ofensiva y la línea víctima. La diafonía que fluye hacia el terminal de transmisión a lo largo de la línea víctima se denomina diafonía del terminal cercano, mientras que la diafonía que fluye hacia el terminal receptor a lo largo de la línea víctima se denomina diafonía del terminal lejano. En términos generales, el voltaje de ruido general en la línea de la víctima debe controlarse a menos del 5% del voltaje de la señal. Lo mejor es controlar el presupuesto de diafonía de la línea ofensiva de un solo borde dentro del 1% teniendo en cuenta otra fuente de ruido y la línea ofensiva alrededor de dos lados de la línea víctima.

Los puntos clave a seguir en términos de reducción de diafonía incluyen:

a. El espacio entre la línea ofensiva y la línea de la víctima debe ampliarse y la longitud del recorrido paralelo debe reducirse.

b. La tierra integrada se aplica para que sea la ruta de retorno de las señales. De acuerdo con la ley empírica, para la línea de banda de 50 Ω, cuando el espaciado es tres veces el ancho de la línea, la diafonía en el extremo cercano es de aproximadamente 0,5 %. Para la línea microstrip de 50 Ω, cuando el espaciado es tres veces el ancho de la línea, la diafonía en el extremo cercano es de aproximadamente el 1 %. La diafonía en el extremo lejano de las líneas de cinta o las líneas de microcinta totalmente integradas es casi cero y la polaridad de la diafonía en el extremo lejano de las líneas de transmisión de microcinta es negativa y su magnitud es relativamente grande porque la influencia del acoplamiento inductivo es mayor que el acoplamiento capacitivo.

• Enrutamiento de intervalos

En este diseño, la impedancia diferencial de la línea diferencial de alta velocidad es de 100 Ω. Basado en el solucionador de campo Si9000, el ancho de línea/espaciado/ancho de línea se calcula en 8mil/10mil/8mil. Cuanto más ancha es la línea, menor es la atenuación y el espaciado de 10 mil es para mantener la impedancia diferencial de 100 Ω. Este tipo de línea diferencial se aplica fuera del área del chip BGA. Para disminuir la diafonía, el espacio entre dos pares de líneas diferenciales no es inferior a 80 mil. The spacing between pins of interconnection chip in this article is 1mm and the through hole size limitation of BGA makes the line width/spacing/line width of the differential line in the BGA chip area 4mil/4mil/4mil. Although the differential impedance of this type of differential line is 100Ω as well, the lead loss is big, requiring differential line of 4mil/4mil/4mil to be transformed into 8mil/10mil/8mil as soon as it enters BGA chip area. In order to reduce crosstalk, differential line of 4mil/4mil/4mil in BGA chip area applies the way of interval routing to ensure the spacing between two pairs of differential lines more than 50mil as well, which is shown in Figure 2.

• Differential holes

Specific differential holes are set in this design for the application of exchange coupling capacitance on the connection surface layer. Ground holes have to be placed beside differential holes to provide backflow channel for returning path. Design of four ground holes features the best effect and two ground holes can be also applied when the area of board is limited. Besides, measures such as back drilling and internal pad eliminationhave should be taken to differential holes to reduce the impedance change at differential holes in order to decrease crosstalk and reflection.

• Preventing Tx and Rx from being routed in the same layer

In order to reduce crosstalk, Tx differential line should be routed in the different layer from Rx differential line. Here, Tx refers to the source terminal of differential line while Rx refers to the receiving terminal of differential line. If both of them have to be routed in the same layer, the spacing between them has to be over 5mm to ensure safety.

• 20H rule

In the PCB circuit with high frequency and high speed, RF energy is coupled by PCB power layer and ground layer and edge magnetic flux leakage is generated between power layer and ground layer. The radio RF energy can be radiated to the free space. 20H rule indicates that if there are high-speed currents on the board, there are electromagnetic fields associated with them. In the design of this article, the distance between all the routings and board edge should be at least 20 times of line width and the distance between high-speed differential holes and power plane cut-off lines is at least 5mm.

• Routing on the surface layer

In the design of high-frequency PCBs, with the relatively big far-end crosstalk between microstrip lines and strip lines considered, high-speed differential lines are prohibited on the surface layer. In the design of this article, at most 8 internal routing layers are required owing to the limitation of manufacturing craft. Moreover, the terminal arrangement limitation of interconnection chip makes it impossible for internal layers only to implement the connections of the interconnection differential lines between 6 chips inside connection board.

Helpful Resources

• Something You Must Know about HDI

• History of High-Density Packaging Technology

• 3 Keys to Designing a Successful HDI PCB

• Advantages of HDI Printed Circuit Boards

• Full Feature PCB Manufacturing Service from PCBCart - Multiple Value-added options

• Advanced PCB Assembly Service from PCBCart - Start from 1 piece

Tecnología Industrial

- Cambiar diseño de contacto

- Cómo documentar cables y arneses

- ¿Qué son los martillos de potencia? - Tipos, diseño y funcionamiento

- Placas de circuito impreso personalizadas de alta tecnología

- Directrices para el diseño de RF y microondas

- Materiales y diseño de PCB para alta tensión

- Capacidades de curvatura flexible y rígido-flexible en el diseño de PCB

- Retrocesos y soluciones en el diseño de PCB RF

- Tungsteno

- El proceso de diseño e implementación de la automatización de la planta

- El auge de las PCB de interconexión de alta densidad