Registros de cambio:entrada en serie, salida en serie

Los registros de desplazamiento de entrada y salida en serie retrasan los datos una vez para cada etapa.

Almacenarán un poco de datos para cada registro. Un registro de desplazamiento de entrada y salida en serie puede tener una longitud de uno a 64 bits, más si los registros o paquetes están en cascada.

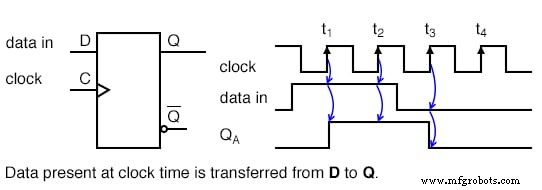

A continuación se muestra un registro de desplazamiento de una sola etapa que recibe datos que no están sincronizados con el reloj del registro.

Los "datos en" en el D pin del tipo D FF (Flip-Flop) no cambia de nivel cuando el reloj cambia de bajo a alto.

Es posible que deseemos sincronizar los datos con un reloj de todo el sistema en una placa de circuito para mejorar la confiabilidad de un circuito lógico digital.

El punto obvio (en comparación con la figura siguiente) ilustrado anteriormente es que cualquier "dato en" está presente en el D alfiler de tipo D FF se transfiere de D a la salida Q a la hora del reloj.

Dado que nuestro registro de desplazamiento de ejemplo utiliza elementos de almacenamiento sensibles al borde positivo, la salida Q sigue la D Ingrese cuando el reloj cambia de bajo a alto como se muestra en las flechas hacia arriba en el diagrama de arriba.

No hay duda de qué nivel lógico está presente en la hora del reloj porque los datos son estables mucho antes y después del borde del reloj.

Esto rara vez es el caso en los registros de desplazamiento de varias etapas. Pero, este fue un ejemplo fácil para empezar. Solo nos preocupa el margen positivo, de menor a mayor, del reloj.

El borde descendente se puede ignorar. Es muy fácil ver Q seguir D a la hora del reloj anterior.

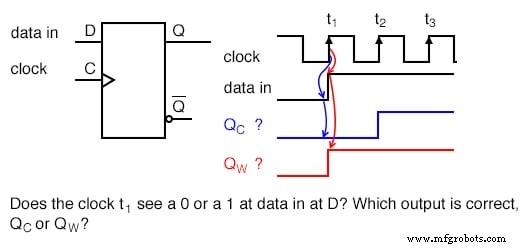

Compare esto con el diagrama a continuación, donde los "datos de entrada" parecen cambiar con el borde positivo del reloj.

Dado que "datos en" parece cambiar a la hora del reloj t 1 arriba, ¿qué significa el tipo D ¿FF ve a la hora del reloj?

La respuesta breve y simplificada es que ve los datos que estaban presentes en D antes del reloj.

Eso es lo que se transfiere a Q a la hora del reloj t 1 . La forma de onda correcta es Q C . En t 1 Q va a cero si aún no es cero.

El D el registro no ve un uno hasta el momento t 2 , momento en el que Q sube.

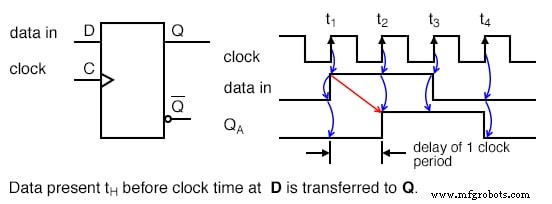

Dado que los datos anteriores, presentes en D está sincronizado a Q a la hora del reloj y Q no puede cambiar hasta la próxima hora del reloj, el D FF retrasa los datos en un período de reloj, siempre que los datos ya estén sincronizados con el reloj. La Q A La forma de onda es la misma que "entrada de datos" con un retraso de un período de reloj.

Una mirada más detallada a lo que la entrada del tipo D Flip-Flop ve lo que sigue a la hora del reloj.

Refiérase a la figura de abajo. Dado que los "datos ingresados" parecen cambiar a la hora del reloj (arriba), necesitamos más información para determinar cuál es el D FF ve.

Si la "entrada de datos" es de otra etapa de registro de desplazamiento, otro mismo tipo D FF, podemos sacar algunas conclusiones basándonos en la hoja de datos información.

Los fabricantes de lógica digital ponen a disposición información sobre sus partes en hojas de datos, que anteriormente solo estaban disponibles en una colección llamada libro de datos .

Los libros de datos todavía están disponibles; sin embargo, el sitio web del fabricante es la fuente moderna.

Los siguientes datos se extrajeron de la hoja de datos CD4006b para el funcionamiento a 5 V DC , que sirve como ejemplo para ilustrar la sincronización. [*]

- t S =100ns

- t H =60ns

- t P =200-400ns típ / máx.

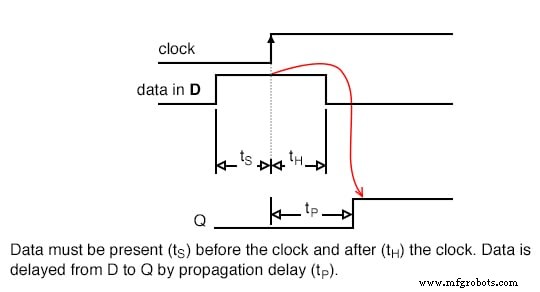

t S es el tiempo de configuración , los datos de tiempo deben estar presentes antes de la hora del reloj. En este caso, los datos deben estar presentes en D 100 ns antes del reloj.

Además, los datos deben conservarse durante tiempo de conservación t H =60 ns después de la hora del reloj. Deben cumplirse estas dos condiciones para registrar de forma fiable los datos de D a Q del Flip-Flop.

No hay ningún problema para cumplir con el tiempo de configuración de 60 ns como los datos en D ha estado allí durante todo el período de reloj anterior si proviene de otra etapa de registro de desplazamiento.

Por ejemplo, a una frecuencia de reloj de 1 Mhz, el período de reloj es de 1000 µs, mucho tiempo.

Los datos estarán presentes durante 1000 µs antes del reloj, que es mucho mayor que el mínimo requerido t S de 60ns.

El tiempo de espera t H =60ns se cumple porque D conectado a Q de otra etapa no puede cambiar más rápido que el retardo de propagación de la etapa anterior t P =200ns.

El tiempo de espera se cumple siempre que el retardo de propagación del D anterior FF es mayor que el tiempo de espera.

Datos en D impulsado por otra etapa Q no cambiará más rápido que 200ns para el CD4006b.

Para resumir, salida Q sigue la entrada D casi a la hora del reloj si los Flip-Flops se conectan en cascada a un registro de desplazamiento de múltiples etapas.

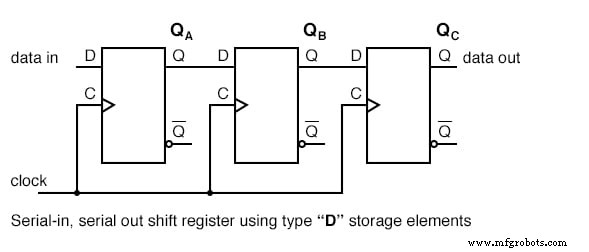

Tres tipo D Los flip-flops se conectan en cascada Q a D y los relojes en paralelo para formar un registro de desplazamiento de tres etapas arriba.

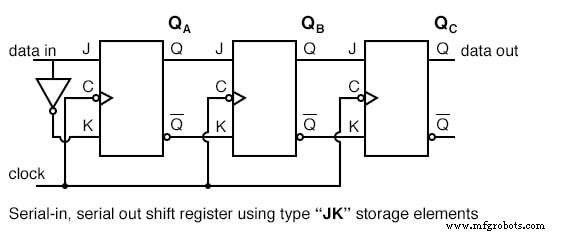

Escriba JK Flip Flops en cascada Q a J, Q ’a K con relojes en paralelo para producir una forma alternativa del registro de desplazamiento anterior.

Un registro de desplazamiento de entrada / salida en serie tiene una entrada de reloj, una entrada de datos y una salida de datos de la última etapa.

En general, las otras salidas de etapa no están disponibles. De lo contrario, sería un registro de desplazamiento de entrada en serie y salida en paralelo.

Las siguientes formas de onda son aplicables a cualquiera de las dos versiones anteriores del registro de desplazamiento de entrada y salida en serie.

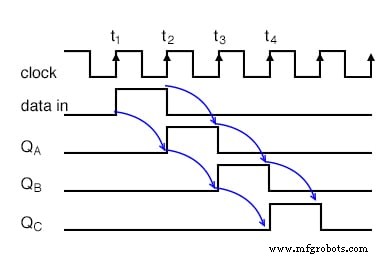

Los tres pares de flechas muestran que un registro de desplazamiento de tres etapas almacena temporalmente 3 bits de datos y los retrasa tres períodos de reloj desde la entrada hasta la salida.

A la hora del reloj t 1 una "entrada de datos" de 0 está cronometrado desde D a Q de las tres etapas. En particular, D de la etapa A ve una lógica 0 , que está sincronizado con Q A donde permanece hasta el tiempo t 2 .

A la hora del reloj t 2 una "entrada de datos" de 1 está cronometrado desde D a Q A . En las etapas B y C , un 0 , la alimentación de las etapas anteriores se sincroniza con Q B y Q C .

A la hora del reloj t 3 una "entrada de datos" de 0 está cronometrado desde D a Q A . Q A baja y permanece baja para los relojes restantes debido a que "datos en" es 0 . Q B sube en t 3 debido a un 1 de la etapa anterior. Q C sigue siendo bajo después de t 3 debido a un mínimo de la etapa anterior.

Q C finalmente sube en el reloj t 4 debido a la alta alimentación a D de la etapa anterior Q B . Todas las etapas anteriores tienen 0 s cambió a ellos. Y, después del siguiente pulso de reloj en t 5 , toda lógica 1 s habrán sido desplazados, reemplazados por 0 s

Dispositivos de entrada / salida en serie

Examinaremos más de cerca las siguientes piezas disponibles como circuitos integrados, cortesía de Texas Instruments.

Para obtener las hojas de datos completas del dispositivo, siga los enlaces.

- CD4006b registro de desplazamiento de entrada / salida en serie de 18 bits

- CD4031b Registro de desplazamiento de entrada / salida en serie de 64 bits

- CD4517b registro de desplazamiento de entrada / salida en serie dual de 64 bits

Los siguientes registros de desplazamiento de entrada / salida en serie son CMOS de la serie 4000 (Semiconductores de óxido de metal complementario) de la familia.

Como tal, aceptarán un V DD , fuente de alimentación positiva de 3 voltios a 15 voltios. El V SS el pin está conectado a tierra.

La frecuencia máxima del reloj de cambio, que varía con V DD , son unos pocos megahercios.

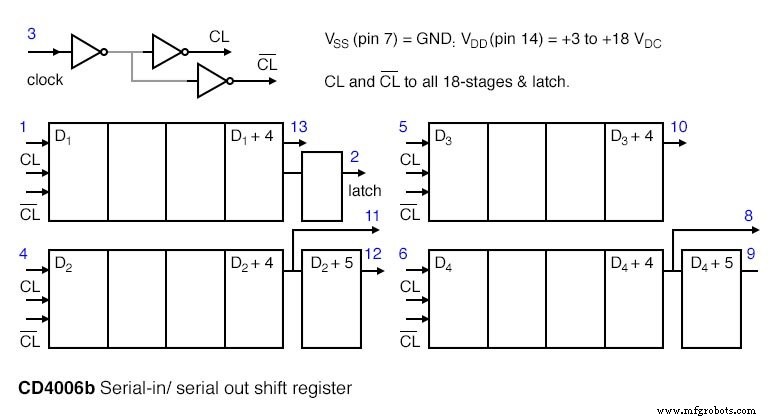

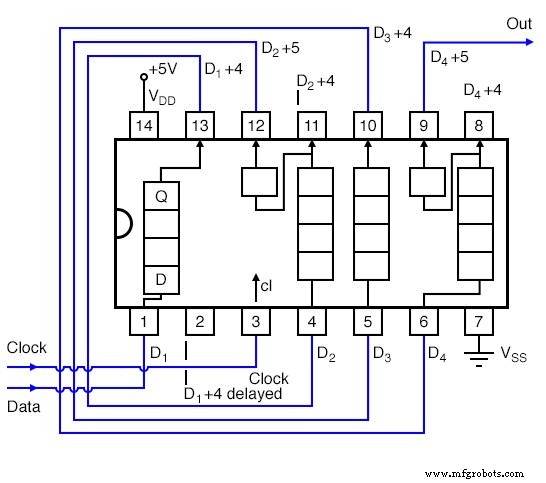

El CD4006b de 18 bits consta de dos etapas de 4 bits y dos etapas más de 5 bits con una toma de salida de 4 bits.

Por lo tanto, las etapas de 5 bits podrían usarse como registros de desplazamiento de 4 bits.

Para obtener un registro de desplazamiento completo de 18 bits, la salida de un registro de desplazamiento debe conectarse en cascada a la entrada de otro y así sucesivamente hasta que todas las etapas creen un solo registro de desplazamiento como se muestra a continuación.

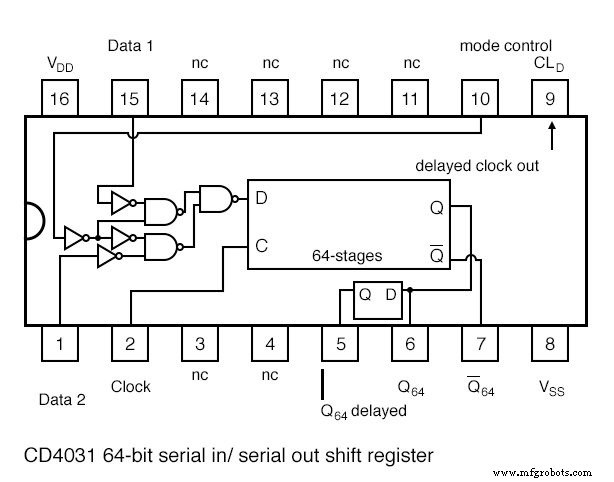

A continuación se muestra un registro de desplazamiento de entrada / salida en serie CD4031 de 64 bits.

Varios pines no están conectados (nc). Tanto Q como Q 'están disponibles en la etapa 64, en realidad Q 64 y Q ’ 64 .

También hay un Q 64 "Retrasado" desde una mitad de la etapa que se retrasa por medio ciclo de reloj. Una característica importante es un selector de datos que se encuentra en la entrada de datos al registro de desplazamiento.

El "control de modo" selecciona entre dos entradas:datos 1 y datos 2. Si el "control de modo" es alto, los datos se seleccionarán de "datos 2" para ingresar al registro de desplazamiento.

En el caso de que el “control de modo” sea lógicamente bajo, se selecciona el “dato 1”. En las dos figuras siguientes se muestran ejemplos de esto.

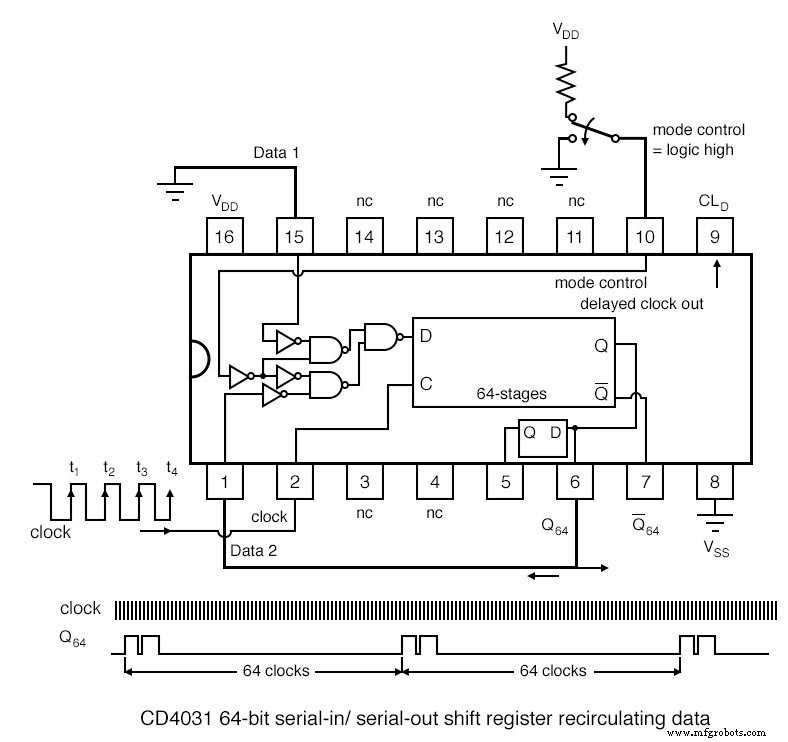

Los "datos 2" de arriba están conectados al Q 64 salida del registro de desplazamiento. Con el "control de modo" alto, el Q 64 la salida se enruta de nuevo a la entrada de datos D de la palanca de cambios.

Los datos recircularán de salida a entrada. Los datos se repetirán cada 64 pulsos de reloj como se muestra arriba.

La pregunta que surge es ¿cómo llegó este patrón de datos al registro de desplazamiento en primer lugar?

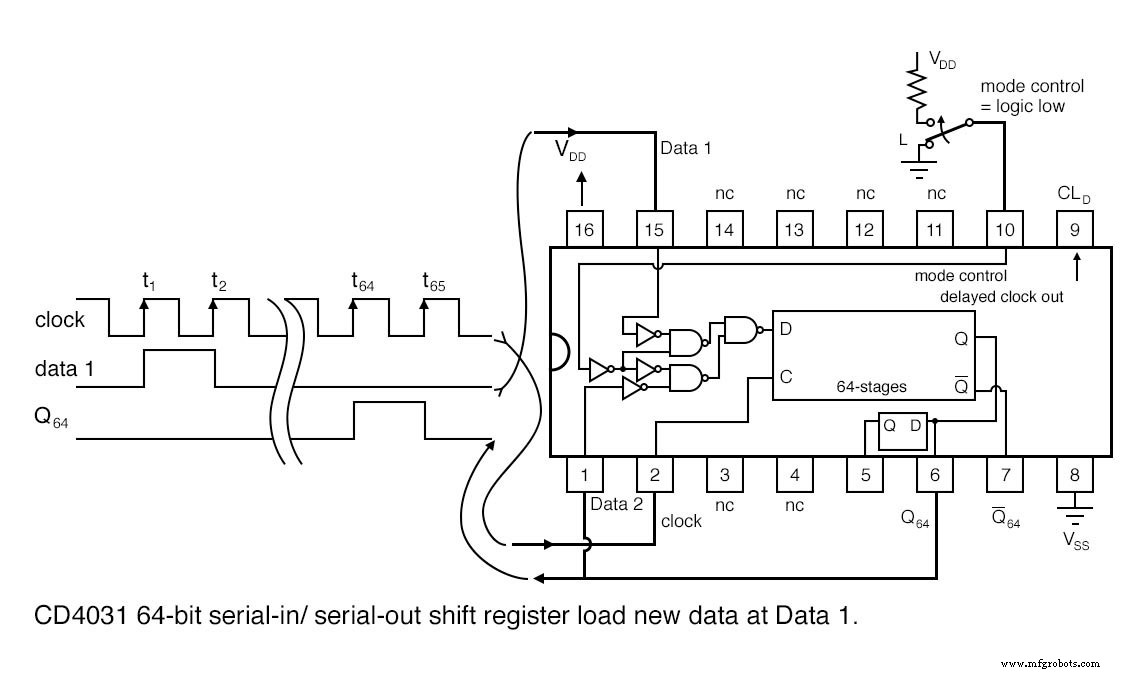

Con el "control de modo" bajo, se selecciona el "dato 1" del CD4031 para ingresarlo en la palanca de cambios.

La salida, Q 64 , no se recircula porque la puerta del selector de datos inferior está deshabilitada .

Por deshabilitado queremos decir que la "selección de modo" lógica baja invertida dos veces a un nivel bajo en la puerta NAND inferior evita que pase cualquier señal en el pin inferior (dato 2) a la salida de la puerta.

Por lo tanto, está deshabilitado.

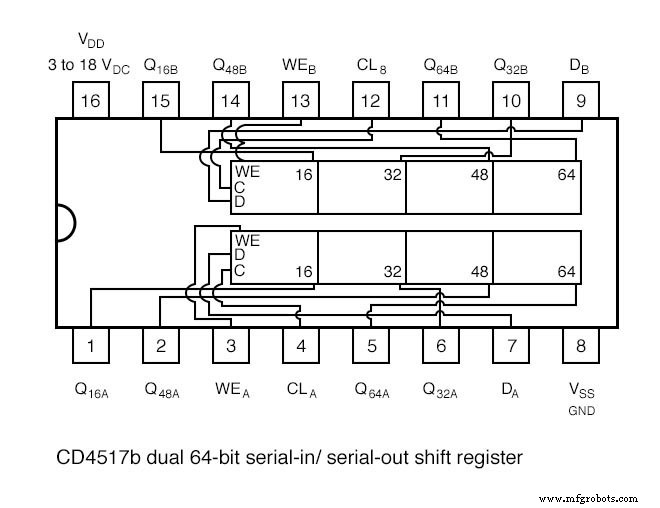

Arriba se muestra un registro de desplazamiento dual CD4517b de 64 bits. Tenga en cuenta los grifos en las etapas 16, 32 y 48.

Eso significa que los registros de desplazamiento de esas longitudes se pueden configurar desde uno de los desplazadores de 64 bits.

Por supuesto, los desplazadores de 64 bits pueden conectarse en cascada para producir un registro de desplazamiento de 80 bits, 96 bits, 112 bits o 128 bits.

El reloj CL A y CL B deben estar en paralelo al conectar en cascada las dos palancas de cambio. NOSOTROS B y WE B están conectados a tierra para operaciones de cambio normales.

Las entradas de datos a los registros de desplazamiento A y B son D A y D B respectivamente.

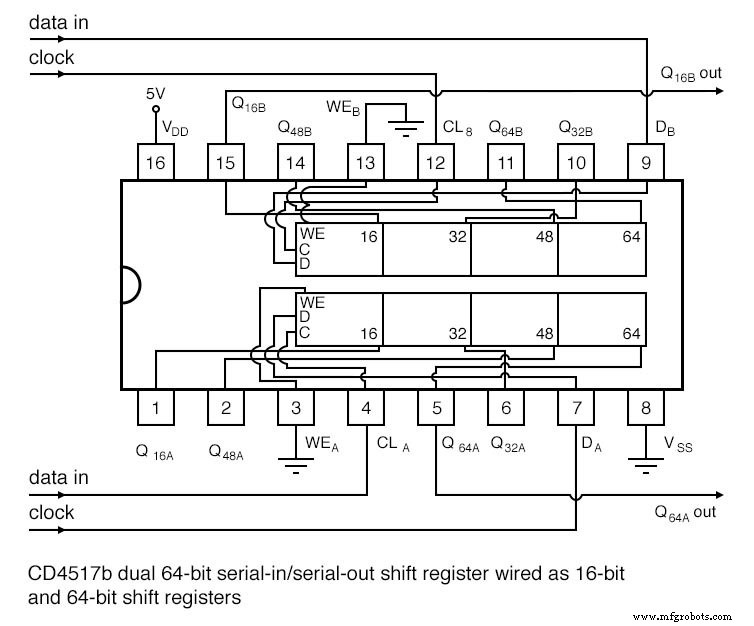

Supongamos que necesitamos un registro de desplazamiento de 16 bits.

¿Se puede configurar esto con el CD4517b? ¿Qué tal un registro de 64 turnos de la misma parte?

Arriba mostramos A CD4517b cableado como un registro de desplazamiento de 16 bits para la sección B.

El reloj de la sección B es CL B . Los datos se registran en CL B . Y los datos retrasados por 16 relojes se seleccionan de Q 16B . NOSOTROS B , la habilitación de escritura está conectada a tierra.

Arriba también mostramos el mismo CD4517b cableado como un registro de desplazamiento de 64 bits para la sección independiente A.

El reloj de la sección A es CL A . Los datos ingresan en CL A . Los datos retrasados por pulsos de 64 relojes se obtienen de Q 64A . NOSOTROS A , la habilitación de escritura para la sección A, está conectada a tierra.

HOJAS DE TRABAJO RELACIONADAS:

- Hoja de trabajo de registros de turnos

Tecnología Industrial

- Protocolos de red

- ¿Por qué digital?

- Microprocesadores

- Datos del amplificador operacional

- La fabricación basada en datos está aquí

- Poniendo tus datos a trabajar

- ¿Qué es IIoT?

- Digitalización de Instalaciones de Producción

- Big Data vs Inteligencia Artificial

- Códigos de matriz de datos frente a códigos QR

- ¿Qué son los datos de mantenimiento?