La optimización de la ingeniería espaciadora para DRAM sin condensador basada en el transistor de túnel de doble puerta

Resumen

La DRAM basada en el FET de túnel de doble puerta (DGTFET) tiene las ventajas de una estructura sin condensador y un alto tiempo de retención. En este artículo, la herramienta Silvaco-Atlas investiga sistemáticamente la optimización de la ingeniería del espaciador para DGTFET DRAM para mejorar aún más su rendimiento, incluida la reducción de la lectura de corriente "0" y la extensión del tiempo de retención. Los resultados de la simulación muestran que los espaciadores en los lados de la fuente y el drenaje deben aplicar los dieléctricos de baja k y alta k, respectivamente, lo que puede mejorar la lectura de corriente "1" y reducir la lectura de corriente "0". Aplicando esta ingeniería de espaciador optimizada, la DRAM DGTFET obtiene el rendimiento óptimo:corriente de lectura extremadamente baja "0" (10 −14 A / μm) y un gran tiempo de retención (10 s), lo que reduce su consumo de energía estática y su frecuencia de actualización dinámica. Y la corriente de lectura baja "0" también mejora su relación de corriente (10 7 ) de la lectura "1" a la lectura "0". Además, el análisis sobre escalabilidad revela su deficiencia inherente, que ofrece la dirección de investigación adicional para DGTFET DRAM.

Antecedentes

Con la reducción de la geometría del dispositivo, la memoria de acceso aleatorio dinámico (DRAM) de 1 transistor (1T) –1 capacitor (1C) ha tenido dificultades para reducir su tamaño, ya que es difícil que el capacitor reduzca su tamaño [1,2,3] . La industria de la memoria ha propuesto algunos métodos efectivos para el empaquetado de memoria de mayor densidad, como nuevos materiales y estructuras de dispositivos novedosas [4, 5]. La DRAM de 1T con estructura sin condensador se informó por primera vez a principios de los años 90 [6, 7] y atrae cada vez más la atención. En 1T DRAM, el estado 1 (almacenamiento de portadora) se logra de cuatro formas:ionización de impacto [8], transistor de unión bipolar [9], tunelización banda a banda (BTBT) [10] y tunelización de puerta [11].

El transistor de efecto de campo de efecto túnel (TFET) basado en el BTBT ha sido considerado como una alternativa potencial para MOSFET debido a la relación de conmutación más alta y la corriente de estado apagado extremadamente baja [12,13,14]. Las ventajas de TFET (baja corriente en estado inactivo y dependencia débil de la temperatura) son extraordinariamente beneficiosas para la DRAM. Especialmente, la baja corriente en estado apagado puede reducir la lectura de corriente "0" y el consumo de energía estática. En la actualidad, hay algunos grupos que trabajan en la investigación de TFET DRAM [15,16,17,18,19,20]. Se informa que TFET DRAM tiene una corriente de lectura baja "0" y un tiempo de retención alto (RT). Entre estas DRAM TFET, la DRAM TFET de doble puerta (DGTFET) es la más destacada [19, 20]. En DGTFET DRAM, tanto las operaciones de escritura como de lectura se basan en BTBT. La investigación muestra que la lectura de corriente "0" de la DRAM DGTFET puede alcanzar 1 nA / μm, que es mucho menos que la de la DRAM 1T1C tradicional. Y el RT de 2 s es muy superior al valor objetivo de 64 ms que generalmente se establece en el tiempo de actualización dinámica en el sistema informático [21]. El RT de DGTFET DRAM es aún mayor de 300 ms cuando la temperatura se eleva a 85 ° C, lo que autoriza su viabilidad en las duras condiciones. Además, en DGTFET DRAM, la eliminación del condensador de mayor tamaño también exhibe su competitividad en empaques de alta densidad. Estas ventajas indican plenamente que es necesario estudiar DGTFET DRAM. Aunque estas investigaciones han demostrado que DGTFET tiene un rendimiento superior a la DRAM 1T1C convencional, los resultados (RT y corriente de lectura "0") no son óptimos debido a que la configuración del dispositivo de DGTFET no está optimizada.

En este artículo, la ingeniería del espaciador de DGTFET está optimizada para que DGTFET obtenga el rendimiento óptimo. En TFET, los dieléctricos espaciadores tienen una fuerte influencia en BTBT [22, 23]. En DGTFET, los espaciadores en los lados de la fuente y el drenaje están cerrados a las uniones de túneles, por lo que afectan en gran medida el rendimiento de DGTFET DRAM. Este artículo analiza sistemáticamente las influencias del dieléctrico del espaciador (dieléctricos de baja o alta k) en cada espaciador en DGTFET DRAM y propone una ingeniería de espaciador optimizada. Mediante la optimización de la ingeniería del espaciador, la lectura de corriente "0" se reduce a 10 −14 A / μm y RT pueden alcanzar los 10 s. Finalmente, la escalabilidad de DGTFET DRAM con la ingeniería de espaciador optimizada también se analiza en este trabajo.

Estructura del dispositivo y método de simulación

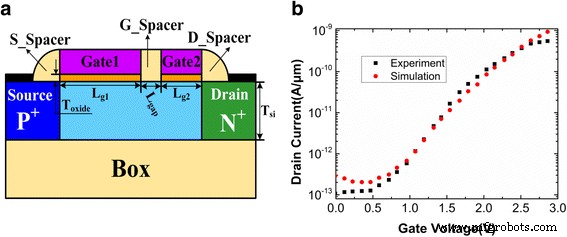

El DGTFET con una configuración P-I-N se ilustra en la Fig. 1a. Las regiones de origen y drenaje son P + dopaje (10 20 / cm 3 ) y N + dopaje (10 20 / cm 3 ), respectivamente. La región del canal intrínseco se divide en dos partes:la región Gate1 con N + polisilicio y la región Gate2 con P + polisilicio. Hay un pequeño espacio entre Gate1 y Gate2. El P + polysilicon Gate2 puede crear y mantener el pozo físico para el almacenamiento de carga y reemplazar la DRAM convencional basada en TFET que utiliza un P + región de bolsillo como área de almacenamiento. Mientras que para un N + polisilicio Gate1, la concentración de orificios en la región del traslapo entre Gate1 y Gate2 es baja, lo que es útil para la operación de lectura. Por lo tanto, una P + Se ha optado por polysilicon Gate2 para crear una región de almacenamiento más profunda que podría facilitar un tiempo de retención más prolongado, mientras que un N + El polisilicio Gate1 se selecciona para controlar el mecanismo de tunelización durante la operación de lectura [20]. En la Fig. 1a, S_Spacer y D_Spacer se refieren a los espaciadores en los lados de la fuente y del drenaje, respectivamente. El G_spacer se refiere al espaciador entre Gate1 y Gate2. El material predeterminado de los espaciadores es SiO 2 . Los parámetros predeterminados del dispositivo son los siguientes:espesor de la película de silicona (T si ) es de 20 nm, la longitud de Gate1 (L g1 ) es de 400 nm, longitud de Gate2 (L g2 ) es de 200 nm, la longitud del espacio de la puerta (L gap ) es de 50 nm y el espesor del óxido de puerta HfO 2 (T óxido ) es de 3 nm.

un Esquema de la celda DRAM TFET (DGTFET) de doble puerta. b Comparación entre la característica de transferencia simulada con resultados experimentales para SOI TFET [25]

Las simulaciones del DGTFET DRAM se llevan a cabo en Silvaco Atlas utilizando un modelo BTBT no local. El modelo de tunelización BTBT no local tiene en cuenta la variación espacial de las bandas de energía y la generación / recombinación del tipo de portador opuesto [24]. Los parámetros del modelo de tunelización se calibran de acuerdo con los resultados experimentales de SOI TFET [25]. La masa del túnel de electrones y huecos se ajusta a 0,22 m 0 y 0,52 m 0 , respectivamente, donde m 0 es la masa en reposo del electrón. La característica de transferencia simulada de SOI TFET es consistente con los resultados experimentales, como se muestra en la Fig. 1b, que autoriza los modelos aplicados en este trabajo. Debido al fuerte dopaje en las regiones de origen y drenaje, también se consideran el modelo de estrechamiento de la brecha de banda y las estadísticas de Fermi-Dirac. Además, también se aplican la recombinación Shockley-Read-Hall, así como los modelos de movilidad dependiente del dopaje y del campo eléctrico. Todos los parámetros del modelo son consistentes con los de [19, 20]. Debido a que la vida útil de la portadora gobierna la generación / recombinación de la portadora durante la operación de retención, influye en el RT de DGTFTET DRAM. De acuerdo con los diferentes tiempos de vida de los portadores que varían entre 1 μs y 10 ns en [26,27,28], los tiempos de vida de los electrones y los huecos se establecen en 100 ns. La relación Scharfetter y los modelos Schenk se utilizan para incluir la dependencia del dopaje y la temperatura durante la vida útil, respectivamente.

Resultados y discusión

Mecanismo operativo

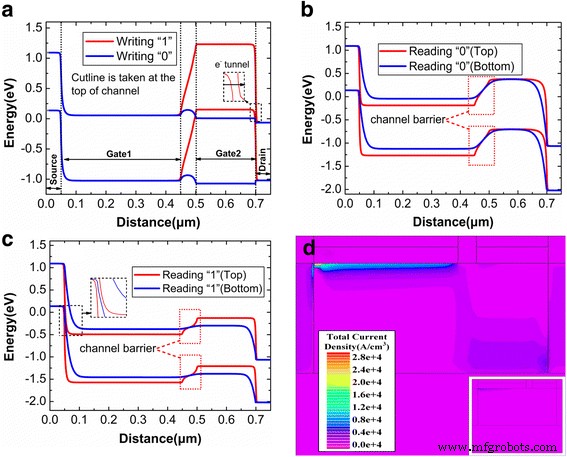

En DGTFET DRAM, las operaciones de escritura y lectura están controladas por BTBT en las uniones de túnel de drenaje y fuente, respectivamente. La Figura 2 muestra las bandas de energía durante las diferentes operaciones. Como se muestra en la Fig. 2a, durante la escritura "1", la puerta 2 con un sesgo negativo coloca significativamente la banda de energía del canal debajo de la puerta 2 de modo que se crea una barrera de túnel extremadamente pequeña en el lado del drenaje. Por lo tanto, los electrones hacen un túnel hacia el lado del drenaje y los agujeros se acumulan en el pozo de potencial profundo (1.2 V), como se muestra en la Fig. 3a. Durante la escritura "0", el Gate2 con un sesgo positivo hace que los agujeros se expulsen de este pozo de potencial y se recombinen en el lado del drenaje [29]. La Figura 2b, c muestra las bandas de energía después de leer "1" y "0", respectivamente. La Figura 2b ilustra que hay una barrera de canal entre Gate1 y Gate2, pero esta no existe en la parte inferior del canal. Además, la distancia de túnel en el lado de la fuente es menor en la parte superior del canal. Esto demuestra que se forma una ruta de conducción inclinada (desde la interfaz frontal para Gate1 hasta la interfaz trasera para Gate2) durante la lectura “1”, lo que también puede demostrarse mediante la densidad de corriente de la Fig. 2d. Durante la lectura "0", la barrera de canal obvia se puede encontrar en la Fig. 2c, que restringe la lectura "0" de corriente. El recuadro de la Fig. 2d muestra que los electrones que forman un túnel desde la región de la fuente no pueden cruzar esta barrera de canal para formar la corriente de lectura más alta "0".

Bandas de energía desde la fuente hasta el drenaje. un Bandas de energía después de escribir "1" con sesgo Gate2 negativo y después de escribir "0" con sesgo Gate2 positivo. b Bandas de energía en la parte superior e inferior del canal después de leer "1". c Bandas de energía en la parte superior e inferior del canal después de leer "0". d Densidad de corriente total después de leer "1"

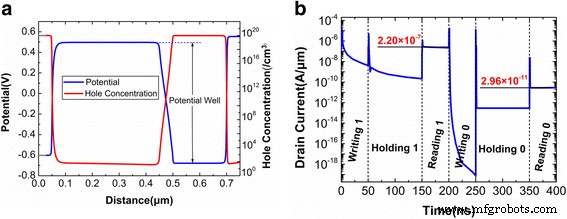

un Potencial y concentración de agujeros en la superficie del canal después de escribir “1”. b Respuesta transitoria de la corriente de drenaje para DGTFET DRAM operada en la Tabla 1

Una condición de programación adecuada es importante para DGTFET DRAM. Se debe aplicar un sesgo negativo mayor en Gate2 para que el BTBT saturado se induzca durante la escritura "1". Durante la celebración de "1", se aplica un pequeño sesgo negativo en la puerta 2 para retener los agujeros en el pozo potencial durante mucho tiempo. Para las operaciones de lectura, el mayor sesgo de Gate1 fortalece el BTBT durante la lectura "1", pero es perjudicial para la lectura de corriente "0". El Gate2 con el sesgo apropiado no solo puede mejorar la corriente de lectura "1" sino que también puede debilitar la corriente de lectura "0". Aplicando la condición de programación optimizada en la Tabla 1, la respuesta transitoria de DGTFET DRAM con los parámetros predeterminados se muestra en la Fig. 3b. Los tiempos de escritura y lectura, así como los tiempos de espera, se establecen en 50 ns y 100 ns, respectivamente. La relación actual obtenida de la lectura "1" a la lectura "0" es aproximadamente 10 4 , que es el mismo que en [17, 19, 20].

Impacto de los dieléctricos espaciadores

En DGTFET DRAM, el uso de dieléctricos low-k o high-k en tres espaciadores (S_Spacer, G_Spacer y D_Spacer) influirá en su rendimiento. En este diseño, los dieléctricos low-k y high-k eligen el SiO 2 y HfO 2 , respectivamente. Si cada espaciador usa SiO 2 o HfO 2 , habrá ocho combinaciones de ingeniería de espaciadores. Para un análisis más completo, las propiedades de rendimiento de DGTFET DRAM con cada combinación, incluida la lectura "1" ( I 1 ) y "0" ( I 0 ) corrientes, así como la relación de corriente ( I 1 / Yo 0 ), se extraen de las respuestas transitorias, como se muestra en la Tabla 2. Para evaluar el RT, estos parámetros también se extraen cuando el tiempo de espera se incrementa a 2 s, lo cual se discutirá en las siguientes secciones. En la Tabla 2, las letras "S" y "H" representan SiO 2 y HfO 2 , respectivamente, y tres letras de cada abreviatura representan respectivamente S_Spacer, G_Spacer y D_Spacer.

De la Tabla 2, se puede seleccionar la ingeniería de espaciador óptima. El yo 1 son aproximadamente 10 −7 A / μm y 10 −9 A / μm cuando el SiO 2 y HfO 2 se utilizan en S_Spacer, respectivamente. Cuando el D_Spacer aplica el HfO 2 , el yo 0 es bajo a aproximadamente 10 −14 A / μm. Por lo tanto, la configuración óptima del espaciador de DGTFET DRAM es que se deben usar dieléctricos de baja k y alta k en los lados de la fuente y del drenaje. Las razones específicas se analizarán sistemáticamente en las siguientes secciones.

Impactos del dieléctrico S_Spacer

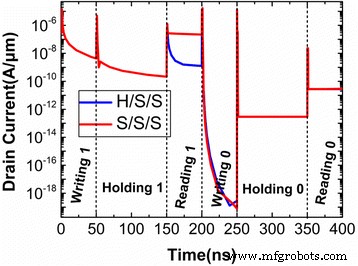

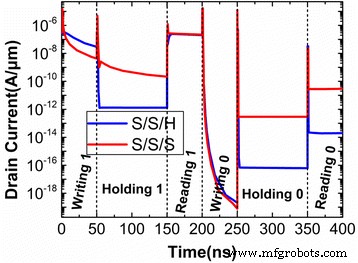

Para analizar las influencias de S_Spacer, las respuestas transitorias de las corrientes de drenaje para H / S / S y S / S / S se comparan en la Fig. 4. Se puede observar que la lectura "1" de la corriente se mejora en aproximadamente dos órdenes de magnitud cuando el SiO 2 se elige como el dieléctrico S_Spacer.

Respuestas transitorias de las corrientes de drenaje para H / S / S y S / S / S operadas en la Tabla 1

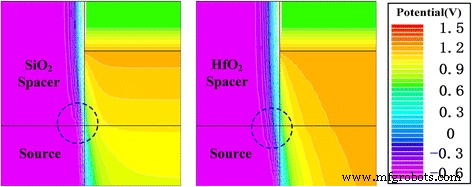

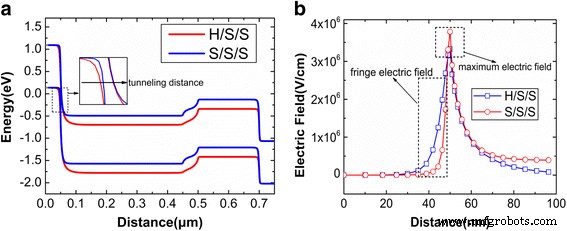

La Figura 5 muestra los contornos potenciales de S / S / S y H / S / S. En la unión de túnel de origen, la región de agotamiento de la superficie de H / S / S se extiende obviamente en comparación con la de S / S / S, como se muestra en el círculo de la Fig. 5. La región de agotamiento de la superficie extendida aumenta el ancho de la barrera de túnel. La Figura 6a muestra las bandas de energía después de leer "1". Como se muestra en la región local ampliada de esta figura, la distancia de túnel (ver las flechas) de H / S / S es obviamente mayor que la de S / S / S, que es causada por la región de agotamiento de la superficie extendida. Además, después de leer "1", el campo eléctrico en la parte superior de la unión de túnel de la fuente se muestra en la Fig. 6b. Se puede encontrar que el campo eléctrico marginal de H / S / S es mayor que el de S / S / S, que es la razón principal de la extensión de la región de agotamiento de la superficie. En una palabra, S_Spacer con high-k (HfO 2 ) el dieléctrico genera el campo eléctrico de franja más grande de modo que se extiende la región de agotamiento de la superficie en la unión de tunelización de la fuente, lo que aumenta la distancia de tunelización de los electrones y disminuye la lectura “1” de corriente. Además, también se puede encontrar en la Fig. 6b que el campo eléctrico máximo de S / S / S es mayor que el de H / S / S. La relación exponencial entre la tasa BTBT y el campo eléctrico hace que la corriente de túnel de S / S / S sea mucho mayor que la de H / S / S [30]. Por lo tanto, el S_Spacer con el dieléctrico low-k (SiO 2 ) es beneficioso para la lectura actual "1".

Contornos potenciales de S / S / S (izquierda) y H / S / S (derecha) después de leer "1"

un Banda de energía desde la fuente hasta el drenaje y b campo eléctrico en la parte superior de la unión de túnel de la fuente

En la Fig. 6a, el dieléctrico S_Spacer también provoca el impacto en la banda de energía de la región del canal. En la Fig. 6b, el campo eléctrico de S / S / S es mayor en la región del canal, por lo que su potencial de canal es menor que el de H / S / S. Como resultado, el nivel de energía más alto se puede encontrar en S / S / S. Pero esto no puede tener efectos sobre la barrera de túnel y la lectura de corriente "1".

Impactos del dieléctrico D_Spacer

Posteriormente, el D_Spacer también se investiga en este documento. Manteniendo constante S_Spacer y G_Spacer (SiO 2 se utiliza en estos dos espaciadores), las diferentes corrientes de drenaje transitorias causadas por los diferentes dieléctricos D_Spacer se ilustran en la Fig. 7. Aparte de la lectura "1" y la escritura "0", las otras operaciones tienen una dependencia obvia del dieléctrico D_Spacer. Esto se debe a que D_Spacer está lejos de la ruta de conducción de lectura "1" (parte inferior del canal debajo de Gate2). Se puede aprender del mecanismo operativo anterior que las operaciones de escritura y retención están gobernadas por Gate2, por lo que el dieléctrico D_Spacer puede influir en estas dos operaciones.

Respuestas transitorias de las corrientes de drenaje para S / S / H y S / S / S operadas en la Tabla 1

Durante la operación de retención, los agujeros acumulados durante la escritura "1" se eliminan del pozo de potencial y se recombinan en el lado del drenaje. Entonces, la corriente de retención "1" proviene principalmente de la corriente de recombinación SRH. Debido a la mayor capacidad de control de Gate2 sobre el canal en S / S / S, S / S / S tiene la mayor tasa de recombinación y mantiene la corriente “1”. Pero es mucho menor que la corriente BTBT durante la lectura "1", por lo que la corriente de retención "1" más alta no se puede reflejar en la lectura de corriente "1".

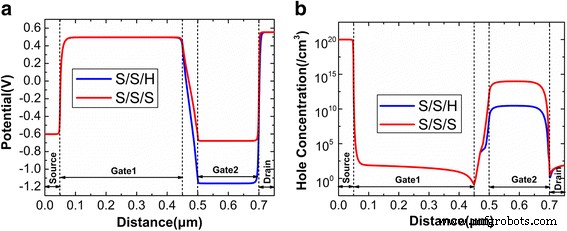

Durante la escritura "1", el dieléctrico D_Spacer influye significativamente en la profundidad del pozo potencial. El contorno de potencial en la Fig. 8a muestra que D_Spacer con HfO 2 El dieléctrico crea un pozo de potencial más profundo. Implica que el BTBT efectivo entre el drenaje y el canal se extiende a una región más profunda del canal. Por lo tanto, la corriente de escritura “1” de S / S / H es mayor que la de S / S / S. Durante el mantenimiento de "0", aunque se aplica una pequeña polarización negativa (- 0,2 V) en Gate2, también puede aumentar la banda de energía del canal debajo de Gate2, lo que induce el BTBT en el lado del drenaje. A través del análisis anterior, se puede conocer que D_Spacer con SiO 2 El dieléctrico mejora el BTBT en la unión de túnel de drenaje durante el mantenimiento de “0”, lo que puede demostrarse por la mayor concentración de orificios para S / S / S, como se muestra en la Fig. 8b. Por lo tanto, el D_Spacer con SiO 2 El dieléctrico da como resultado la corriente de retención más alta "0".

un Contorno potencial después de escribir “1”. b Concentración de agujeros después de mantener presionado "0"

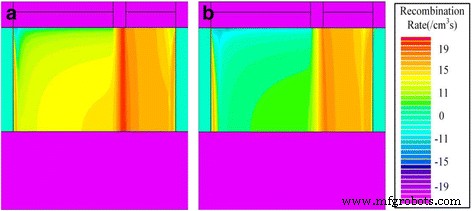

Durante la lectura "0", debido a que la barrera del canal entre Gate1 y Gate2 evita que los electrones fluyan hacia el lado del drenaje, la diferencia de lectura de la corriente "0" para S / S / H y S / S / S se debe principalmente a la corriente de recombinación . Cuantos más agujeros se acumulan durante el mantenimiento de "0" para S / S / S, por lo que la banda de energía descendente hace que la tasa de recombinación de S / S / S sea mayor que la de S / H / S durante la lectura "0", como se muestra en la Fig. 9. Como resultado, cuando el D_Spacer usando SiO 2 , la lectura de corriente "0" más alta debe atribuirse a la corriente de recombinación más alta, que es causada por los agujeros más acumulados durante el mantenimiento de "0".

Tasa de recombinación de a S / S / S y b S / S / H después de leer "0"

En resumen, la ingeniería de espaciador óptima para DGTFET DRAM es que los espaciadores en los lados de la fuente y el drenaje deben aplicar los dieléctricos de baja k y alta k, respectivamente. Puede verse en la Tabla 2 que G_Spacer no tiene influencia en DGTFET DRAM cuando los otros espaciadores se mantienen sin cambios. Esto se debe a que los BTBT que dominan las operaciones de escritura y lectura están libres de la influencia de G_Spacer.

Tiempo de retención

Como se explicó anteriormente, la recombinación y generación de huecos durante el mantenimiento de "1" y "0" degradan el estado "1" y "0", respectivamente. Como resultado, es necesario estudiar la degradación del rendimiento de DGTFET DRAM en el tiempo de retención más largo. En la Tabla 2, I 1 y yo 0 degradar en gran medida con el aumento del tiempo de espera. En todos los dispositivos, yo 1 / Yo 0 sigue siendo mayor que 10 4 para dispositivo con ingeniería de espaciador óptima (S / S / H y S / H / H) cuando el tiempo de retención aumenta a 2 s.

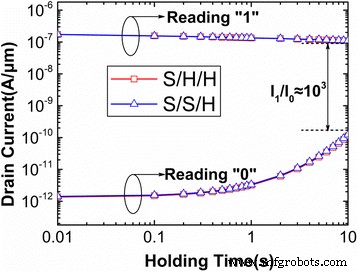

Generalmente, el tiempo de retención requerido para reducir el margen máximo de detección (diferencia entre I 1 y yo 0 ) en un 50% se evalúa como RT. En este diseño, un RT más estricto se define como el tiempo máximo de retención cuando el I 1 / Yo 0 es superior a 10 3 . La Figura 10 muestra la variación de la corriente de lectura con el tiempo de retención para S / S / H y S / H / H. Se puede encontrar que la relación actual de S / H / S y S / H / H es tan alta como 10 3 cuando el tiempo de espera se eleva a 10 s. Como resultado, el RT de DGTFET DRAM con ingeniería de espaciador óptima puede alcanzar los 10 s. Esto es mucho más alto que el valor objetivo de 64 ms. La Tabla 3 compara las propiedades de desempeño en este trabajo con las de [17,18,19,20]. En [19, 20], la razón actual es solo 10 2 , y el RT es mucho menor que 10 s. Además, la lectura de corriente “0” en este trabajo es dos órdenes de magnitud menor que la de [19, 20]. Los resultados del experimento sobre FD-SOI TFET DRAM también muestran que su lectura de corriente "0" y RT son inferiores a las de este trabajo. Este rendimiento superior muestra que DGTFET es un sustituto de la DRAM de baja potencia. La optimización de la ingeniería del espaciador hace que la DRAM DGTFET obtenga una corriente de lectura baja "0" y un RT alto, lo que es útil para la reducción del consumo de energía estática y dinámica.

Variación de la corriente de lectura con el tiempo de retención para S / S / H y S / H / H

Escalabilidad de DGTFET DRAM

Aunque la DRAM DGTFET resuelve el problema de la densidad de la celda de memoria debido a la eliminación del condensador con el gran tamaño, es necesario estudiar su escalabilidad. El objetivo de la escalabilidad es mantener el RT por encima de 2 s. La Tabla 4 extrae las propiedades de rendimiento de S / S / H con la disminución de L g1 , L g2 y L espacio . En la Tabla 4, los tres números de cada abreviatura representan L g1 , L espacio y L g2 .

De la Tabla 4, se puede observar que I 1 disminuye extremadamente cuando el L g1 se reduce a 100 nm desde 200 nm. La escala de L g1 más allá de 100 nm estrecha la barrera inducida por el tipo n, lo que resulta en una capacidad de control reducida de la puerta y una I degradada 1 . El yo 0 aumenta significativamente con la disminución de L g1 y L g2 . La reducción de L g2 disminuye el ancho de la barrera del canal entre Gate1 y Gate2, lo que promueve que una parte de los electrones cruce la barrera para formar el I más alto 0 . Además, la reducción continua de L g1 debilita la capacidad de Gate1 para restringir los electrones tunelizados en la superficie del canal durante la lectura "0". En la Tabla 4, la L espacio no tiene una influencia obvia en el yo 1 , pero el yo 0 aumenta ligeramente con la disminución de la L espacio . Reducir L espacio por debajo de 20 nm permite un túnel más alto hacia Gate2, degradando así el estado "0", reduciendo así el tiempo de retención.

Para asegurar que el I 1 / Yo 0 y el tiempo de retención es superior a 10 2 y 2 s, respectivamente, el mínimo de L g1 , L g2 y L espacio se consideran 200, 150 y 20 nm, respectivamente. Este tamaño mínimo de dispositivo es ligeramente menor que el de [17,18,19,20], como se muestra en la Tabla 3. Sin embargo, el tamaño mínimo de DRAM DGTFET es aún mayor que el de DRAM 1T1C de nodo de 20 nm / 18 nm [31 ], que es la deficiencia inherente de DGTFET DRAM. Pero sus ventajas de sin condensador, baja potencia y alta RT no pueden ignorarse con la ayuda de la optimización de la ingeniería de espaciadores. Reducir el tamaño de DGTFET DRAM más allá de 100 nm será el enfoque de nuestro trabajo en el futuro.

Conclusiones

En este trabajo, la optimización de la ingeniería de espaciadores para DGTFET DRAM es estudiada por la herramienta Silvaco-Atlas. Los espaciadores en los lados de la fuente y el drenaje tienen las principales influencias en el rendimiento de DGTFET DRAM. El campo eléctrico de franja agrandado por el espaciador de la fuente con HfO 2 hace que la región de agotamiento de la superficie se extienda en la unión de tunelización de la fuente, lo que disminuye la lectura “1” de corriente. Cuando el SiO 2 El dieléctrico se utiliza en el espaciador de drenaje, el BTBT más fuerte induce más agujeros mientras se mantiene "0", lo que mejora la corriente de recombinación durante la lectura "0". Por lo tanto, la ingeniería óptima del espaciador es que se deben usar dieléctricos de baja k y alta k en los espaciadores de drenaje y fuente, respectivamente. A través de la optimización de la ingeniería del espaciador, la DRAM DGTFET obtiene ventajas destacadas:corriente "0" de lectura extremadamente baja y mayor tiempo de retención (10 s) en comparación con otros trabajos relacionados. Además, el análisis sobre la escalabilidad revela que el tamaño mínimo de su dispositivo es aún mayor que el del último nodo 1T1C DRAM de 20 nm / 18 nm. Esta deficiencia inherente indica que reducir el tamaño de DGTFET DRAM más allá de 100 nm será el enfoque de nuestro trabajo para DGTFET DRAM en el futuro.

Abreviaturas

- DGTFET:

-

Transistor de efecto de campo de tunelización de doble puerta

- DRAM:

-

Memoria dinámica de acceso aleatorio

Nanomateriales

- El transistor de unión única (UJT)

- Ideas de proyectos basados en sensores para estudiantes de ingeniería de último año

- Principios de ingeniería de confiabilidad para el ingeniero de planta

- Los científicos de IBM inventan un termómetro para nanoescala

- El valor de la gestión de archivos y el corte en la nube para la impresión 3D

- Optimización de película fina altamente reflectante para micro-LED de ángulo completo

- El diseño de la capa de emisión para multiplicadores de electrones

- El Mejor Nivel de Optimización y Organización en la Fábrica Inteligente

- Cómo encontrar las soluciones de ingeniería personalizadas que está buscando

- La falta de diversidad puede ser la causa de la creciente brecha de habilidades de la industria

- ¡Gracias por los recuerdos!