La cadencia acelera la verificación de SoC de mil millones de puertas

Cadence Design Systems ha lanzado sus sistemas de emulación y creación de prototipos de próxima generación que, según dijo, ofrecen la validación de software y depuración de hardware previo al silicio más rápida y de mayor rendimiento para la verificación de mil millones de diseños de sistemas en chip (SoC) de compuertas.

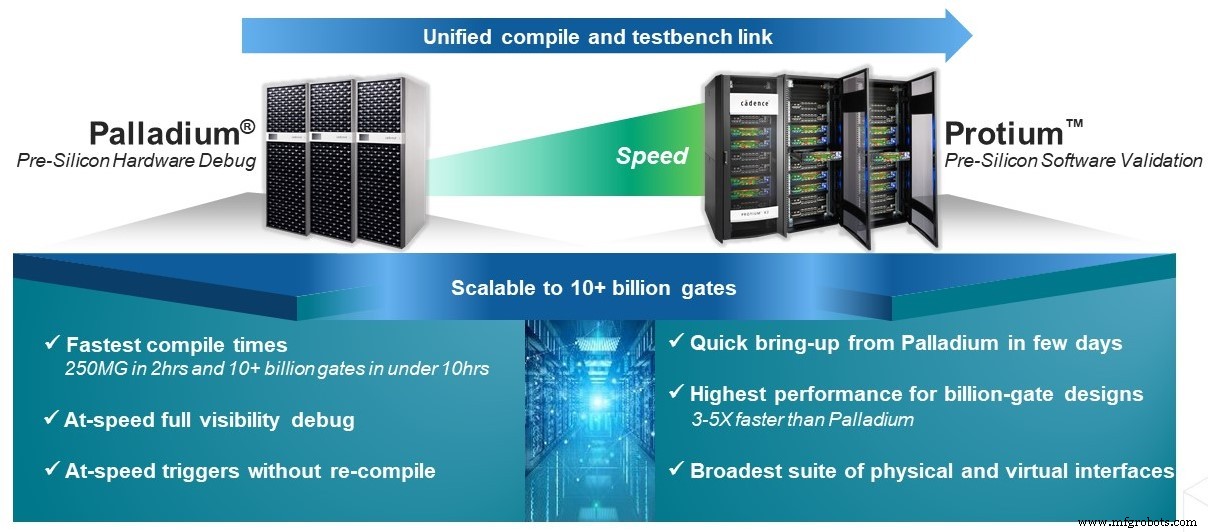

Con una interfaz de compilador unificada, así como interfaces de depuración comunes y contenido de banco de pruebas, la nueva emulación empresarial Palladium Z2 y los sistemas de creación de prototipos empresariales Protium X2 brindan a los clientes una capacidad 2X y mejoras de rendimiento 1.5X con respecto a sus predecesores, lo que permite ejecutar más ciclos de validación en chips más grandes. en menos tiempo. Cadence dijo que ambos sistemas también ofrecen una innovadora tecnología de compilación modular capaz de compilar 10 mil millones de puertas en menos de 10 horas en el sistema Palladium Z2 y en menos de 24 horas en el sistema Protium X2.

Una clave para la combinación Palladium Z2 / Protium X2, que son parte de la suite de verificación Cadence más amplia, incluidas las aplicaciones de verificación inteligente, es la interfaz unificada del compilador, lo que significa que un diseño que compila para Palladium se compilará y se ejecutará en Protium. Con el flujo perfectamente integrado, la depuración unificada, las interfaces físicas y virtuales comunes y el contenido del banco de pruebas en todos los sistemas, los dos sistemas ofrecen una rápida migración de diseño y pruebas desde la emulación hasta la creación de prototipos. La capacidad escalable significa que están diseñados para abordar los desafíos que enfrentan los que diseñan para las aplicaciones más avanzadas, incluidos los diseños informáticos móviles, de consumo y de hiperescala.

Paul Cunningham de Cadence dijo:"La verificación previa al silicio del diseño avanzado de SoC requiere una solución con una capacidad de miles de millones de puertas que ofrezca el mayor rendimiento y una depuración rápida y predecible". El vicepresidente senior y gerente general del grupo de sistemas y verificación agregó:“Nuestro nuevo dúo dinámico cumple estos requisitos con dos sistemas estrechamente integrados, la emulación Palladium Z2 optimizada para una depuración de hardware rápida y predecible y la creación de prototipos Protium X2 optimizada para un rendimiento multimillonario más alto. validación del software de la puerta. Estamos entusiasmados con el gran interés de los clientes y esperamos asociarnos con ellos para aprovechar estos nuevos sistemas y lograr el mayor rendimiento de verificación en sus diseños ”.

Los primeros clientes han comentado los beneficios del rendimiento de verificación de front-end común. En Nvidia, el director senior de ingeniería de hardware, Narendra Konda, dijo:“La complejidad de nuestros gráficos de alta gama y diseños de hiperescala aumenta con cada generación, mientras que nuestros horarios de comercialización se ajustan. Utilizando el flujo de interfaz común en los sistemas Cadence Palladium Z2 y Protium X2, estamos optimizando la distribución de la carga de trabajo entre la verificación, la validación y la activación del software previo al silicio. Con el doble de capacidad utilizable, un 50 por ciento más de rendimiento y una respuesta del compilador modular más rápida, podemos validar nuestros diseños de GPU y SoC más sofisticados de manera integral y según lo programado ”.

Mientras tanto, en Arm, el director senior de servicios de diseño, Tran Nguyen, dijo:“Las mejores emulaciones de su clase son clave para nuestro éxito, y Arm utiliza la emulación de manera extensiva junto con la simulación en servidores basados en Arm para lograr el mayor rendimiento de verificación. Con el nuevo sistema Cadence Palladium Z2, hemos visto una mejora de hasta un 50% en el rendimiento y una mejora del doble en la capacidad de nuestros últimos diseños, lo que nos proporciona las poderosas capacidades de pre-silicio necesarias para verificar nuestra IP y nuestros productos de próxima generación ”.

Al igual que sus predecesores, Palladium Z2 y Protium X2 están construidos con una configuración de rack estándar y están pensados para instalarse dentro de un centro de datos y acceder a ellos desde el escritorio de los ingenieros. Ambos pueden manejar muchos diseños al mismo tiempo, dependiendo de la capacidad que realmente requieran los diseños individuales. La granularidad que se puede compartir está en el chip individual dentro del sistema, y ambos sistemas se escalan para que cada chip individual se pueda usar en paralelo para un diseño diferente:

- Palladium Z2 escala desde un chip con 8 millones de puertas y puede tener hasta 144 trabajos simultáneos por rack. O puede escalar a 18,4 mil millones de puertas por rack si todo el rack se utiliza para un solo diseño. Más allá de eso, se pueden usar hasta 12 racks para un solo diseño y escalar hasta 18,4 mil millones de puertas.

- Un rack completo de Protium X2 contiene 60 FPGA y tenemos clientes que ejecutan 60 trabajos en paralelo. Dado que un solo FPGA en Protium X2 tiene ~ 40 millones de puertas, estos no son diseños pequeños. Todo el bastidor se puede utilizar para un diseño único de 2.400 millones de puertas. O, como con Palladium Z2, un diseño grande se puede escalar aún más en varios estantes.

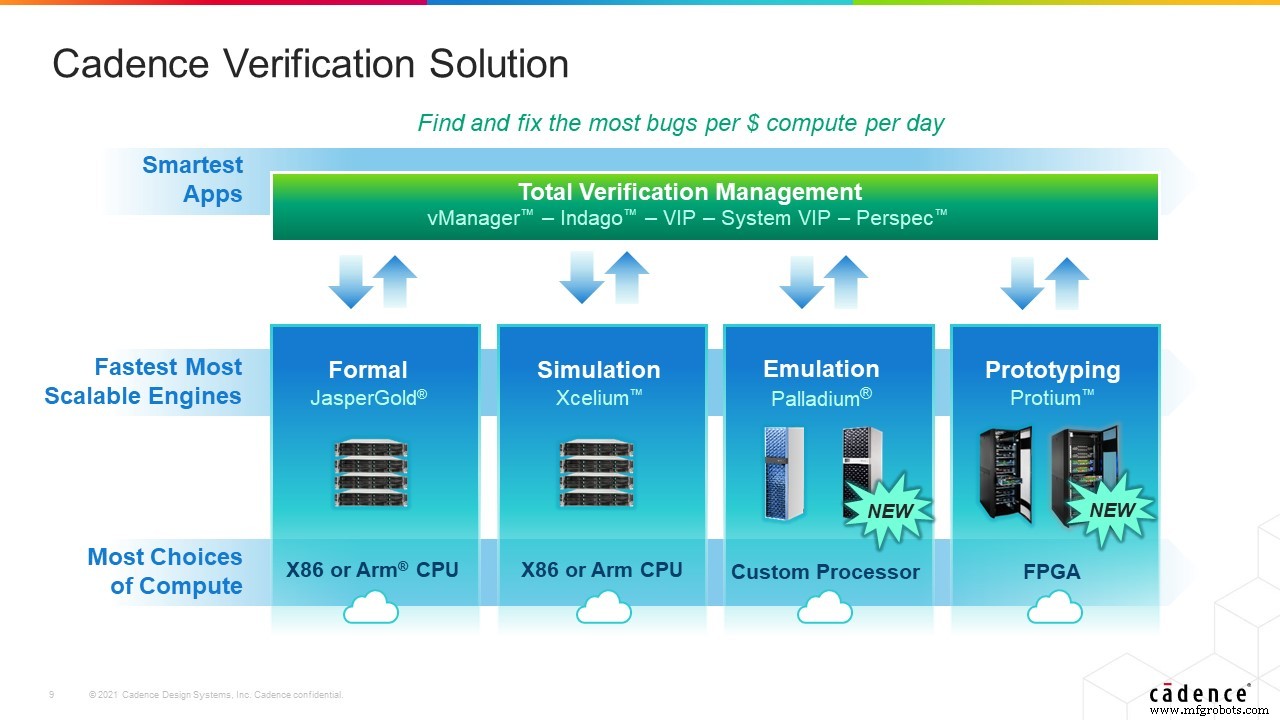

El flujo completo de verificación de Cadence, que incluye la emulación Palladium Z2, la creación de prototipos Protium X2, la simulación lógica Xcelium, la plataforma de verificación formal JasperGold y el conjunto de aplicaciones de verificación inteligente Cadence, ofrece el mayor rendimiento de verificación de errores por dólar por día, según la compañía.

Incrustado

- Sistemas de numeración

- Universalidad de la puerta

- Tiristores

- Sistemas de señales actuales

- ¿Por qué un desarrollador bare-metal se mudó a sistemas operativos

- Cadence anuncia el programa de socios de Cloud Passport

- SoC aumenta el rendimiento de los wearables

- La placa del sensor inteligente acelera el desarrollo de la IA de borde

- Modelado de nivel de puerta

- Hitachi adquirirá el integrador de sistemas robóticos JR Automation por 1400 millones de dólares

- ABB reclama el 20 por ciento del mercado de sistemas de control distribuido de $14 mil millones