Niveles de voltaje de la señal lógica

Voltajes de entrada para puertas lógicas

Los circuitos de compuerta lógica están diseñados para ingresar y emitir solo dos tipos de señales:"alta" (1) y "baja" (0), representada por un voltaje variable:voltaje de suministro de energía completo para un estado "alto" y voltaje cero para un estado "bajo". En un mundo perfecto, todas las señales del circuito lógico existirían en estos límites extremos de voltaje y nunca se desviarían de ellos (es decir, menos del voltaje total para un voltaje "alto" o más de cero para un voltaje "bajo").

Sin embargo, en realidad, los niveles de voltaje de la señal lógica rara vez alcanzan estos límites perfectos debido a las caídas de voltaje parásitas en los circuitos del transistor, por lo que debemos comprender las limitaciones del nivel de señal de los circuitos de puerta cuando intentan interpretar los voltajes de señal que se encuentran en algún lugar entre voltaje de suministro completo y cero.

Tolerancia de voltaje de las entradas de puerta TTL

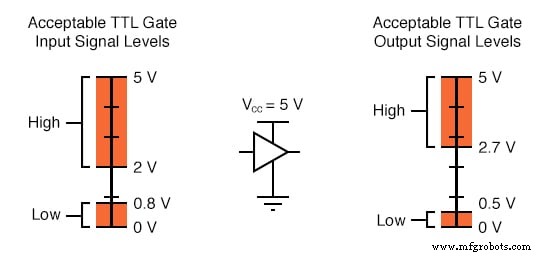

Las puertas TTL operan con un voltaje de suministro de energía nominal de 5 voltios, +/- 0,25 voltios. Idealmente, una señal TTL "alta" sería exactamente de 5,00 voltios y una señal TTL "baja" de 0,00 voltios exactamente.

Sin embargo, los circuitos de compuerta TTL reales no pueden generar niveles de voltaje tan perfectos y están diseñados para aceptar señales "altas" y "bajas" que se desvían sustancialmente de estos valores ideales.

Los voltajes de señal de entrada "aceptables" varían de 0 voltios a 0,8 voltios para un estado lógico "bajo" y de 2 voltios a 5 voltios para un estado lógico "alto".

Los voltajes de señal de salida "aceptables" (niveles de voltaje garantizados por el fabricante de la puerta en un rango específico de condiciones de carga) varían de 0 voltios a 0,5 voltios para un estado lógico "bajo" y de 2,7 voltios a 5 voltios para un estado lógico "alto" :

Si se enviara una señal de voltaje entre 0,8 voltios y 2 voltios a la entrada de una puerta TTL, no habría una respuesta segura de la puerta. Tal señal se consideraría incierta , y ningún fabricante de puertas lógicas garantizaría cómo su circuito de puertas interpretaría dicha señal.

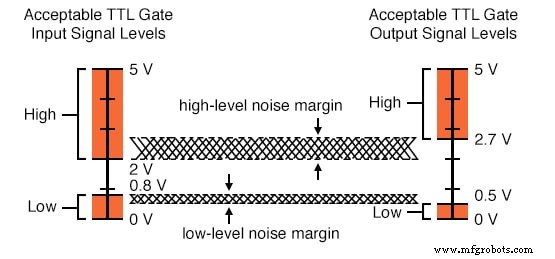

Margen de ruido TTL

Como puede ver, los rangos tolerables para los niveles de señal de salida son más estrechos que para los niveles de señal de entrada, para garantizar que cualquier puerta TTL que emita una señal digital a la entrada de otra puerta TTL transmita voltajes aceptables a la puerta receptora. La diferencia entre los rangos de entrada y salida tolerables se denomina margen de ruido de la puerta.

Para las puertas TTL, el margen de ruido de bajo nivel es la diferencia entre 0,8 voltios y 0,5 voltios (0,3 voltios), mientras que el margen de ruido de alto nivel es la diferencia entre 2,7 voltios y 2 voltios (0,7 voltios). En pocas palabras, el margen de ruido es la cantidad máxima de voltaje espurio o de "ruido" que puede superponerse a una señal de voltaje de salida de puerta débil antes de que la puerta receptora lo interprete incorrectamente:

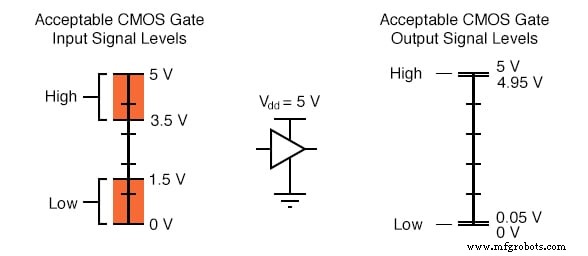

Tolerancia de voltaje de las entradas de puerta CMOS

Los circuitos de puerta CMOS tienen especificaciones de señal de entrada y salida que son bastante diferentes de TTL. Para una puerta CMOS que funciona con un voltaje de suministro de energía de 5 voltios, los voltajes de señal de entrada aceptables varían de 0 voltios a 1,5 voltios para un estado lógico "bajo" y de 3,5 voltios a 5 voltios para un estado lógico "alto".

Los voltajes de señal de salida "aceptables" (niveles de voltaje garantizados por el fabricante de la puerta en un rango específico de condiciones de carga) varían de 0 voltios a 0.05 voltios para un estado lógico "bajo" y de 4.95 voltios a 5 voltios para un estado lógico "alto" :

Margen de ruido CMOS

Debería ser obvio a partir de estas cifras que los circuitos de compuerta CMOS tienen márgenes de ruido mucho mayores que TTL:1,45 voltios para márgenes CMOS de nivel bajo y alto, frente a un máximo de 0,7 voltios para TTL. En otras palabras, los circuitos CMOS pueden tolerar más del doble de la cantidad de voltaje de "ruido" superpuesto en sus líneas de entrada antes de que se produzcan errores de interpretación de la señal.

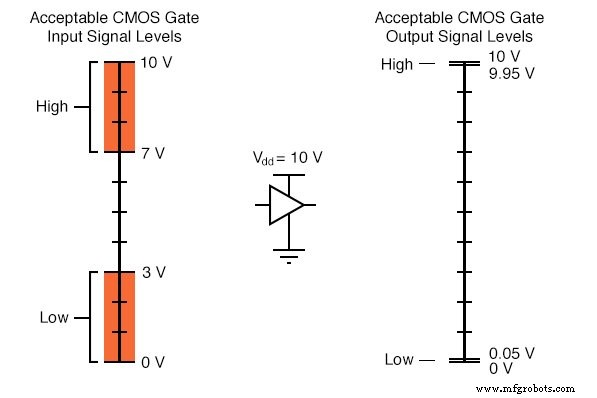

Márgenes de ruido a voltajes operativos más altos

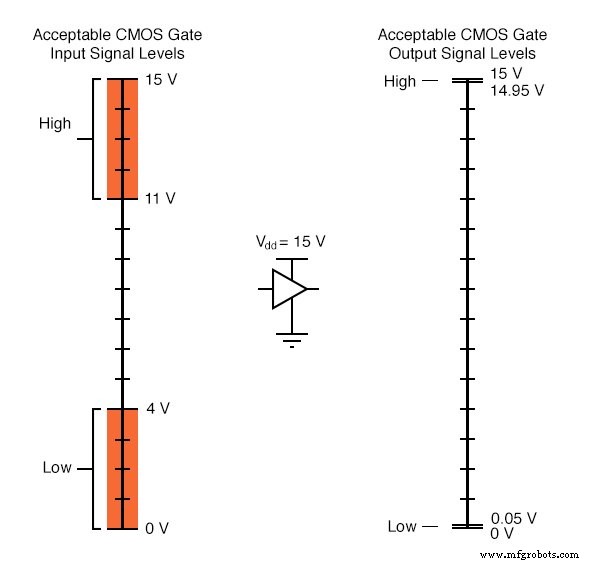

Los márgenes de ruido CMOS se amplían aún más con voltajes operativos más altos. A diferencia de TTL, que está restringido a un voltaje de suministro de energía de 5 voltios, el CMOS puede ser alimentado por voltajes de hasta 15 voltios (algunos circuitos CMOS de hasta 18 voltios).

Aquí se muestran los estados aceptables "alto" y "bajo", tanto para la entrada como para la salida, de los circuitos integrados CMOS que operan a 10 voltios y 15 voltios, respectivamente:

Los márgenes para las señales aceptables “altas” y “bajas” pueden ser mayores que lo que se muestra en las ilustraciones anteriores. Lo que se muestra representa el rendimiento de la señal de entrada en el "peor de los casos", según las especificaciones del fabricante. En la práctica, se puede encontrar que un circuito de puerta tolerará señales "altas" de voltaje considerablemente menor y señales "bajas" de voltaje considerablemente mayor que las especificadas aquí.

Por el contrario, los márgenes de salida extremadamente pequeños que se muestran, que garantizan estados de salida para señales "altas" y "bajas" dentro de 0.05 voltios de los "rieles" de la fuente de alimentación, son optimistas. Tales niveles de voltaje de salida “sólidos” serán verdaderos solo para condiciones de carga mínima. Si la puerta está generando o absorbiendo una corriente sustancial a una carga, el voltaje de salida no podrá mantener estos niveles óptimos, debido a la resistencia del canal interno de los MOSFET de salida final de la puerta.

Umbrales de voltaje

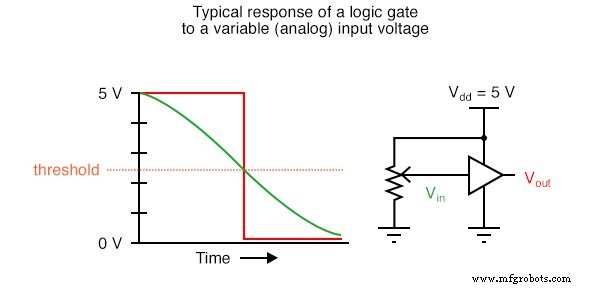

Dentro del rango "incierto" para cualquier entrada de puerta, habrá algún punto de demarcación que dividirá el rango de señal de entrada "baja" real de la puerta de su rango de señal de entrada "alta" real. Es decir, en algún lugar entre el nivel de voltaje de señal "alto" más bajo y el nivel de voltaje de señal "bajo" más alto garantizado por el fabricante de la puerta, hay un voltaje de umbral en el que la puerta realmente cambie su interpretación de una señal de "baja" o "alta" o viceversa. Para la mayoría de los circuitos de puerta, este voltaje no especificado es un solo punto:

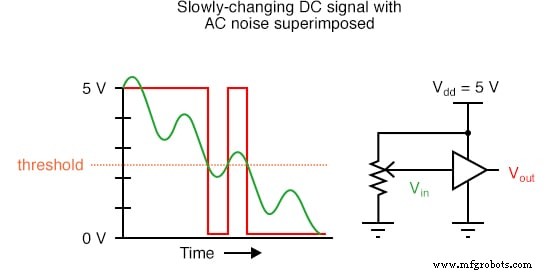

Entradas con ruido de CA

En presencia de voltaje de "ruido" de CA superpuesto a la señal de entrada de CC, un único punto de umbral en el que la puerta altera su interpretación del nivel lógico dará como resultado una salida errática:

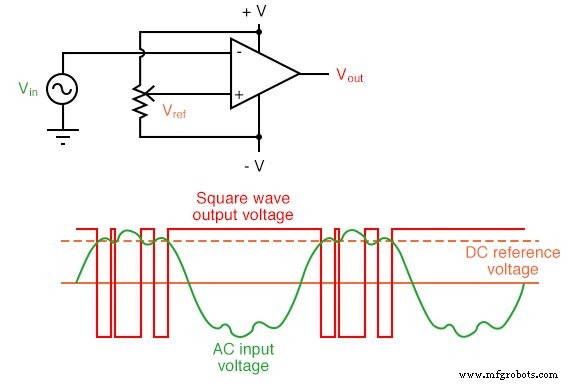

Si este escenario le resulta familiar, es porque recuerda un problema similar con los circuitos del amplificador operacional del comparador de voltaje (analógico). Con un solo punto de umbral en el que una entrada hace que la salida cambie entre los estados "alto" y "bajo", la presencia de ruido significativo provocará cambios erráticos en la salida:

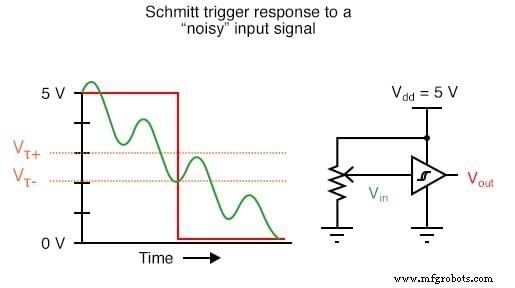

Activador Schmittt

La solución a este problema es un poco positiva retroalimentación introducida en el circuito amplificador. Con un amplificador operacional, esto se hace conectando la salida de vuelta a la entrada no inversora (+) a través de una resistencia.

En un circuito de puerta, esto implica rediseñar el circuito de puerta interno, estableciendo la retroalimentación dentro del paquete de puerta en lugar de a través de conexiones externas. Una puerta así diseñada se llama disparador Schmitt . Los disparadores Schmitt interpretan los voltajes de entrada variables de acuerdo con dos voltajes de umbral:un positivo umbral (VT +) y un negativo umbral (VT-):

Histéresis en puertas de activación Schmitt

Las compuertas de disparo de Schmitt se distinguen en los diagramas esquemáticos por el pequeño símbolo de "histéresis" dibujado dentro de ellas, que recuerda la curva B-H de un material ferromagnético. La histéresis engendrada por la retroalimentación positiva dentro del circuito de la puerta agrega un nivel adicional de inmunidad al ruido al rendimiento de la puerta.

Las puertas de disparo Schmitt se utilizan con frecuencia en aplicaciones donde se espera ruido en las líneas de señal de entrada y / o donde una salida errática sería muy perjudicial para el rendimiento del sistema.

Uso de tecnologías TTL y CMOS en el mismo sistema

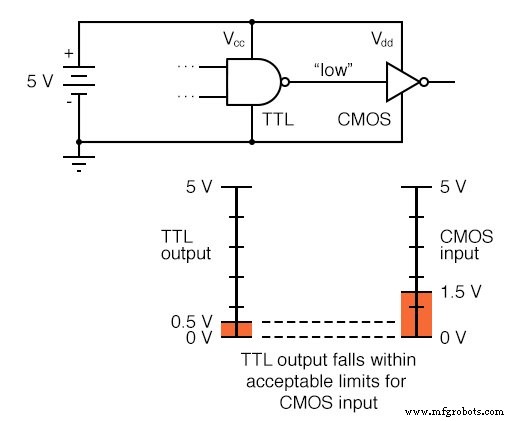

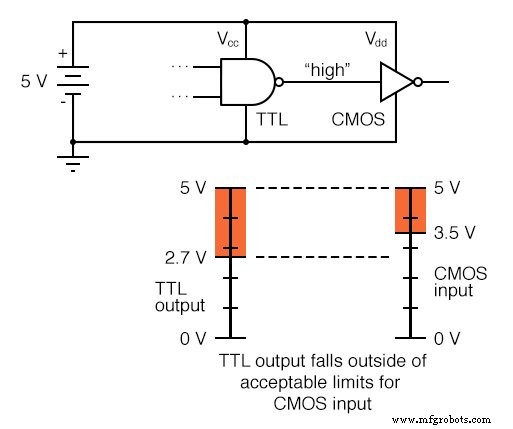

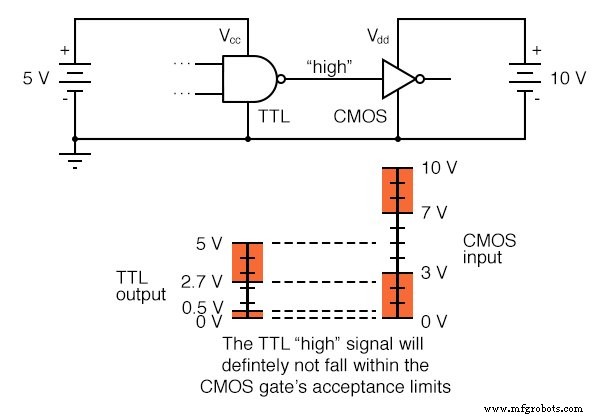

Los diferentes requisitos de nivel de voltaje de la tecnología TTL y CMOS presentan problemas cuando los dos tipos de puertas se utilizan en el mismo sistema. Aunque operar puertas CMOS con el mismo voltaje de fuente de alimentación de 5,00 voltios requerido por las puertas TTL no es un problema, los niveles de voltaje de salida TTL no serán compatibles con los requisitos de voltaje de entrada CMOS.

Ejemplo de circuito de combinación TTL y CMOS

Tomemos, por ejemplo, una puerta TTL NAND que envía una señal a la entrada de una puerta de inversor CMOS. Ambas puertas funcionan con el mismo suministro de 5,00 voltios (V cc ). Si la puerta TTL emite una señal "baja" (garantizada entre 0 voltios y 0,5 voltios), la entrada de la puerta CMOS la interpretará correctamente como "baja" (esperando un voltaje entre 0 voltios y 1,5 voltios):

Sin embargo, si la puerta TTL emite una señal "alta" (garantizada entre 5 voltios y 2,7 voltios), podría no ser interpretado correctamente por la entrada de la puerta CMOS como un "alto" (esperando un voltaje entre 5 voltios y 3,5 voltios):

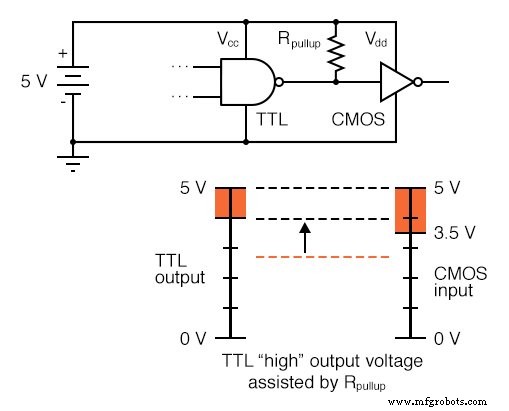

Dada esta discrepancia, es totalmente posible que la puerta TTL emita una señal "alta" válida (válida, es decir, de acuerdo con los estándares para TTL) que se encuentre dentro del rango "incierto" para la entrada CMOS, y puede ser ( falsamente) interpretado como un "bajo" por la puerta de recepción. Una "solución" fácil para este problema es aumentar el nivel de voltaje de señal "alto" de la puerta TTL por medio de una resistencia pullup:

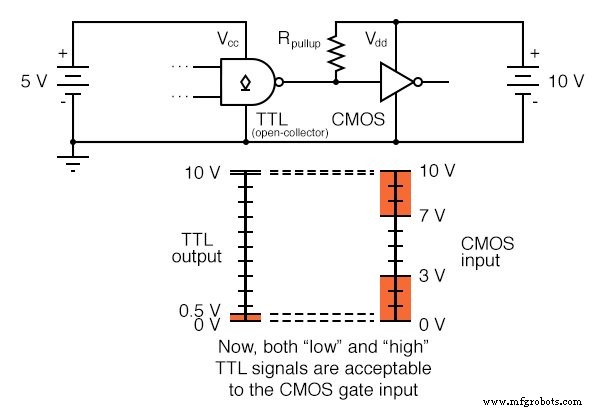

Sin embargo, se requiere algo más que esto para conectar una salida TTL con una entrada CMOS, si la puerta CMOS receptora está alimentada por un voltaje de fuente de alimentación mayor:

Usando una puerta TTL de colector abierto con una puerta CMOS

No habrá ningún problema con que la puerta CMOS interprete la salida "baja" de la puerta TTL, por supuesto, pero una señal "alta" de la puerta TTL es otra cuestión. El rango de voltaje de salida garantizado de 2,7 voltios a 5 voltios de la salida de la puerta TTL no se acerca al rango aceptable de la puerta CMOS de 7 voltios a 10 voltios para una señal "alta".

Si usamos un colector abierto Sin embargo, una puerta TTL en lugar de una puerta de salida de tótem, una resistencia pullup al V dd de 10 voltios El riel de suministro elevará el voltaje de salida "alto" de la puerta TTL al voltaje de suministro de energía completo que suministra la puerta CMOS. Dado que una compuerta de colector abierto solo puede absorber corriente, no generar corriente, el nivel de voltaje del estado "alto" está completamente determinado por la fuente de alimentación a la que está conectada la resistencia pullup, resolviendo así el problema de desajuste:

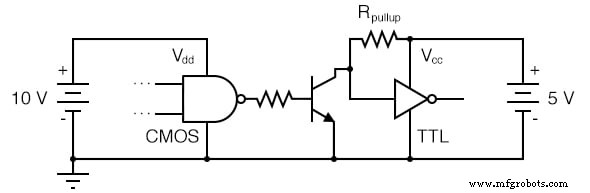

Problemas al usar la salida CMOS en una entrada TTL

Debido a las excelentes características de voltaje de salida de las puertas CMOS, normalmente no hay problemas para conectar una salida CMOS a una entrada TTL. El único problema importante es la carga de corriente que presentan las entradas TTL, ya que la salida CMOS debe reducir la corriente para cada una de las entradas TTL mientras se encuentra en el estado "bajo".

Cuando la puerta CMOS en cuestión está alimentada por una fuente de voltaje superior a 5 voltios (V cc ), sin embargo, surgirá un problema. El estado de salida "alto" de la puerta CMOS, que es superior a 5 voltios, excederá los límites de entrada aceptables de la puerta TTL para una señal "alta".

Uso de circuito inversor de colector abierto

Una solución a este problema es crear un circuito inversor de "colector abierto" utilizando un transistor NPN discreto y utilizarlo para interconectar las dos puertas:

La "R pullup La resistencia de ”es opcional, ya que las entradas TTL asumen automáticamente un estado“ alto ”cuando se dejan flotantes, que es lo que sucederá cuando la salida de la compuerta CMOS sea“ baja ”y el transistor se corte. Por supuesto, una consecuencia muy importante de implementar esta solución es la inversión lógica creada por el transistor:cuando la puerta CMOS emite una señal "baja", la puerta TTL ve una entrada "alta"; y cuando la puerta CMOS emite una señal "alta", el transistor se satura y la puerta TTL ve una entrada "baja". Siempre que esta inversión se tenga en cuenta en el esquema lógico del sistema, todo irá bien.

HOJA DE TRABAJO RELACIONADA:

-

Hoja de trabajo de señales lógicas digitales

Tecnología Industrial