Diseño integrado con FPGA:recursos de hardware

Nota del editor:a medida que continúan surgiendo algoritmos avanzados para diseños de productos inteligentes, los desarrolladores a menudo se encuentran luchando para implementar sistemas integrados capaces de satisfacer las demandas de procesamiento asociadas de estos algoritmos. Los FPGA pueden ofrecer el rendimiento requerido, pero el diseño con FPGA se ha considerado durante mucho tiempo limitado al ámbito de los expertos en programación de FPGA. Sin embargo, hoy en día, la disponibilidad de FPGA más potentes y entornos de desarrollo más efectivos ha hecho que el desarrollo de FPGA sea ampliamente accesible. En este extracto, Capítulo 4 del libro Architecting High-Performance Embedded Systems, el autor ofrece una revisión completa de los dispositivos FPGA, los lenguajes de implementación y el proceso de desarrollo de FPGA, así como un tutorial detallado de cómo comenzar a implementar FPGA en su propio diseño. El extracto completo se presenta en la siguiente serie de entregas:

Nota del editor:a medida que continúan surgiendo algoritmos avanzados para diseños de productos inteligentes, los desarrolladores a menudo se encuentran luchando para implementar sistemas integrados capaces de satisfacer las demandas de procesamiento asociadas de estos algoritmos. Los FPGA pueden ofrecer el rendimiento requerido, pero el diseño con FPGA se ha considerado durante mucho tiempo limitado al ámbito de los expertos en programación de FPGA. Sin embargo, hoy en día, la disponibilidad de FPGA más potentes y entornos de desarrollo más efectivos ha hecho que el desarrollo de FPGA sea ampliamente accesible. En este extracto, Capítulo 4 del libro Architecting High-Performance Embedded Systems, el autor ofrece una revisión completa de los dispositivos FPGA, los lenguajes de implementación y el proceso de desarrollo de FPGA, así como un tutorial detallado de cómo comenzar a implementar FPGA en su propio diseño. El extracto completo se presenta en la siguiente serie de entregas:

1:Recursos de hardware (este artículo)

2:Idiomas de implementación

3:Proceso de desarrollo

4:Creación de un proyecto

5:Implementación

Adaptado de Architecting High-Performance Embedded Systems, por Jim Ledin.

Desarrollo de su primer programa FPGA

Este capítulo comienza con una discusión sobre el uso efectivo de dispositivos FPGA en sistemas embebidos en tiempo real y continúa con una descripción de los elementos funcionales contenidos en los FPGA estándar. La gama de lenguajes de diseño de FPGA, incluido Hardware Idiomas de descripción ( HDL ), se introducen métodos de diagrama de bloques y lenguajes de programación de software populares, incluidos C y C ++. El capítulo continúa con una descripción general del proceso de desarrollo de FPGA y concluye con un ejemplo completo de un ciclo de desarrollo de FPGA que comienza con una declaración de los requisitos del sistema y termina con un sistema funcional implementado en una placa de desarrollo de FPGA de bajo costo.

Después de completar este capítulo, sabrá cómo se pueden aplicar los FPGA en arquitecturas de sistemas embebidos en tiempo real y comprenderá los componentes que componen un circuito integrado FPGA. Habrá aprendido sobre los lenguajes de programación utilizados en el diseño de algoritmos FPGA y comprenderá la secuencia de pasos para desarrollar una aplicación basada en FPGA. También habrá trabajado con un ejemplo completo de desarrollo de FPGA en una placa de desarrollo de bajo costo utilizando herramientas de software FPGA gratuitas.

Cubriremos los siguientes temas en este capítulo:

- Uso de FPGA en diseños de sistemas integrados en tiempo real

- Lenguajes de implementación de FPGA

- El proceso de desarrollo de FPGA

- Desarrollando su primer proyecto FPGA

Requisitos técnicos

Los archivos de este capítulo están disponibles en https://github.com/PacktPublishing/Architecting-High-Performance-Embedded-Systems.

Uso de FPGA en diseños de sistemas integrados en tiempo real

Como vimos en los Elementos de FPGA sección del Capítulo 1 , Arquitectura de alto rendimiento Sistemas integrados , un dispositivo FPGA típico contiene una gran cantidad de tablas de búsqueda, flip-flops, elementos de RAM de bloque, segmentos de DSP y otros componentes. Si bien puede ser instructivo comprender las capacidades detalladas de cada uno de estos componentes, tales preocupaciones no son necesariamente informativas durante el proceso de desarrollo de FPGA. La restricción más importante a tener en cuenta es que un número de pieza de FPGA específico contiene un número finito de cada uno de estos elementos, y un diseño no puede exceder esos límites cuando se apunta a ese modelo de FPGA en particular.

En cambio, es más productivo ver el proceso de desarrollo de FPGA desde la perspectiva de la declaración de requisitos del sistema integrado. Puede comenzar a desarrollar el diseño FPGA dirigido a un modelo FPGA elegido arbitrariamente. A medida que avanza el desarrollo, puede alcanzar un límite de recursos o identificar una característica de FPGA que el diseño requiere y que no está presente en la FPGA actualmente seleccionada. En ese momento, puede seleccionar un objetivo diferente, más capaz y continuar con el desarrollo.

Alternativamente, a medida que el desarrollo del diseño se acerca a su finalización, puede darse cuenta de que el FPGA objetivo que seleccionó originalmente contiene recursos excesivos y el diseño podría mejorarse seleccionando un FPGA más pequeño, con beneficios potenciales en términos de menor costo, menos pines, tamaño de paquete más pequeño, y consumo de energía reducido.

En cualquiera de estas situaciones, generalmente es sencillo cambiar el FPGA objetivo a un modelo diferente dentro de la misma familia. Las herramientas de desarrollo y los artefactos de diseño que ha creado hasta este punto deberían ser completamente reutilizables con el modelo FPGA recién diseñado. Si es necesario cambiar a una familia diferente de FPGA del mismo proveedor, o a un modelo de un proveedor diferente, es probable que el cambio implique más trabajo.

El objetivo de esta discusión es enfatizar que no es demasiado importante identificar un modelo FPGA específico al comienzo de un esfuerzo de desarrollo de un sistema integrado de alto rendimiento. En cambio, las primeras consideraciones deben centrarse en validar la decisión de utilizar un FPGA como parte del diseño, luego, si el FPGA es el mejor enfoque de diseño, proceda con la selección de un proveedor de FPGA y una familia de dispositivos adecuados.

Los proyectos de ejemplo de este libro se basarán en la familia Xilinx Vivado de herramientas de desarrollo FPGA. Aunque se debe comprar una licencia de Vivado para desarrollar para algunas familias de FPGA de Xilinx, los dispositivos FPGA en Artix-7 con los que trabajaremos son compatibles con Vivado de forma gratuita. La familia Artix-7 FPGA combina los atributos de alto rendimiento, bajo consumo de energía y costo total reducido del sistema. Otras familias de dispositivos FPGA y conjuntos de herramientas de desarrollo similares están disponibles de otros proveedores de FPGA.

El desarrollo de FPGA es un proceso bastante complicado, con una variedad de tipos de análisis y entrada de datos de diseño necesarios. Para evitar discutir estos temas en un nivel demasiado abstracto, y para presentar resultados concretos en términos de proyectos de ejemplo de trabajo, usaremos Vivado a lo largo del libro. Una vez que esté familiarizado con las herramientas y técnicas discutidas aquí, debería poder aplicarlas usando herramientas similares de otros proveedores.

Las siguientes secciones discutirán algunas características clave de diferenciación de las familias de FPGA y modelos individuales dentro de esas familias, incluida la cantidad de RAM de bloque, la cantidad y los tipos de señales de E / S disponibles, los recursos de hardware especializados en chip y la inclusión de uno o más núcleos de procesador de hardware en el paquete FPGA.

Bloquear RAM y RAM distribuida

Bloquear RAM se utiliza para implementar regiones de memoria dentro de una FPGA. Una región de memoria particular se especifica en términos de ancho en bits (típicamente 8 o 16 bits) y la profundidad, que define el número de ubicaciones de almacenamiento en la región de memoria.

La cantidad total de RAM de bloque en un FPGA generalmente se especifica en términos de kilobits ( Kb ). La cantidad de RAM de bloque disponible varía entre las familias de FPGA y entre los modelos dentro de una familia en particular. Como era de esperar, las piezas más grandes y caras generalmente tienen una mayor cantidad de recursos que se pueden usar como RAM de bloque.

En los FPGA de Xilinx, y en diversos grados en los FPGA de otros proveedores, una categoría distinta de memoria llamada RAM distribuida está disponible además de la RAM de bloque. RAM distribuida se construye a partir de los elementos lógicos utilizados en las tablas de búsqueda y reutiliza los circuitos de esos dispositivos para formar pequeños segmentos de RAM, cada uno de los cuales contiene 16 bits. Estos segmentos se pueden agregar para formar bloques de memoria más grandes cuando sea necesario.

La RAM de bloque tiende a usarse para propósitos tradicionalmente asociados con la RAM, como implementar la memoria caché del procesador o como un búfer de almacenamiento para datos de E / S. La RAM distribuida se puede utilizar para fines como el almacenamiento temporal de resultados de cálculo intermedios. Debido a que la RAM distribuida se basa en circuitos de tablas de búsqueda, el uso de RAM distribuida en un diseño reduce los recursos disponibles para implementar operaciones lógicas.

La RAM de bloque puede tener un solo puerto o puertos duales. La RAM de bloque de puerto único representa el patrón de uso común de un procesador que lee y escribe RAM durante la operación.

La RAM de bloque de dos puertos proporciona dos puertos de lectura / escritura, los cuales pueden leer o escribir activamente en la misma región de memoria simultáneamente.

La RAM de bloque de dos puertos es ideal para situaciones en las que se transfieren datos entre partes de una FPGA que se ejecutan a diferentes velocidades de reloj. Por ejemplo, un subsistema de E / S puede tener una velocidad de reloj de cientos de MHz cuando recibe un flujo de datos entrante. El subsistema de E / S escribe los datos entrantes en la RAM del bloque a medida que llegan a través de uno de los canales de E / S de alta velocidad de la FPGA. Un subsistema separado dentro de la FPGA, que se ejecuta a una velocidad de reloj diferente, puede leer datos del segundo puerto de la RAM del bloque sin interferir con el funcionamiento del subsistema de E / S.

Block RAM también puede funcionar en primero en entrar, primero en salir ( FIFO ) modo. En el ejemplo del flujo de datos en serie entrante, el subsistema de E / S puede insertar palabras de datos en el FIFO a medida que llegan y el subsistema de procesamiento puede leerlas en el mismo orden. La RAM de bloque en modo FIFO proporciona señales que indican si el FIFO está lleno, vacío, casi lleno o casi vacío. Las definiciones de casi completo y casi vacío dependen del diseñador del sistema. Si asigna casi vacío para significar que quedan menos de 16 elementos en el FIFO, puede estar seguro de que siempre que el FIFO no indique que está casi vacío, puede leer 16 elementos sin más verificaciones de la disponibilidad de datos.

Cuando se usa RAM de bloque en modo FIFO, es vital que la lógica que inserta elementos en el FIFO nunca intente escribir cuando el FIFO está lleno, y la lectura lógica del FIFO nunca intenta leer cuando el FIFO está vacío. Si ocurre cualquiera de estos eventos, el sistema perderá datos o intentará procesar datos no definidos.

Pines de E / S de FPGA y funciones asociadas

Debido a que los FPGA están diseñados para usarse en aplicaciones de alto rendimiento, sus pines de E / S generalmente son capaces de implementar una variedad de estándares de E / S de alta velocidad. Durante la implementación de un diseño con una suite de herramientas de desarrollo FPGA, el desarrollador del sistema debe realizar tareas que incluyen la asignación de funciones a pines particulares en el paquete FPGA y configurar cada uno de esos pines para operar con el estándar de interfaz apropiado. Se deben realizar pasos adicionales para asociar las señales de entrada y salida dentro del código de modelo FPGA con los pines del paquete correcto.

A nivel de pin, las señales de E / S individuales son de un solo extremo o diferenciales.

Una señal de un solo extremo está referenciado a tierra. Lógica transistor-transistor tradicional ( TTL ) y Semiconductor complementario de óxido metálico ( CMOS ) las señales digitales operan en un rango de 0-5 VCC en relación con la tierra.

Los FPGA modernos normalmente no admiten el rango de señal heredado de 5 VCC, sino que admiten señales TTL y CMOS que operan en un rango de voltaje reducido, lo que reduce el consumo de energía y mejora la velocidad. TTL de bajo voltaje ( LVTTL ) Las señales funcionan en un rango de 0-3,3 V CC. CMOS de bajo voltaje ( LVCMOS ) las señales se pueden seleccionar con voltajes de señalización de 1,2, 1,5, 1,8, 2,5 y 3,3 V. Estos tipos de señales se denominan LVCMOS12, LVCMOS15, LVCMOS18, LVCMOS25 y LVCMOS33. Hay disponibles otros tipos de señales de un solo extremo de alto rendimiento, incluida la lógica de transceptor de alta velocidad ( HSTL ) y Lógica terminada serie stub ( SSTL ).

Las señales de un solo extremo se utilizan ampliamente para fines de baja frecuencia, como la lectura de entradas de pulsadores y LED de iluminación. Las señales de un solo extremo también se utilizan en muchos protocolos de comunicación de baja velocidad, como I2C y SPI. Un inconveniente importante de las señales de un solo extremo es que cualquier ruido acoplado a los cables y las pistas de la placa de circuito impreso que transportan la señal tiene el potencial de corromper la entrada al receptor. Este problema se puede reducir sustancialmente mediante el uso de señalización diferencial.

Para las tasas de transferencia de datos más altas, la señalización diferencial es el enfoque preferido.

Señales diferenciales use un par de pines de E / S e impulse señales opuestas en los dos pines.

En otras palabras, un pin se conduce a un voltaje más alto y el otro pin a un voltaje más bajo para representar un bit de datos 0 y los voltajes de los pines se invierten para representar un bit de 1. El receptor diferencial resta las dos señales para determinar si el bit de datos es 0 o 1. Debido a que los dos cables o trazas que llevan la señal diferencial están ubicados físicamente muy juntos, cualquier ruido que se acople a una de las señales se acoplará a la otra. de una manera muy similar. La operación de resta elimina la gran mayoría del ruido, lo que permite una operación confiable a velocidades de transferencia de datos mucho más altas que las señales de un solo extremo.

Los FPGA estándar admiten una serie de estándares de señal diferencial. Se definen varias versiones diferenciales de HSTL y SSTL, con una variedad de niveles de voltaje de señalización para cada una.

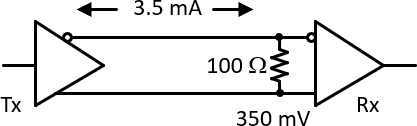

Señalización diferencial de bajo voltaje ( LVDS ) se introdujo como estándar en 1994 y continúa utilizándose en una variedad de aplicaciones. Un transmisor de señalización LVDS produce una corriente constante de 3,5 mA y cambia la dirección de la corriente que fluye a través de la resistencia en el receptor para producir cambios de estado que representan valores de datos 0 y 1 como se muestra en la Figura 4.1 :

Figura 4.1 - Interfaz LVDS

En la comunicación LVDS, como en los otros estándares de señalización diferencial y de un solo extremo, es importante que la impedancia de la ruta de comunicación entre el transmisor y el receptor coincida estrechamente con la impedancia de terminación, que es de 100 ohmios en el caso de LVDS. Si la impedancia del canal de comunicación no coincide con la impedancia de terminación, pueden producirse reflejos en la línea, impidiendo la recepción de datos confiable.

La impedancia de los pares de trazas de señales diferenciales es función de la geometría de las trazas de pares y su relación con el plano de tierra. Como veremos en el Capítulo 6 , Diseño de circuitos con KiCad , es sencillo diseñar placas de circuito que satisfagan los requisitos de los estándares de señalización diferencial de alta velocidad.

Recursos de hardware especializados

Los FPGA generalmente incluyen una selección de recursos de hardware dedicados para funciones que se requieren comúnmente y se implementan de manera más eficiente en hardware en lugar de usar funciones FPGA sintetizadas, o no es posible implementar con componentes FPGA. Algunos ejemplos de estos recursos son los siguientes:

- Interfaces con RAM dinámica externa ( DRAM ) para almacenar grandes cantidades de Estas interfaces generalmente admiten un estándar DRAM común como DDR3.

- Convertidores de analógico a digital.

- Bucles de bloqueo de fase, que se utilizan para generar múltiples frecuencias de reloj.

- Procesamiento de señales digitales multiplicar-acumular ( MAC ) hardware.

Estos recursos de hardware permiten el desarrollo de sistemas complejos con una amplia gama de capacidades. Se proporciona hardware dedicado para funciones como la operación MAC porque el rendimiento del hardware es significativamente mejor que la funcionalidad equivalente sintetizada utilizando recursos lógicos FPGA.

Núcleos de procesador

Algunas familias de FPGA incluyen núcleos de procesador de hardware con el fin de combinar la velocidad máxima de ejecución del software con las ventajas de rendimiento de los algoritmos implementados por FPGA. Por ejemplo, la familia Xilinx Zynq-7000 integra un procesador ARM Cortex-A9 de hardware junto con una estructura FPGA tradicional.

Los diseños de FPGA que no requieren un procesador de hardware pueden implementar un procesador utilizando los recursos de FPGA, denominado procesador suave . Los procesadores de software son altamente configurables, aunque generalmente no son capaces de igualar el rendimiento de un procesador implementado en hardware.

La siguiente sección presentará los lenguajes de programación principales y los métodos de entrada de datos utilizados para desarrollar algoritmos FPGA.

Reproducido con permiso de Packt Publishing. Copyright © 2021 Packt Publishing

Jim Ledin es el director ejecutivo de Ledin Engineering, Inc. Jim es un experto en diseño, desarrollo y pruebas de software y hardware integrados. También tiene experiencia en evaluación de ciberseguridad de sistemas integrados y pruebas de penetración. Tiene un B.S. Licenciado en ingeniería aeroespacial de la Universidad Estatal de Iowa y un M.S. Licenciatura en ingeniería eléctrica e informática del Instituto de Tecnología de Georgia. Jim es un ingeniero eléctrico profesional registrado en California, un profesional certificado en seguridad del sistema de información (CISSP), un hacker ético certificado (CEH) y un probador de penetración certificado (CPT).

Jim Ledin es el director ejecutivo de Ledin Engineering, Inc. Jim es un experto en diseño, desarrollo y pruebas de software y hardware integrados. También tiene experiencia en evaluación de ciberseguridad de sistemas integrados y pruebas de penetración. Tiene un B.S. Licenciado en ingeniería aeroespacial de la Universidad Estatal de Iowa y un M.S. Licenciatura en ingeniería eléctrica e informática del Instituto de Tecnología de Georgia. Jim es un ingeniero eléctrico profesional registrado en California, un profesional certificado en seguridad del sistema de información (CISSP), un hacker ético certificado (CEH) y un probador de penetración certificado (CPT). Contenidos relacionados:

- Las herramientas de código abierto ayudan a simplificar la programación FPGA

- Implementación de algoritmos de punto flotante en FPGA o ASIC

- Aprovechamiento de FPGA para el aprendizaje profundo

- Las herramientas de software migran el código de la GPU a FPGA para aplicaciones de inteligencia artificial

- Los FPGA desplazan a los ASIC en el ADAS basado en la visión de Subaru Eyesight

- Cómo los FPGA basados en flash simplifican los requisitos de seguridad funcional

- Aprovechar los beneficios de los FPGA instantáneos

- Configuración de FPGA usando flash NOR de alta velocidad

- Cómo está evolucionando la tecnología FPGA para cumplir con los nuevos requisitos del sistema de rango medio

Para obtener más información sobre Embedded, suscríbase al boletín informativo semanal por correo electrónico de Embedded.

Incrustado

- Cómo evitar sorpresas costosas en el diseño de hardware conectado

- Qué es el diseño de sistemas integrados:pasos en el proceso de diseño

- Simplificación del desarrollo de IoT con Eclipse IoT

- Desarrollo de máquinas de estado con desarrollo basado en pruebas

- Convertir macrodatos en datos inteligentes con IA incorporada

- Los recursos impulsados por la comunidad realizan un seguimiento de las debilidades de seguridad del diseño del hardware

- Cypress:ModusToolbox Suite facilita la complejidad del diseño de IoT

- Lattice:MachX03D FPGA mejora la seguridad con capacidades de raíz de confianza de hardware

- El kit de diseño mide la presión arterial con un sensor óptico

- Java 9 - Prueba con la mejora de los recursos

- Todo con aditivo