La nueva herramienta basada en ML ofrece optimización automatizada del flujo de diseño de chips

No se puede debatir el hecho de que el diseño de chips se está volviendo cada vez más complejo a medida que los clientes exigen más funciones y dispositivos más pequeños y un menor consumo de energía. Para satisfacer esta demanda, los ingenieros están sobrecargados y necesitan soporte para mantenerse al día con la demanda y el desarrollo oportuno de productos.

Para abordar esto, Cadence Design Systems ha introducido una nueva herramienta que utiliza el aprendizaje automático (ML) para impulsar el flujo de implementación de Cadence RTL-to-signoff, entregando lo que dijo es hasta 10 veces la productividad y 20% PPA (potencia, rendimiento y área ) mejoras para la implementación. Su nuevo Explorador de chips inteligente Cerebrus proporciona capacidades de gestión de recursos informáticos en el sitio y en la nube más eficientes que la exploración de diseño tradicional impulsada por humanos; y mejora el PPA y la productividad en muchos nodos y múltiples aplicaciones finales, incluido el consumidor, la computación a hiperescala, las comunicaciones 5G, el diseño automotriz y móvil.

En una sesión informativa con embedded.com, Rod Metcalfe, director del grupo de gestión de productos de Cadence, dijo:“Esta es la primera herramienta de optimización digital de flujo completo que utiliza ML. Esto es importante, ya que a medida que aumenta la complejidad del diseño, el diseño de chips exige más funciones e inteligencia, pero existe una limitación en la cantidad de ingenieros disponibles para llevar a cabo estas tareas. Seguimos viendo a los diseñadores realizando un desarrollo de flujo manual e iterando alrededor del ciclo para cumplir con sus objetivos de diseño:esto requiere una gran cantidad de esfuerzo de ingeniería y no es escalable. Ahí es donde entra Cerebrus, utilizando computación masiva para mejorar la productividad para la automatización del diseño ".

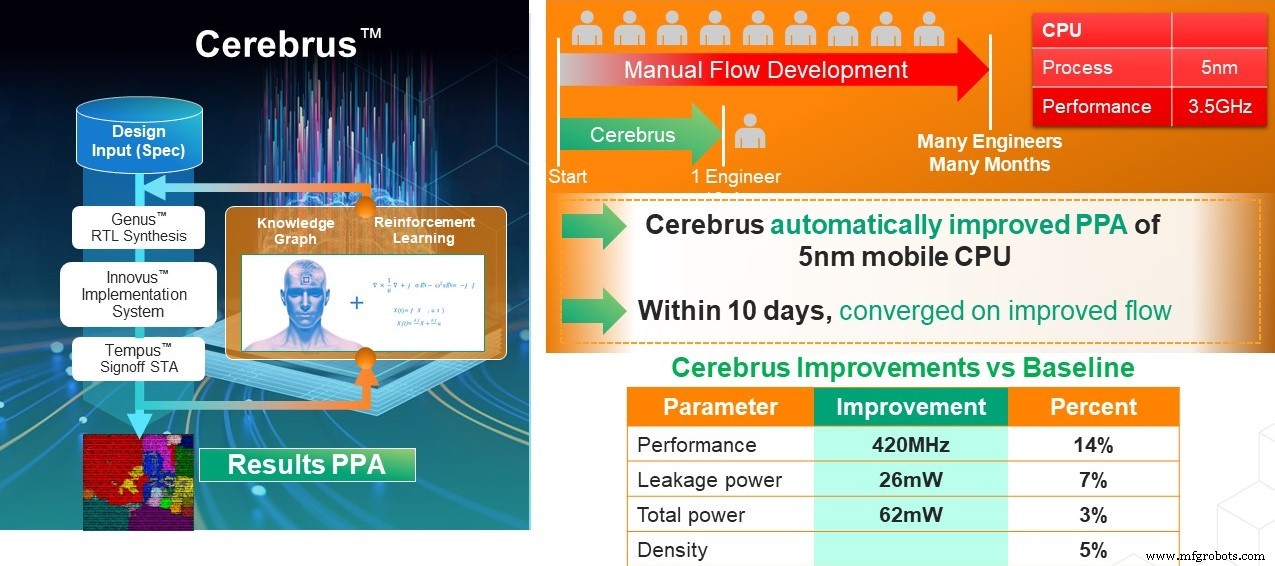

Metcalfe destacó un ejemplo en el que Cerebrus solo necesitaba un ingeniero para converger en un flujo de diseño mejorado en 10 días para mejorar automáticamente el PPA de una CPU móvil de 5 nm (ver gráfico a continuación).

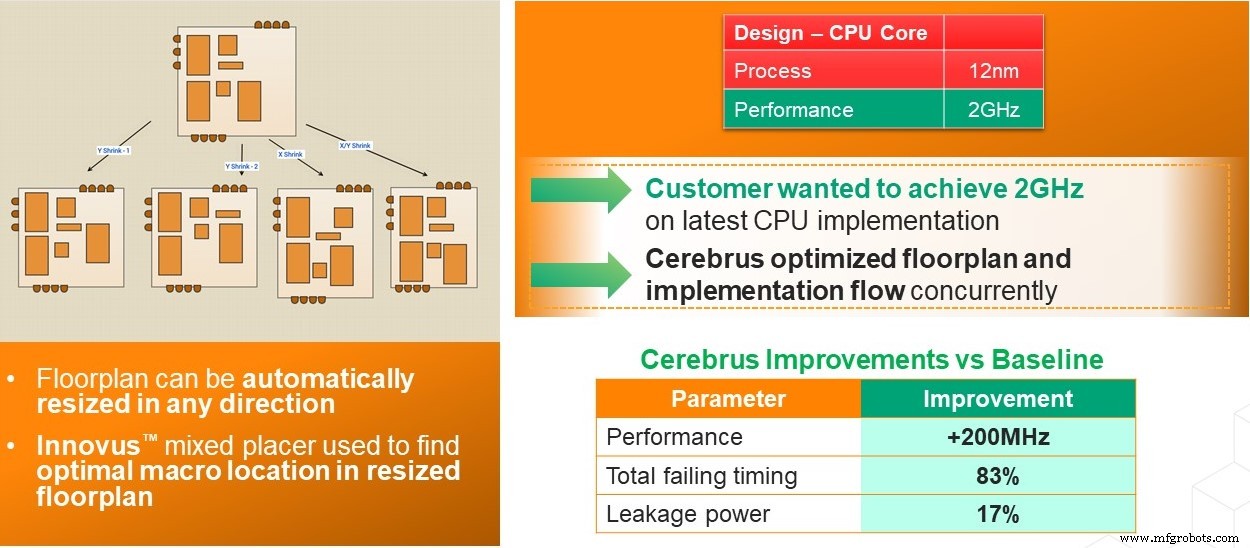

Otro ejemplo en un nivel superior es la optimización automática del plano de planta, como se muestra en el gráfico siguiente:

El impacto de usar una herramienta basada en ML como Cerebrus es que los equipos de diseño tienen una forma automatizada de reutilizar el conocimiento de diseño histórico; anteriormente, habrían dedicado un exceso de tiempo al reaprendizaje manual con cada nuevo proyecto. Por lo tanto, Cadence dijo que Cerebrus marca una revolución en la industria de EDA con un diseño de chip digital impulsado por ML, donde los equipos de ingeniería tienen una mayor oportunidad de proporcionar un mayor impacto en sus organizaciones porque pueden descargar los procesos manuales. A medida que la industria continúa moviéndose hacia nodos avanzados y el tamaño y la complejidad del diseño aumentan, Cerebrus ayudará a los diseñadores a lograr los objetivos de PPA de manera más eficiente.

Los primeros respaldos de los clientes para la herramienta provinieron de Renesas y Samsung Foundry.

Satoshi Shibatani, director del departamento de tecnología de diseño digital en la división compartida de I + D EDA de Renesas, dijo:“Para maximizar de manera eficiente el rendimiento de los nuevos productos que utilizan nodos de procesos emergentes, los flujos de implementación digital utilizados por nuestro equipo de ingeniería deben actualizarse continuamente. La optimización del flujo de diseño automatizado es fundamental para realizar el desarrollo de productos con un rendimiento mucho mayor. Cerebrus, con sus innovadoras capacidades de aprendizaje automático, y las herramientas Cadence RTL-to-signoff han proporcionado optimización de flujo automatizada y exploración de planos de planta, mejorando el rendimiento del diseño en más del 10% ”.

Mientras tanto, en Samsung Foundry, su vicepresidente de tecnología de diseño, Sangyun Kim, dijo:“A medida que continuamos implementando nodos de proceso actualizados, la eficiencia de nuestro programa de co-optimización de tecnología de diseño (DTCO) es muy importante. . Como parte de nuestra asociación a largo plazo con Cadence, Samsung Foundry ha utilizado Cerebrus y el flujo de implementación digital de Cadence en múltiples aplicaciones. Hemos observado una reducción de energía de más del 8% en algunos de nuestros bloques más críticos en solo unos días en comparación con muchos meses de esfuerzo manual. Además, estamos utilizando Cerebrus para el dimensionamiento automatizado de la red de distribución de energía de los planos de planta, lo que ha dado como resultado una mejor sincronización del diseño final en más de un 50%.

Las características y beneficios clave de Cerebrus son:

- Refuerzo ML : encuentra rápidamente soluciones de flujo que los ingenieros humanos podrían no probar o explorar de forma natural, lo que mejora el PPA y la productividad.

- Reutilización del modelo de AA :permite que los aprendizajes de diseño se apliquen automáticamente a diseños futuros, lo que reduce el tiempo para obtener mejores resultados.

- Productividad mejorada :permite que un solo ingeniero optimice el flujo completo de RTL a GDS automáticamente para muchos bloques al mismo tiempo, lo que permite que los equipos de diseño completos sean más productivos.

- Computación distribuida masivamente :proporciona exploración de diseño escalable local o basada en la nube para una optimización del flujo más rápida.

- Interfaz fácil de usar: La potente cabina de usuario permite el análisis interactivo de resultados y la gestión de ejecuciones para obtener información valiosa sobre las métricas de diseño.

Cerebrus es parte del flujo completo digital más amplio de Cadence, que trabaja a la perfección con la solución de síntesis Genus, el sistema de implementación Innovus, la solución de firma de temporización Tempus, la solución de energía Joules RTL, la solución de integridad de energía Voltus IC y el sistema de verificación Pegasus para proporcionar a los clientes una ruta rápida para diseñar el cierre y una mejor previsibilidad.

Incrustado

- Subiendo a un nuevo nivel de IA de borde

- Pulsic ofrece una vista previa del diseño del chip analógico en tiempo real en el editor de esquemas

- El proyecto explora un diseño confiable y un flujo de verificación para la seguridad de IoT

- Ingeniería y diseño de neumáticos SIMULIA

- Pensilvania ofrece nuevos fondos para ayudar a los estudiantes de Filadelfia a descubrir oportunidades en la fabricación

- Ingeniería de diseño de preformas a medida

- Barra/mandril con diseño frontal abierto y más

- Nuevo diseño de transistor disfraza hardware de chip de computadora clave para proteger contra piratas informáticos

- Sandvik presenta un nuevo concepto de torneado

- El panorama de la integración de la nueva línea

- Cómo agregar una nueva herramienta