Cómo usar el tipo de VHDL más común:std_logic

El tipo más común usado en VHDL es el std_logic . Piense en este tipo como un solo bit, la información digital transportada por un solo cable físico. El std_logic nos da un control más detallado sobre los recursos en nuestro diseño que el integer type, que hemos estado usando en los tutoriales anteriores.

Normalmente, queremos que un cable en una interfaz digital tenga el valor '1' o '0' . Estos dos valores son los únicos valores que puede tener un bit, un dígito binario. Pero en realidad, una señal digital física puede estar en varios estados, que el std_logic type hace un buen trabajo de emulación. Por lo tanto, es el tipo más utilizado en VHDL.

Esta publicación de blog es parte de la serie Tutoriales básicos de VHDL.

El std_logic tipo puede tener los siguientes valores:

| '1' | Lógica 1 |

| '0' | Lógica 0 |

| 'Z' | Alta impedancia |

| 'W' | Señal débil, no puedo decir si 0 o 1 |

| 'L' | Débil 0, desplegable |

| 'H' | Débil 1, pull-up |

| ‘-‘ | No me importa |

| 'U' | No inicializado |

| 'X' | Desconocido, varios controladores |

Esto puede parecer una gran cantidad de estados diferentes para un tipo que se supone que modela un solo valor binario. No se preocupe, no usaremos todos estos tipos en esta serie de tutoriales. Usaremos '1' y '0' por supuesto. Y también veremos 'U' y 'X' , que nos ayudará a detectar errores en nuestro diseño. Los otros valores son características avanzadas de VHDL que se pueden usar para cosas como modelar la comunicación con, por ejemplo, I

2

dispositivos C, o para crear buses de tres estados.

Si varios procesos intentan escribir diferentes valores en una señal, decimos que tiene múltiples controladores . Si un std_logic La señal tiene varios controladores, no será un error de compilación o de tiempo de ejecución, al menos no en el simulador. Eso es porque std_logic es un tipo resuelto , lo que significa que su valor será determinado por una función de resolución.

El valor de un std_logic la señal con dos controladores se determinará en función de esta tabla de resolución:

| U | X | 0 | 1 | Z | W | L | H | – | |

|---|---|---|---|---|---|---|---|---|---|

| U | X | X | 1 | 1 | 1 | 1 | 1 | X | 1 |

| U | X | 0 | X | 0 | 0 | 0 | 0 | X | 0 |

| U | U | U | U | U | U | U | U | U | U |

| U | X | X | X | X | X | X | X | X | X |

| U | X | 0 | 1 | Z | W | L | H | X | Z |

| U | X | 0 | 1 | W | W | W | W | X | W |

| U | X | 0 | 1 | L | W | L | W | X | L |

| U | X | 0 | 1 | H | W | W | H | X | H |

| U | X | X | X | X | X | X | X | X | – |

Ejercicio

En este videotutorial aprenderemos a usar declare y show std_logic señales en forma de onda:

El código final que creamos en este tutorial:

library ieee;

use ieee.std_logic_1164.all;

entity T10_StdLogicTb is

end entity;

architecture sim of T10_StdLogicTb is

signal Signal1 : std_logic := '0';

signal Signal2 : std_logic;

signal Signal3 : std_logic;

begin

process is

begin

wait for 10 ns;

Signal1 <= not Signal1;

end process;

-- Driver A

process is

begin

Signal2 <= 'Z';

Signal3 <= '0';

wait;

end process;

-- Driver B

process(Signal1) is

begin

if Signal1 = '0' then

Signal2 <= 'Z';

Signal3 <= 'Z';

else

Signal2 <= '1';

Signal3 <= '1';

end if;

end process;

end architecture;

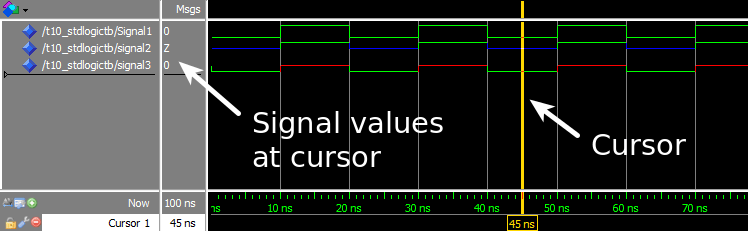

La ventana de forma de onda en ModelSim después de presionar Ejecutar y hacer zoom en la línea de tiempo:

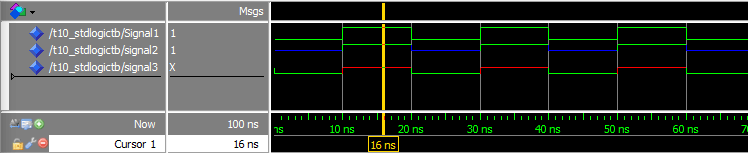

La forma de onda con el cursor colocado en la otra parte del ciclo de la señal repetitiva:

Análisis

El ejercicio demostró cómo funciona la función de resolución de VHDL con el std_logic escribe. Cuando se trabaja con lógica digital, suele ser más práctico estudiar la línea de tiempo en una forma de onda en lugar de utilizar impresiones. Por lo tanto, usamos la forma de onda de ModelSim para verificar los valores de la señal en este ejercicio.

El primer proceso y Signal1 solo se usa para cambiar el valor que el tercer proceso está impulsando en Signal2 y Signal3 .

El segundo proceso, Driver A, intentará conducir un 'Z' en Signal2 y un '0' en Signal3 constantemente.

El tercer proceso, Conductor B, alternará entre conducir '1' y 'Z' en ambos Signal2 y Signal3 .

Vemos en las capturas de pantalla de forma de onda que Signal1 está cambiando entre '0' y '1' , porque solo hay un proceso que intenta impulsar esta señal. También podemos ver que las múltiples señales de los controladores se resuelven de acuerdo con la tabla de resolución publicada en los comentarios del código VHDL:

| Señal | Conductor A | Conductor B | Resultado |

|---|---|---|---|

| Señal2 | 'Z' | 'Z' | 'Z' |

| Señal2 | 'Z' | '1' | '1' |

| Señal3 | '0' | 'Z' | '0' |

| Señal3 | '0' | '1' | 'X' |

Para llevar

std_logices el tipo más común utilizado para contener un valor de bit único en VHDL- Piense en un

std_logicseñal como un cable físico en nuestro diseño digital - Si varios procesos intentan generar un

std_logicseñal, su valor está determinado por una tabla de resolución

Ir al siguiente tutorial »

VHDL

- Los cuellos de botella más comunes en el flujo de trabajo de impresión 3D y cómo solucionarlos

- Los problemas más comunes del sistema de refrigeración del automóvil

- Cómo aprovechar al máximo sus datos

- Cómo crear una lista enlazada en VHDL

- Cómo usar un procedimiento en un proceso en VHDL

- Cómo usar una función impura en VHDL

- Cómo usar una función en VHDL

- Cómo usar un procedimiento en VHDL

- Cómo utilizar de forma segura un elevador de motor en el lugar de trabajo

- Las causas más comunes de accidentes con grúas (y cómo evitarlas)

- Las aplicaciones más comunes de a286