Banco de pruebas interactivo usando Tcl

Un banco de pruebas interactivo es una configuración de simulador donde un operador proporciona la entrada al dispositivo bajo prueba (DUT) mientras el banco de pruebas está funcionando. En la mayoría de los casos, esto significa que debe ingresar comandos en la consola del simulador para proporcionar estímulo al DUT.

Si bien siempre debe crear un banco de pruebas de autocomprobación, un banco de pruebas interactivo puede ser un buen complemento. Es más fácil realizar pruebas ad-hoc con un banco de pruebas interactivo a mano que cambiar el código del banco de pruebas de autocomprobación.

Muchas veces, descubrirá problemas en el laboratorio que querrá probar en el banco de pruebas. Con un banco de pruebas interactivo, puede ser tan fácil como escribir la secuencia de entrada que se ha observado para replicar el comportamiento no deseado en el simulador.

Tcl interactuando con VHDL

La mayoría de los simuladores VHDL usan Tcl como lenguaje de consola. Los simuladores tienen un montón de comandos específicos del proveedor, pero la buena noticia es que pueden tratarse como cualquier otro comando Tcl. Puede usar Tcl para crear secuencias de comandos complejas, en su mayoría portátiles, para administrar y respaldar sus bancos de pruebas VHDL.

Cambio de señales VHDL de Tcl

Para interactuar con VHDL, necesitamos encontrar el comando para cambiar el valor de una señal. En ModelSim, este es el comando "forzar". Como se especifica en el documento de referencia del comando, la sinopsis del comando es:

force {<object_name> <value> [[@]<time_info>][, <value> [@]<time_info>]...

[-deposit | -drive | -freeze] [-cancel [@]<time_info>] [-repeat [@]<time_info>] El interruptor que desea usar es el indicador "-depósito". Esto cambia el valor de la señal VHDL instantáneamente, pero permite que otro controlador VHDL o Tcl lo cambie a otra cosa en un momento posterior.

Al ignorar las opciones que no estamos usando, la sinopsis simplificada queda así:

force -deposit <signal_name> <value>

El disparador VHDL

Ahora que sabemos cómo controlar las señales VHDL desde Tcl, necesitamos crear algún tipo de proceso receptor en nuestro banco de pruebas VHDL. El siguiente código muestra un ejemplo mínimo de dicho banco de pruebas.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity interactive is

end interactive;

architecture sim of interactive is

-- Controlled by Tcl

signal trigger : std_logic := '0';

begin

process is

begin

wait until trigger = '1';

report "Triggered!";

end process;

end architecture;

El proceso se reactivará cuando el trigger la señal cambia de algo a '1' . Imprimirá "¡Activado!" a la consola cuando esto suceda, permitiéndonos probar el concepto de controlar procesos VHDL desde Tcl.

Acabo de hacer eso es la consola ModelSim. Los comandos emitidos, así como la salida, se pueden ver en la transcripción a continuación.

VSIM 1> run 10 ns; VSIM 2> force -deposit /trigger '1' VSIM 3> run 0 ns; # ** Note: Triggered! # Time: 10 ns Iteration: 0 Instance: /interactive VSIM 4> force -deposit /trigger '0' VSIM 5> run 10 ns;

Ejecuté el banco de pruebas durante 10 nanosegundos después de iniciar la simulación.

Luego, forcé el trigger señal a '1' . En la siguiente línea, espero 0 nanosegundos. El propósito de esto es crear un ciclo delta. Quiero que se active el proceso, pero no quiero que pase ningún tiempo de simulación.

Finalmente, fuerzo el trigger señal de regreso a '0' antes de continuar con el banco de pruebas.

Podemos ver que el proceso VHDL se despertó después de la línea "ejecutar 0 ns" e imprimió "¡Activado!" a la consola.

Lectura de valores de señal VHDL en tcl

Para leer valores de señal en ModelSim, puede usar el comando "examinar". Podemos por ejemplo leer el valor del trigger señal usando este comando en la consola de ModelSim:

VSIM 6> examine /trigger # 0

Querría asignar el valor a una variable Tcl cuando use "examinar" en un script. Intentemos esto en la consola de ModelSim:

VSIM 7> set triggerVal [examine /trigger] # 0

Entonces podemos, por ejemplo, imprimir la variable usando el comando Tcl "puts":

VSIM 8> puts "triggerVal: $triggerVal" # triggerVal: 0

Detener el simulador después de cada prueba

La forma más fácil de ejecutar la prueba durante el tiempo suficiente para que el DUT reaccione es simplemente ejecutar el simulador durante un valor de tiempo fijo. Por ejemplo, si el DUT debe reaccionar después de dos ciclos de reloj y el período de reloj es de 10 nanosegundos, usaríamos el comando "ejecutar 20 ns" en nuestro script Tcl.

Si el DUT no tiene un tiempo de reacción fijo, se puede usar una afirmación VHDL para detener la simulación y transferir el control a una función de devolución de llamada Tcl. En ModelSim, esto significaría establecer un punto de interrupción desde su secuencia de comandos Tcl usando el comando "cuando":

when [[-fast] [-id <id#>] [-label <label>] {<when_condition_expression>} {<command>}] También tendría que definir una función de devolución de llamada "onBreak" en Tcl que se ejecutará cuando se alcance el punto de interrupción. La función "onBreak" se especifica en la referencia de comandos de ModelSim.

Los inconvenientes de las pruebas impulsadas por Tcl

Existen inconvenientes en el uso de bancos de prueba que dependen en gran medida de los scripts Tcl. Los más evidentes son los problemas de velocidad y portabilidad.

Los bancos de pruebas controlados por Tcl funcionan iniciando y deteniendo el simulador varias veces para interactuar con el código VHDL. Iniciar y detener la simulación para ejecutar una función Tcl en el medio requiere más tiempo que ejecutar un banco de pruebas VHDL de forma continua. Si bien Tcl es un lenguaje interpretado, VHDL se compila en el simulador y se ejecuta mucho más rápido que Tcl.

Si bien Tcl es portátil para otros simuladores, los comandos específicos del simulador que tendrá que usar no lo son. Incluso si encuentra los comandos equivalentes en el otro simulador, pueden funcionar de manera diferente. Los proveedores de simuladores crean su propio conjunto de reglas para los comandos que admiten. Por lo tanto, un banco de pruebas controlado por Tcl debe considerarse menos portátil que un banco de pruebas VHDL puro.

Nuevo curso de VHDL y FPGA

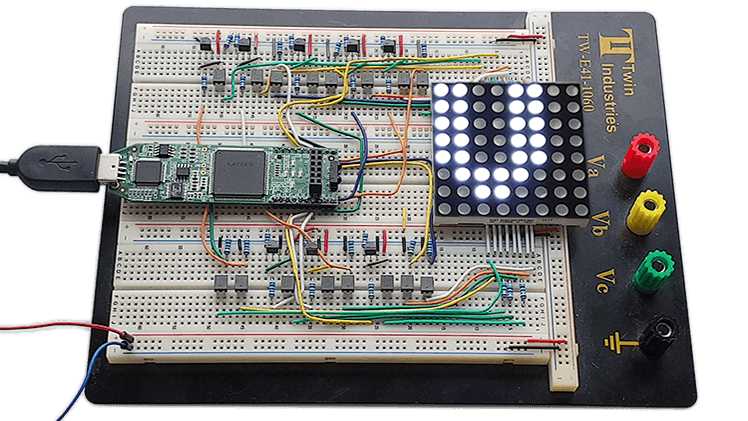

* Actualizado el 12 de octubre de 2020: He completado el curso. Haga clic en la imagen a continuación para obtener más información.

El producto que crearemos es un módulo controlador LED de matriz de puntos. Usaremos la placa de desarrollo Lattice iCEstick de $49. Al final, implementaremos el diseño en una protoboard. Podrá escribir en el teclado de su computadora y los caracteres aparecerán en la pantalla LED de matriz de puntos controlada por la FPGA.

¡Lea más sobre el curso Dot Matrix VHDL y FPGA aquí!

Abre:

Por decidir .

VHDL

- Tutorial - Introducción a VHDL

- Ejemplos de conversiones VHDL

- Declaración de procedimiento:ejemplo de VHDL

- Registros:ejemplo de VHDL

- Firmado vs. Sin firmar en VHDL

- Variables - Ejemplo de VHDL

- C # usando

- Cómo crear una lista de cadenas en VHDL

- Cómo crear un banco de pruebas de autocomprobación

- Proyector láser interactivo con sensores Zigbee

- Uso de una fresadora como torno