Registros de desplazamiento universales:entrada y salida en paralelo

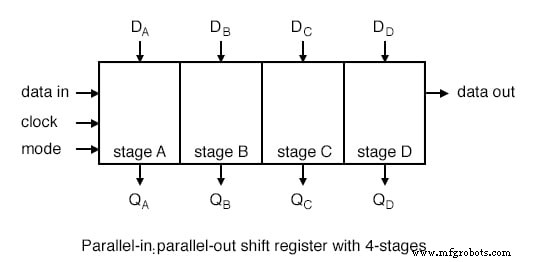

El propósito del registro de desplazamiento de entrada / salida en paralelo es tomar datos en paralelo, desplazarlos y luego generarlos como se muestra a continuación.

Un registro de desplazamiento universal es un dispositivo que lo hace todo además de la función de entrada / salida en paralelo.

Arriba, aplicamos cuatro bits de datos a un registro de desplazamiento de entrada / salida en paralelo en D A D B D C D D . El control de modo, que puede ser de múltiples entradas, controla la carga paralela frente al cambio.

El control de modo también puede controlar la dirección de cambio en algunos dispositivos reales. Los datos se desplazarán una posición de bit por cada pulso de reloj.

Los datos desplazados están disponibles en las salidas Q A Q B Q C Q D . La "entrada de datos" y la "salida de datos" se proporcionan para la conexión en cascada de múltiples etapas.

Aunque, arriba, solo podemos enviar datos en cascada para el cambio a la derecha. Podríamos acomodar la cascada de datos de desplazamiento a la izquierda agregando un par de señales que apuntan a la izquierda, "entrada de datos" y "salida de datos", arriba.

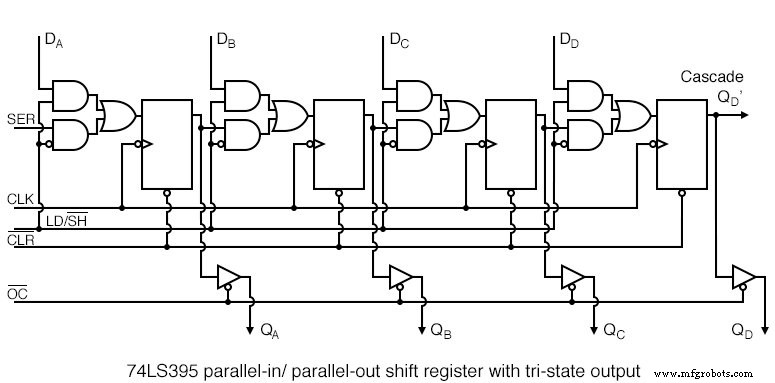

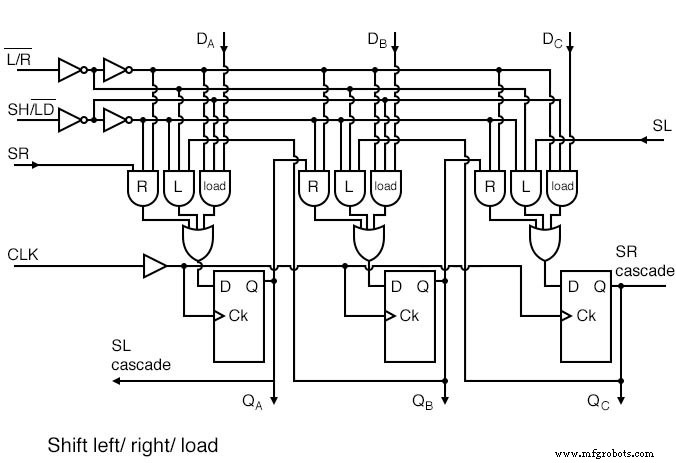

Los detalles internos de un registro de desplazamiento de entrada / salida en paralelo con desplazamiento a la derecha se muestran a continuación.

Los búferes de tres estados no son estrictamente necesarios para el registro de desplazamiento de entrada / salida en paralelo, pero son parte del dispositivo del mundo real que se muestra a continuación.

El 74LS395 coincide tanto con nuestro concepto de un registro de desplazamiento de entrada / salida en paralelo de desplazamiento a la derecha hipotético que usamos una versión demasiado simplificada de los detalles de la hoja de datos anterior.

Consulte el enlace a la hoja de datos completa para obtener más detalles, más adelante en este capítulo.

LD / SH ’ controla el multiplexor AND-OR en la entrada de datos a los FF. Si LD / SH "=1 , las cuatro puertas AND superiores están habilitadas permitiendo la aplicación de entradas paralelas D A D B D C D D a las cuatro entradas de datos FF.

Observe la burbuja del inversor en la entrada del reloj de los cuatro FF. Esto indica que el 74LS395 registra los datos en el reloj que va en negativo, que es la transición de alto a bajo.

Los cuatro bits de datos se sincronizarán en paralelo desde D A D B D C D D a Q A Q B Q C Q D en el siguiente reloj negativo. En esta "parte real", OC ’ debe ser bajo si los datos deben estar disponibles en los pines de salida reales en lugar de solo en los FF internos.

Los datos cargados previamente pueden desplazarse a la derecha en una posición de bit si LD / SH '=0 para los siguientes bordes negativos del reloj.

Cuatro relojes desplazarían los datos completamente fuera de nuestro registro de desplazamiento de 4 bits. Los datos se perderían a menos que nuestro dispositivo se conectara en cascada desde Q D " a SER de otro dispositivo.

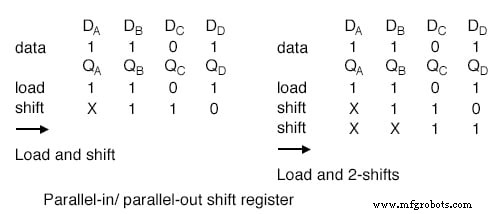

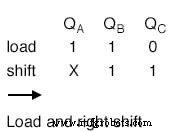

Arriba, se presenta un patrón de datos a las entradas D A D B D C D D . El patrón se carga en Q A Q B Q C Q D . Luego se desplaza un poco hacia la derecha.

Los datos entrantes se indican con X , es decir, no sabemos qué es. Si la entrada ( SER ) se basaron, por ejemplo, sabríamos qué datos ( 0 ) se cambió.

También se muestra el desplazamiento a la derecha en dos posiciones, lo que requiere dos relojes.

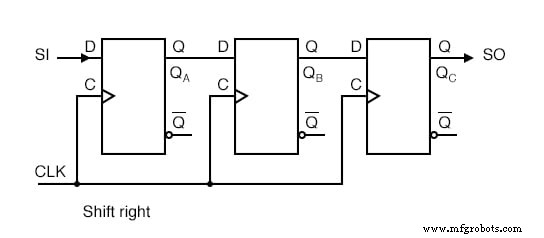

La figura anterior sirve como referencia para el hardware involucrado en el desplazamiento correcto de datos.

Es demasiado simple incluso molestarse con esta figura, excepto para la comparación con figuras más complejas a continuación.

El desplazamiento a la derecha de los datos se proporciona arriba como referencia al desplazador derecho anterior.

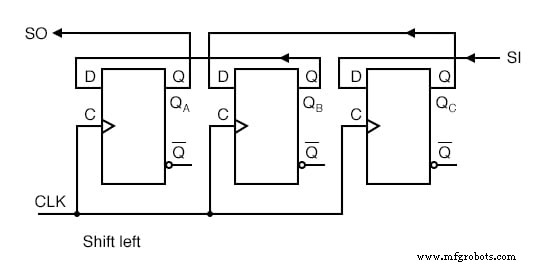

Si necesitamos desplazarnos a la izquierda, es necesario volver a cablear los FF. Compare con la palanca de cambios derecha anterior. Además, SI y SO han sido revertidos. SI cambia a Q C . Q C cambia a Q B . Q B cambia a Q A . Q A deja en el SO conexión, donde podría conectarse en cascada a otra palanca de cambios SI . Esta secuencia de cambio a la izquierda está al revés de la secuencia de cambio a la derecha.

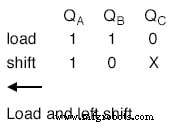

Arriba cambiamos el mismo patrón de datos a la izquierda un bit.

Hay un problema con la figura de "desplazamiento a la izquierda" anterior. No hay mercado para eso. Nadie fabrica una pieza de cambio a la izquierda.

Un "dispositivo real" que cambia una dirección se puede conectar externamente para cambiar la otra dirección. O, deberíamos decir que no hay izquierda o derecha en el contexto de un dispositivo que se desplaza en una sola dirección.

Sin embargo, existe un mercado para un dispositivo que se desplazará hacia la izquierda o hacia la derecha cuando lo ordene una línea de control. Por supuesto, la izquierda y la derecha son válidas en ese contexto.

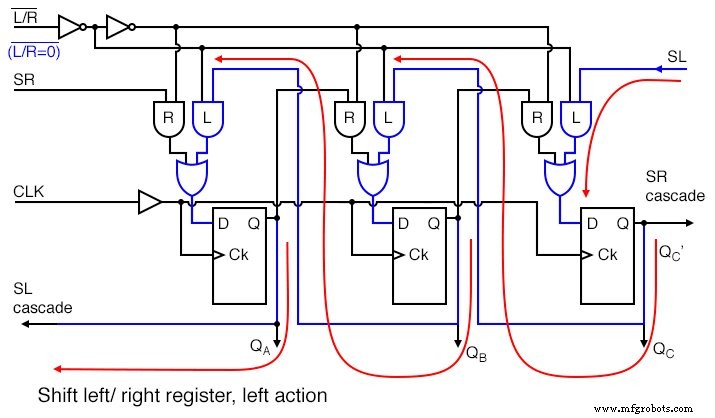

Lo que tenemos arriba es un registro de desplazamiento hipotético capaz de cambiar en cualquier dirección bajo el control de L '/ R .

Está configurado con L '/ R =1 para cambiar la dirección normal, a la derecha. L '/ R =1 habilita el multiplexor Y las puertas etiquetadas R .

Esto permite que los datos sigan la ruta ilustrada por las flechas, cuando se aplica un reloj. La ruta de conexión es la misma que la de la figura "demasiado simple" "desplazar a la derecha" anterior.

Los datos se desplazan en SR , a Q A , a Q B , a Q C , donde sale en SR cascada . Este pin podría conducir a SR de otro dispositivo a la derecha.

¿Qué pasa si cambiamos L '/ R a L '/ R =0 ?

Con L '/ R =0 , el multiplexor Y las puertas etiquetadas L están habilitados, produciendo una ruta, mostrada por las flechas, igual que la figura anterior de "desplazamiento a la izquierda".

Cambios de datos en SL , a Q C , a Q B , a Q A , de donde sale en SL cascada . Este pin podría conducir SL de otro dispositivo a la izquierda.

La principal virtud de las dos figuras anteriores que ilustran el "registro de desplazamiento izquierda / derecha" es la simplicidad.

El funcionamiento del control izquierdo derecho L '/ R =0 es fácil de seguir. Una parte comercial necesita la carga de datos paralela que implica el título de la sección. Esto aparece en la figura siguiente.

Ahora que podemos movernos tanto a la izquierda como a la derecha a través de L '/ R , agreguemos SH / LD ’ , shift / load, y las puertas AND etiquetadas como "load" para proporcionar la carga paralela de datos desde las entradas D A D B D C .

Cuando SH / LD "=0 , Y puertas R y L están deshabilitados, Y las puertas de "carga" están habilitadas para pasar datos D A D B D C a las entradas de datos FF. el próximo reloj CLK sincronizará los datos con Q A Q B Q C .

Siempre que estén presentes los mismos datos, se volverán a cargar en los relojes siguientes. Sin embargo, los datos presentes para un solo reloj se perderán de las salidas cuando ya no estén presentes en las entradas de datos.

Una solución es cargar los datos en un reloj y luego pasar a los siguientes cuatro relojes. Este problema se soluciona en el 74ALS299 agregando otra puerta AND al multiplexor.

Si SH / LD ’ se cambia a SH / LD ’=1 , las puertas AND etiquetadas como "carga" están deshabilitadas, lo que permite el control izquierdo / derecho L '/ R para establecer la dirección de cambio en L o R Y puertas. El cambio es como en las figuras anteriores.

Lo único que se necesita para producir un dispositivo integrado viable es agregar la cuarta puerta AND al multiplexor como se mencionó para el 74ALS299.

Esto se muestra en la siguiente sección de esa parte.

Dispositivos universales y de entrada y salida en paralelo

Echemos un vistazo más de cerca a los registros de desplazamiento de entrada en serie / salida en paralelo disponibles como circuitos integrados, cortesía de Texas Instruments.

Para obtener hojas de datos completas del dispositivo, siga los enlaces.

-

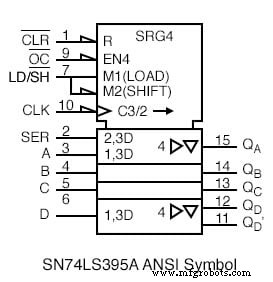

Registro de desplazamiento de 4 bits de entrada / salida en paralelo SN74LS395A

-

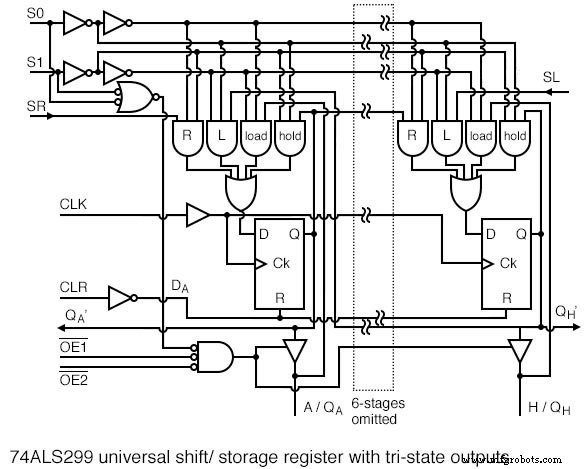

Registro de desplazamiento universal de 8 bits de entrada / salida en paralelo SN74ALS299

Ya hemos analizado los detalles internos del SN74LS395A, consulte la figura anterior, registro de desplazamiento de entrada / salida en paralelo 74LS395 con salida de tres estados.

Justo encima está el símbolo ANSI del 74LS395.

Por qué solo 4 bits, como lo indica SRG4 ¿sobre? Tener entradas y salidas paralelas, además de pines de control y alimentación, no permite más bits de E / S (entrada / salida) en un DIP (paquete dual en línea) de 16 pines.

R indica que las etapas del registro de desplazamiento se restablecen mediante la entrada CLR ’ (media flecha de inversión baja activa en la entrada) de la sección de control en la parte superior del símbolo. OC ’ , cuando está bajo, (invertir la flecha de nuevo) habilitará ( EN4 ) los cuatro búferes de salida de tres estados ( Q A Q B Q C Q D ) en la sección de datos.

Carga / turno "( LD / SH" ) en el pin (7) corresponde a los internos M1 (carga) y M2 (cambio). Busque prefijos de 1 y 2 en el resto del símbolo para determinar qué es controlado por estos.

El reloj sensible al borde negativo (indicado por la flecha invertida en el pin-10) C3 / 2 tiene dos funciones.

Primero, el 3 de C3 / 2 afecta a cualquier entrada que tenga un prefijo de 3 , digamos 2,3D o 1,3D en la sección de datos.

Esta sería una carga paralela en A, B, C, D atribuido a M1 y C3 para 1,3D . Segundo, 2 de C3 / 2 -La flecha derecha indica la sincronización de datos siempre que 2 aparece en un prefijo ( 2,3D en el pin-2).

Por lo tanto, tenemos un reloj de datos en SER en Q A con modo 2 . La flecha hacia la derecha después de C3 / 2 cuentas para el cambio en las etapas del registro de turnos interno Q A Q B Q C Q D .

Los triángulos que apuntan a la derecha indican almacenamiento en búfer; el triángulo invertido indica tri-estado, controlado por EN4 .

Tenga en cuenta que todos los 4 s en el símbolo asociado con EN se omiten con frecuencia. Etapas Q B Q C se entiende que tienen los mismos atributos que Q D . Q D " cae en cascada al SER del siguiente paquete a la derecha.

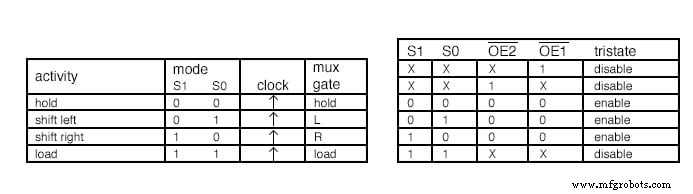

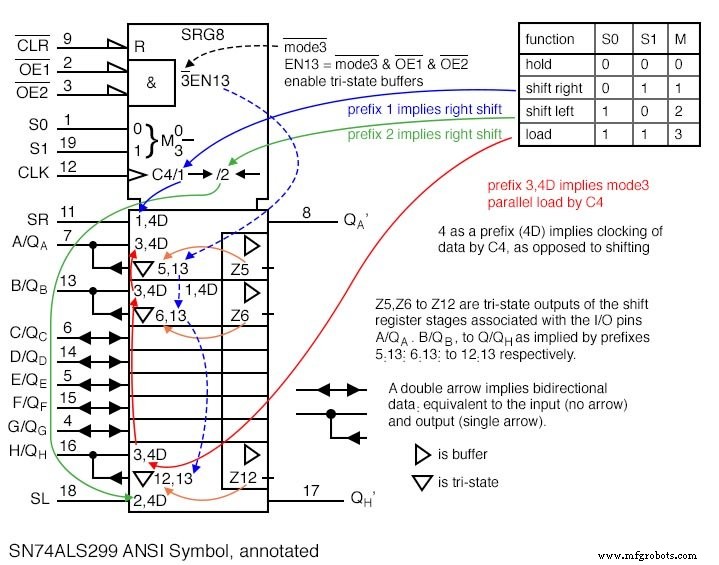

La tabla anterior, resumida de la hoja de datos 299 de datos, resume el funcionamiento del registro universal de desplazamiento / almacenamiento 74ALS299.

Siga el enlace '299 anterior para obtener todos los detalles. Las puertas del multiplexor R , L , cargar operar como en las figuras anteriores de "desplazamiento de registro de izquierda / derecha".

La diferencia es que el modo ingresa S1 y S0 seleccione desplazar a la izquierda, desplazar a la derecha y cargar con el modo configurado en S1 S0 = a 01 , 10 y 11 respectivamente, como se muestra en la tabla, habilitando las puertas del multiplexor L , R y cargar respectivamente.

Ver tabla. Una pequeña diferencia es la ruta de carga paralela de las salidas de tres estados. En realidad, los búferes de tres estados están (deben estar) deshabilitados por S1 S0 =11 para hacer flotar el bus de E / S para usar como entradas.

Un bus es una colección de señales similares. Las entradas se aplican a A , B hasta H (los mismos pines que Q A , Q B , a través de Q H ) y enrutado a la carga puerta en los multiplexores, y en el D insumos de los FF. Los datos son carga paralela en un pulso de reloj.

La única puerta del multiplexor nueva es la puerta AND etiquetada como retención , habilitado por S1 S0 =00 . La bodega puerta habilita un camino desde el Q salida del FF a la bodega puerta, a la entrada D del mismo FF. El resultado es que con el modo S1 S0 =00 , la salida se recarga continuamente con cada nuevo pulso de reloj. Por lo tanto, se mantienen los datos. Esto se resume en la tabla.

Para leer datos de las salidas Q A , Q B , a través de Q H , los búferes de tres estados deben estar habilitados por OE2 ’, OE1’ =00 y modo = S1 S0 =00, 01 o 10 .

Es decir, el modo es cualquier cosa excepto cargar . Consulte la segunda tabla.

Desplazar datos a la derecha de un paquete a la izquierda, cambios en el SR aporte. Cualquier dato desplazado hacia la derecha desde la etapa Q H cascadas a la derecha a través de Q H ".

Esta salida no se ve afectada por los búferes de tres estados. La secuencia de desplazamiento a la derecha para S1 S0 =10 es:

SR> Q A > Q B > Q C > Q D > Q E > Q F > Q G > Q H (Q H ’)

Los datos de desplazamiento a la izquierda de un paquete a la derecha se desplazan en el SL aporte. Cualquier dato desplazado hacia la izquierda desde la etapa Q A cascadas a la izquierda a través de Q A ’, Que tampoco se ve afectado por los amortiguadores de tres estados. La secuencia de desplazamiento a la izquierda para S1 S0 =01 es:

(Q A ’) Q A B

C

D

E

F

G

H (Q SL ’)

El cambio puede tener lugar con los búferes de tres estados inhabilitados por uno de OE2 ’ o OE1 ’=1 . Sin embargo, no se podrá acceder a las salidas de los contenidos del registro. Ver tabla.

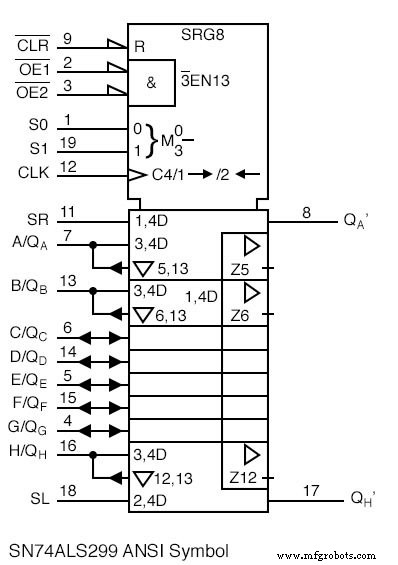

El símbolo ANSI "limpio" para el registro de desplazamiento universal de 8 bits de entrada / salida en paralelo SN74ALS299 con salida de tres estados se muestra como referencia arriba.

Se muestra la versión anotada del símbolo ANSI para aclarar la terminología que contiene.

Tenga en cuenta que el modo ANSI (S0 S1) se invierte del orden (S1 S0) utilizado en la tabla anterior.

Eso invierte los números del modo decimal (1 y 2). En cualquier caso, estamos totalmente de acuerdo con la hoja de datos oficial, copiando esta inconsistencia.

Aplicaciones prácticas

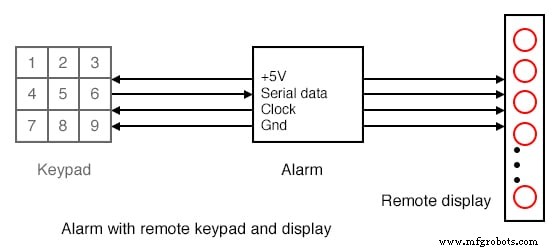

El diagrama de bloques de Alarma con teclado remoto se repite a continuación. Anteriormente, construimos el lector de teclado y la pantalla remota como unidades separadas.

Ahora combinaremos el teclado y la pantalla en una sola unidad usando un registro de desplazamiento universal.

Aunque separados en el diagrama, el teclado y la pantalla están contenidos en el mismo gabinete remoto.

Cargaremos en paralelo los datos del teclado en el registro de desplazamiento en un solo pulso de reloj, luego lo cambiaremos a la caja de alarma principal.

Al mismo tiempo, cambiaremos los datos del LED de la alarma principal al registro de cambio remoto para iluminar los LED.

Estaremos desplazando simultáneamente los datos del teclado y los datos del LED al registro de desplazamiento.

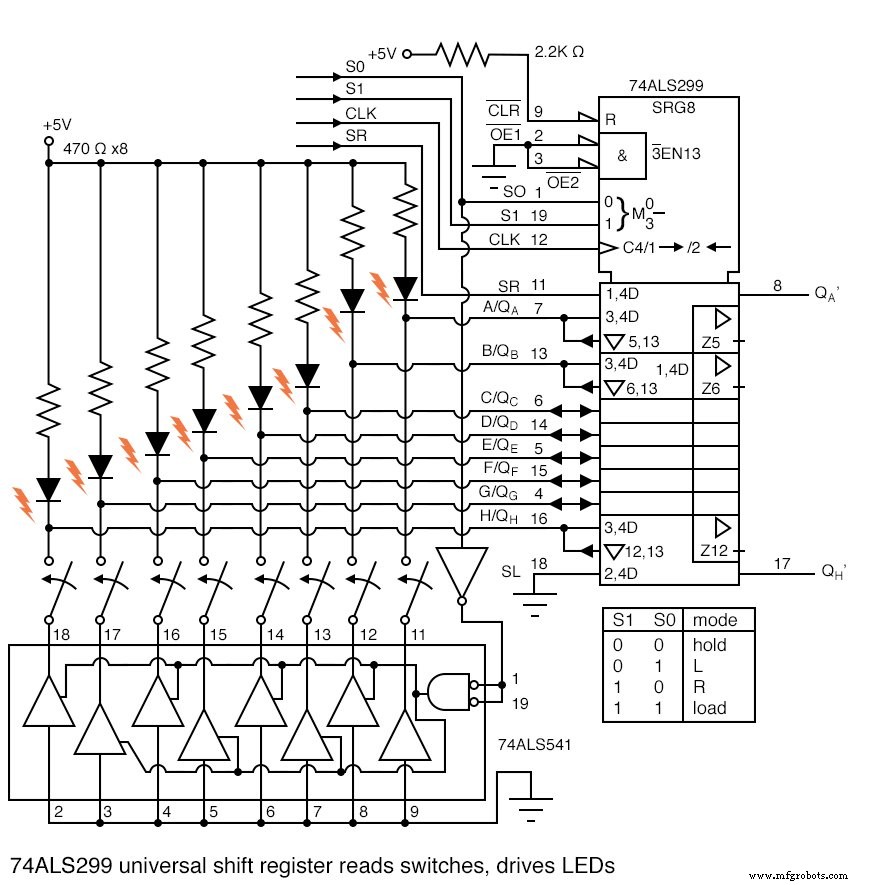

Ocho LED y resistencias limitadoras de corriente están conectados a los ocho pines de E / S del registro de desplazamiento universal 74ALS299.

Los LED solo se pueden manejar durante el Modo 3 con S1 =0 S0 =0 . El OE1 ’ y OE2 ’ Las habilitaciones de tres estados están conectadas a tierra para habilitar permanentemente las salidas de tres estados durante los modos 0, 1, 2 .

Eso hará que los LEDS se enciendan (parpadeen) durante el cambio. Si esto fuera un problema, el EN1 "Y EN2" podría no tener conexión a tierra y estar en paralelo con S1 y S0 respectivamente para habilitar solo los búferes triestado y encender los LEDS durante la espera, modo 3 . Mantengamos las cosas simples para este ejemplo.

Durante la carga paralela, S0 =1 invertido a 0, permite que los búferes octales triestado conecten a tierra los limpiaparabrisas del interruptor.

Los contactos superiores abiertos del interruptor se elevan a un nivel lógico alto mediante la combinación de LED de resistencia en las ocho entradas.

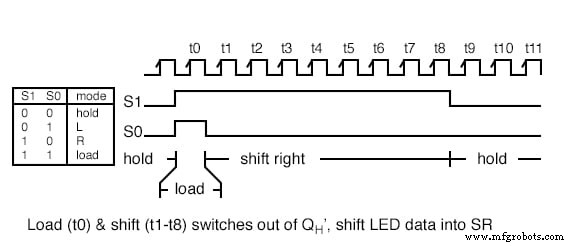

Cualquier cierre de interruptor acortará la entrada baja. Cargamos en paralelo los datos del conmutador en el ‘299 en el reloj t0 cuando ambos S0 y S1 son altos. Vea las formas de onda a continuación.

Una vez S0 baja, ocho relojes ( t0 a t8 ) cambiar los datos de cierre del interruptor de la ‘299 a través de Q h " alfiler.

Al mismo tiempo, los nuevos datos LED se transfieren a SR de las 299 por los mismos ocho relojes. Los datos del LED reemplazan los datos de cierre del interruptor a medida que avanza el cambio.

Después del reloj del octavo turno, t8 , S1 baja al modo de retención de rendimiento ( S1 S0 =00 ). Los datos en el registro de desplazamiento siguen siendo los mismos incluso si hay más relojes, por ejemplo, T9 , t10 , etc.

¿De dónde proceden las formas de onda? Podrían ser generados por un microprocesador si la frecuencia de reloj no fuera superior a 100 kHz, en cuyo caso, sería inconveniente generar relojes después de t8 .

Si el reloj estuviera en el rango de megahercios, el reloj funcionaría continuamente. El reloj, S1 y S0 sería generado por lógica digital, no se muestra aquí.

HOJAS DE TRABAJO RELACIONADAS:

- Hoja de trabajo de registros de turnos

Tecnología Industrial

- Protocolos de red

- ¿Por qué digital?

- Microprocesadores

- Datos del amplificador operacional

- Datos de descargas eléctricas

- La fabricación basada en datos está aquí

- Poniendo tus datos a trabajar

- ¿Qué es IIoT?

- Big Data vs Inteligencia Artificial

- Códigos de matriz de datos frente a códigos QR

- ¿Qué son los datos de mantenimiento?