Debut de chips de inteligencia artificial neuromórfica para aumentar las redes neuronales

Innatera, la startup holandesa que fabrica aceleradores de inteligencia artificial neuromórfica para aumentar las redes neuronales , ha producido sus primeros chips, ha medido su rendimiento y ha revelado detalles de su arquitectura.

Innatera, la startup holandesa que fabrica aceleradores de IA neuromórficos para aumentar las redes neuronales, ha producido sus primeros chips, ha evaluado su rendimiento y ha revelado detalles de su arquitectura.

La compañía también anunció que el cofundador de Cadence and Synopsys, Alberto Sangiovanni-Vincentelli, se unió a la compañía como presidente de su junta directiva. El veterano de la industria es actualmente profesor en la Universidad de California en Berkeley.

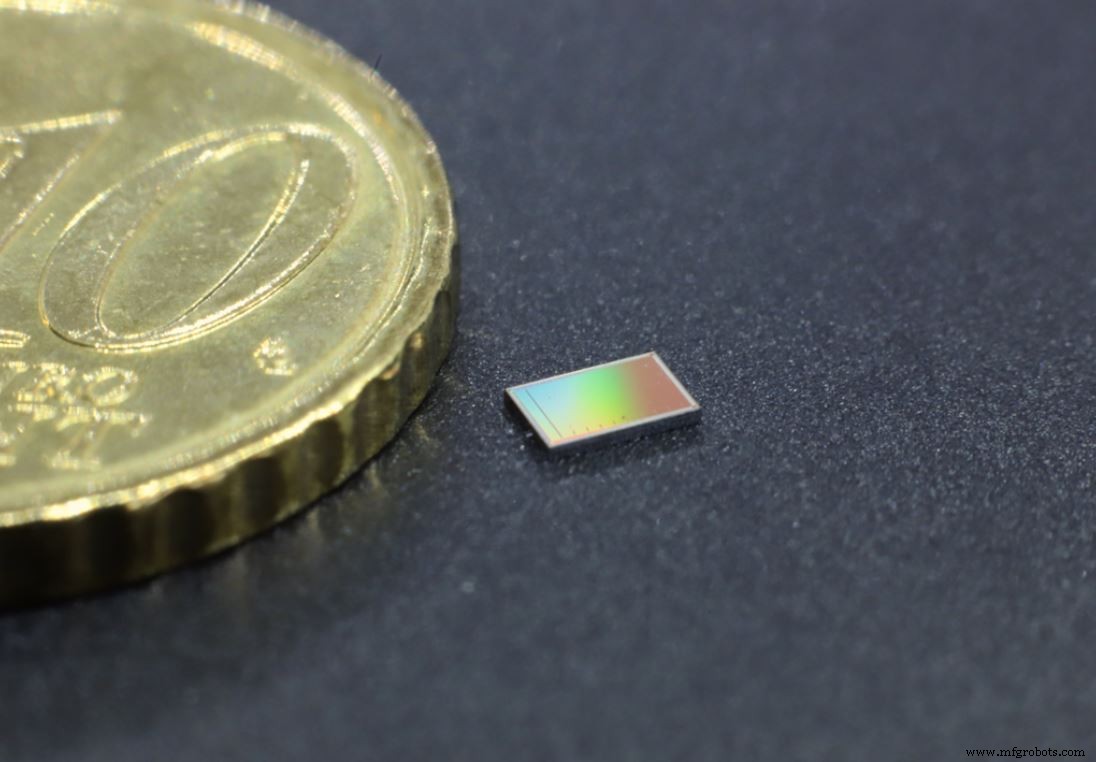

El chip de Innatera está diseñado para acelerar diferentes SNN para aplicaciones de audio, salud y radar (Imagen:Innatera)

El chip Innatera está diseñado para acelerar las redes neuronales de picos (SNN), un tipo de algoritmo de inteligencia artificial neuromórfica basado en la biología del cerebro que utiliza la sincronización de los picos en una señal eléctrica para realizar tareas de reconocimiento de patrones. Los SNN son completamente diferentes en estructura de los algoritmos de IA convencionales y, por lo tanto, requieren hardware dedicado para la aceleración, pero generalmente ofrecen importantes ventajas de latencia y consumo de energía para las aplicaciones del borde del sensor.

La mayoría de las otras empresas que trabajan en la mejora de algoritmos y hardware de redes neuronales (por ejemplo, Prophesee) tienen como objetivo imágenes y transmisiones de video. Innatera ha decidido centrarse en el audio (reconocimiento de voz y sonido), la salud (monitoreo de signos vitales) y el radar (para casos de uso de consumidores / IoT, como sensores de caída de personas mayores que mantienen la privacidad).

Marco Jacobs (Imagen:Innatera)

"Estos sensores tienen datos de series de tiempo, en lugar de imágenes que son muy paralelas", dijo Marco Jacobs, vicepresidente de marketing y desarrollo comercial de Innatera, en una entrevista con EE Times . “Nuestra matriz es especialmente buena para procesar datos de series de tiempo ... es una buena tecnología. Además, desde la perspectiva del mercado, vemos muchas aplicaciones interesantes en esta área y no tantas soluciones que la aborden ”.

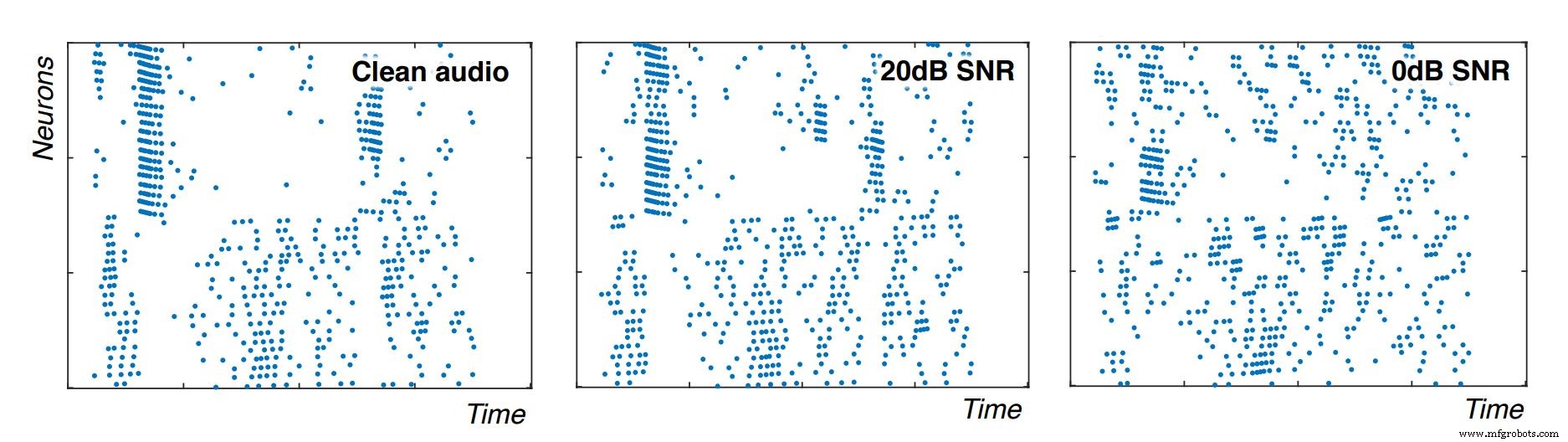

Otra cosa que estas tres aplicaciones tienen en común es que, dado que se requiere procesamiento en el nodo del sensor, la envolvente de potencia es muy ajustada. En las pruebas de Innatera, cada evento de pico (cada neurona que se dispara en respuesta a los datos de entrada) requirió menos de un picoJoule de energía, en realidad, menos de 200 femtoJoules en TSMC 28nm, confirmó Innatera. Esto se acerca a la cantidad de energía utilizada por las neuronas biológicas y las sinapsis. Una aplicación típica de detección de palabras clave de audio requería menos de 500 eventos de picos por inferencia, lo que resultaba en una "disipación de energía profunda de menos de milivatios", según el CEO de Innatera, Sumeet Kumar. En este caso, los grupos de neuronas que se activan juntas representan diferentes fonemas en el habla.

Los grupos de neuronas que se disparan (aquí grupos de puntos) representan la detección de fonemas en el habla. A medida que los datos de entrada incorporan más ruido, los mismos grupos están presentes en su mayoría, aunque son más difíciles de detectar (Imagen:Innatera)

Arquitectura de procesamiento

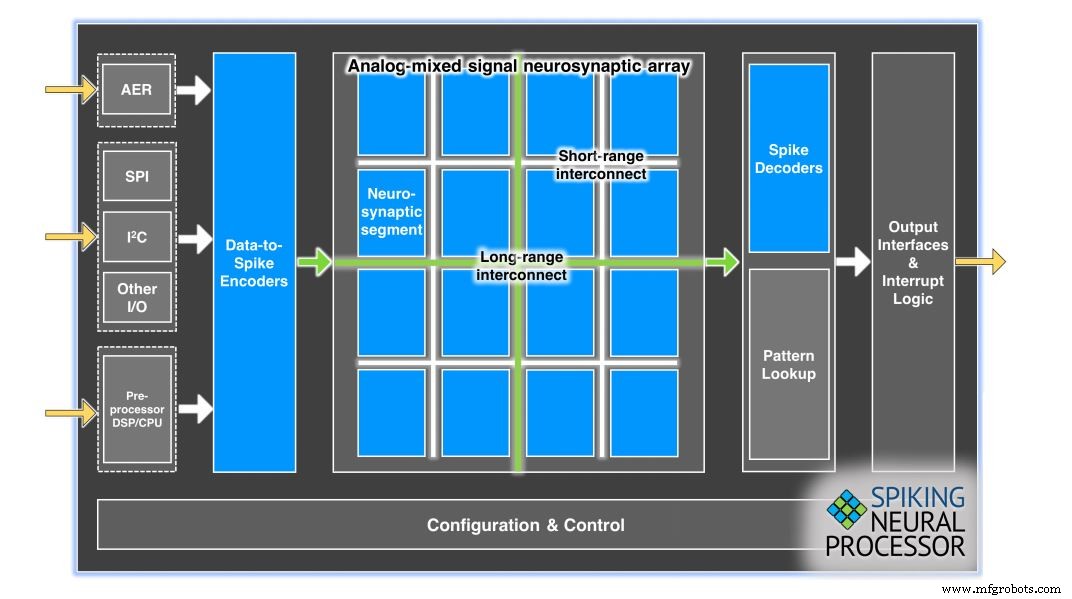

El procesador neuronal de picos de Innatera utiliza una matriz paralela de neuronas y sinapsis de picos para acelerar los SNN de tiempo continuo con una dinámica temporal de grano fino. El dispositivo es un acelerador de señal analógica / mixta diseñado para aprovechar la capacidad de SNN de incorporar la noción de tiempo en la forma en que se procesan los datos.

El procesador neuronal de picos de Innatera incluye una matriz neuro-sináptica masivamente paralela y codificadores y decodificadores de picos (Imagen:Innatera)

Uno de los aspectos clave de los tejidos informáticos de Innatera es su programabilidad, que es importante por dos razones.

Primero, programar diferentes SNN en el chip. Las neuronas deben estar conectadas de manera flexible:el cerebro utiliza topologías de redes neuronales muy complejas para hacer las cosas de manera eficiente, lo que requiere conexiones complejas entre neuronas, que deben recrearse en silicio.

Sumeet Kumar (Imagen:Innatera)

En segundo lugar, optimizar el rendimiento. En lugar de representar la información como bits en palabras, en un SNN la información se representa como picos cronometrados con precisión. La sincronización de los picos debe manipularse a un nivel muy detallado para extraer información sobre los datos. Por lo tanto, las neuronas y las conexiones entre ellas (las sinapsis) deben exhibir comportamientos de sincronización complejos. Estos comportamientos se pueden ajustar a través del SDK de Innatera para optimizar el rendimiento.

Innatera describe su chip como señal analógica mixta o "analógica asistida digitalmente". Las neuronas y las sinapsis se implementan en silicio analógico para mantener un consumo de energía ultrabajo. La electrónica analógica también permite redes de tiempo continuo (la electrónica digital requeriría discretización). Esto es importante para los SNN porque su naturaleza significa que tienen inherentemente una noción de tiempo y necesitan poder mantener estados particulares durante un período de tiempo.

"Hacer esto es mucho más fácil en el dominio analógico:no es necesario cambiar la complejidad de mantener el estado en la topología de la red", dijo Kumar. “Nuestros elementos informáticos retienen naturalmente esa información de estado. Esta es la razón por la que hacemos cosas en el dominio analógico ”.

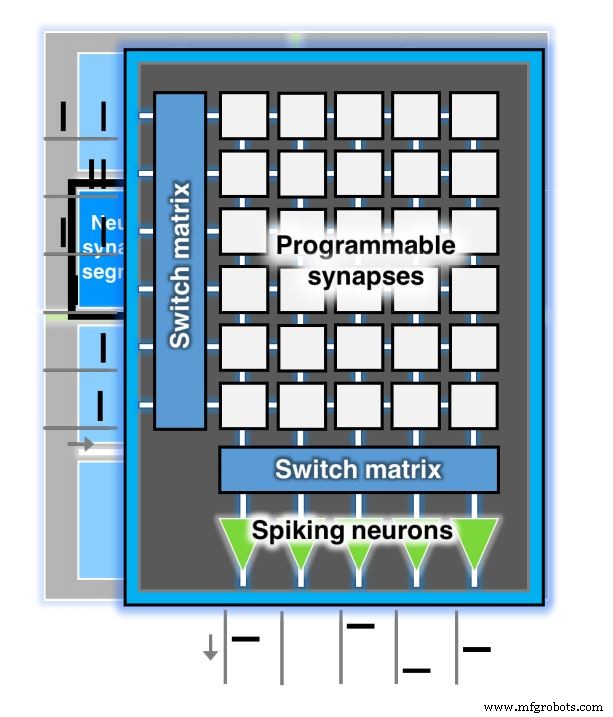

Un segmento de cómputo en la matriz de Innatera, donde las neuronas están diseñadas para emparejarse cuidadosamente. Las sinapsis programables están dispuestas en una estructura de barra transversal de varios niveles. (Las líneas negras / guiones aquí representan picos de entrada y salida) (Imagen:Innatera)

Las inconsistencias menores en la fabricación entre los elementos de cómputo en el chip y entre diferentes chips pueden ser un problema para implementar redes neuronales con precisión en el dominio analógico. La solución de Innatera es agrupar neuronas en lo que llama segmentos, que están cuidadosamente diseñados para coincidir con las longitudes de ruta y el número de neuronas.

El diseño del segmento “esencialmente nos permite utilizar lo mejor de los circuitos analógicos mientras minimizamos estas no idealidades que normalmente tendríamos en un circuito analógico”, dijo Kumar. "Todo esto se hizo esencialmente para asegurarse de que las neuronas dentro de un segmento exhiban un comportamiento determinista y funcionen de una manera similar a sus vecinas inmediatas".

Las inconsistencias entre diferentes chips pueden causar problemas cuando la misma red entrenada se implementa en dispositivos en el campo. Innatera soluciona esto con software.

“Las discrepancias y la variabilidad se tratan en lo más profundo del SDK”, dijo Kumar. "Si es un usuario avanzado, podemos exponerle algo de eso, pero un programador típico no necesita preocuparse por eso".

Específico de la aplicación

Innatera, una empresa derivada de la Universidad Tecnológica de Delft, ya estaba trabajando con clientes de ingresos en sus algoritmos SNN antes de pasar al hardware y recaudar una ronda inicial de € 5 millones (alrededor de $ 6 millones) hacia fines de 2020.

"Hemos estado trabajando con varios clientes desde el momento en que comenzamos la empresa, y estos compromisos aún están en curso; han madurado de manera muy significativa", dijo Kumar. "Esperamos poder mostrar más demostraciones junto con algunos de estos clientes en la última parte de este año".

Kumar dijo que la empresa mantiene su enfoque como empresa de soluciones informáticas, es decir, proporcionará soluciones llave en mano que incluyen tanto hardware como algoritmos SNN específicos de la aplicación.

El primer chip de Innatera es adecuado para aplicaciones de audio, salud y radar. La hoja de ruta de la empresa podría incluir chips optimizados para cada una de las aplicaciones.

"Diseñamos el dispositivo de tal manera que pudiéramos acelerar una amplia variedad de redes neuronales de picos", dijo Kumar. “[Nuestro chip] puede implementar estas redes en todos los dominios de aplicaciones. Pero a medida que profundizamos en los dominios, puede ser necesario optimizar el diseño del hardware, y esto es algo que veremos en el futuro. En este momento, el hardware no está demasiado especializado en ninguna clase específica de aplicaciones o en ningún estilo de redes neuronales con picos, el objetivo es admitir una variedad de ellas generalmente dentro de la arquitectura ".

Las muestras del chip inicial están en camino de estar disponibles antes de finales de 2021.

>> Este artículo se publicó originalmente en nuestro sitio hermano, EE. Tiempos.

Contenidos relacionados:

- El chip AI apunta a dispositivos periféricos de bajo consumo

- La cadena de herramientas y la placa de sensores mejoran el ecosistema de chips de IA

- Los nuevos módulos de aceleración de IA mejoran el rendimiento del borde

- IA en el borde:qué buscar en 2021

- Cómo implementar AI of Things (AIoT) en MCU

Para obtener más información sobre Embedded, suscríbase al boletín informativo semanal por correo electrónico de Embedded.

Incrustado

- Co-simulación para diseños basados en Zynq

- Renesas:chips automotrices adoptados por Nissan para su nuevo Skyline ProPILOT 2.0

- CEVA:procesador de inteligencia artificial de segunda generación para cargas de trabajo de redes neuronales profundas

- Defensa de los chips neuromórficos para la informática de IA

- El chip de radar de baja potencia utiliza redes neuronales con picos

- Lanner:puerta de enlace de borde lista para LTE certificada para IoT y SD-WAN en redes celulares

- IBM en SPIE:Siete avances para chips de más de 7 nm

- NPE es el debut de Campetella Robotic Center en EE. UU.

- 3G ha muerto:¿qué sigue para los diseñadores de productos?

- LoRaWAN reemplazará temporalmente las redes 5G para IoT

- Lattice Semiconductor lanza chips especialmente diseñados para la automatización industrial