IBM en SPIE:Siete avances para chips de más de 7 nm

Cuando anunciamos los primeros chips de prueba funcionales de 7 nanómetros (7 nm) de la industria en 2015, con nuestros socios GLOBALFOUNDRIES y Samsung, sabíamos que el proceso para que los chips alcanzaran la "madurez de fabricación", tal vez el próximo año, sería rápido. A medida que ese esfuerzo se acelera en la industria de los semiconductores, IBM continúa ampliando los límites al enfocarse en los desafíos de los próximos nodos más allá de 7 nm.

Nuestro equipo de IBM presentará siete artículos en la conferencia de litografía avanzada de la Sociedad Internacional de Óptica y Fotónica (SPIE) 2017 de esta semana centrado en la exploración y habilitación de tecnología más allá del nodo de 7 nm. Y comienza con la litografía ultravioleta extrema (EUV).

Nuestro equipo de IBM presentará siete artículos en la conferencia de litografía avanzada de la Sociedad Internacional de Óptica y Fotónica (SPIE) 2017 de esta semana centrado en la exploración y habilitación de tecnología más allá del nodo de 7 nm. Y comienza con la litografía ultravioleta extrema (EUV).

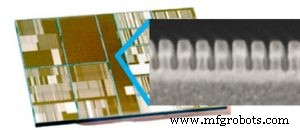

Con chips de 7 nm, ahora estamos creando diseños relacionados con el tamaño de un transistor, o incluso el cableado entre los transistores, que son verdaderamente a nivel atómico. Para lograr este tipo de escala sin esquemas de patrones demasiado complejos, EUV es clave. En una sola exposición, EUV puede crear un patrón de alta resolución que es inalcanzable por procesos previos de modelado de semiconductores. Sin embargo, habilitar la creación de patrones EUV requiere equipos, procesos y conocimientos especializados, todos los cuales se encuentran en los laboratorios de investigación de IBM en Albany, NY y Yorktown Heights, NY. Estos siete avances presentados en SPIE relacionados con las máscaras EUV (plantillas que se utilizan para imprimir diseños de circuitos en una oblea de silicio) y materiales de modelado (materiales "resistentes" activados por la luz o resistentes al grabado), pueden considerarse críticos para habilitar la tecnología de 7 nm. y más allá:

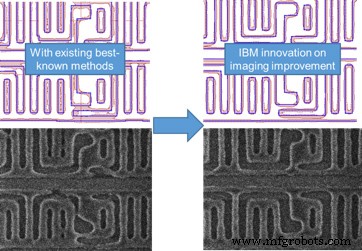

En Optimización de la intención de diseño en el nodo más allá de los 7 nm:la intersección de las técnicas de mitigación estocástica DTCO y EUVL , Michael Crouse muestra que aunque el título de su charla es grande, pequeños cambios en los diseños de cableado pueden mejorar drásticamente las condiciones de impresión. En la Figura 1, muestra que si la optimización de las formas de la máscara se realiza correctamente, se pueden imprimir líneas continuas sin roturas en las dimensiones más pequeñas requeridas para el nodo de 7 nm y más.

Figura 1 :Mejora de la optimización del contraste en cableado metálico bidimensional demostrado con litografía EUV. Con el tipo de mejora que se ilustra a la derecha, las características 20-30 {ccf696850f4de51e8cea028aa388d2d2d2eef894571ad33a4aa3b26b43009887} más pequeñas que las del nodo de 7 nm se pueden imprimir de manera más sólida y la variabilidad física / eléctrica se puede reducir drásticamente.

En Investigación de pilas de máscaras alternativas en litografía EUV, Martin Burkhardt simula el rendimiento de nuevos materiales que no se utilizan actualmente para las máscaras EUV. Al considerar toda la tabla periódica, puede ilustrar que las máscaras EUV que proporcionan un contraste aún mejor están a nuestro alcance. En realidad, fabricar máscaras con algunos de estos materiales permitiría patrones de mayor fidelidad en una oblea de silicio sin ningún cambio adicional en la tecnología EUV y, por lo tanto, permitiría que la industria escale fácilmente más allá de los 7 nm.

En Análisis completo de la rugosidad del borde y del ancho de línea para la litografía EUV , Ravi Bonam ilustra cómo las pequeñas imperfecciones y ondulaciones en una línea de cableado se pueden caracterizar claramente y, al hacerlo, muestra qué condiciones producen las características más rectas, críticas para mejorar la capacidad de fabricación del proceso de modelado EUV y el rendimiento y el rendimiento del chip.

En Fundamentos de las interacciones entre la máscara rígida inorgánica y la resistencia EUV , Dario Goldfarb busca mejorar la pila de películas del material de modelado (el punto de transferencia del patrón a la oblea) mejorando las interacciones físicas y químicas en las interfaces entre estas películas, que a menudo no les gusta pegarse entre sí. Él aprovecha este conocimiento para crear interacciones químicas específicas para mantener juntos estos materiales (que se muestran en la Figura 2), lo cual es fundamental para garantizar que estas pequeñas formas con patrones de EUV puedan permanecer en su lugar el tiempo suficiente para transferir sus patrones al sustrato de abajo.

Figura 2 :Una resistencia EUV que antes era imposible de modelar en una máscara dura de silicio inorgánico ahora se puede modelar claramente después de la personalización de la superficie adaptada a la combinación de resistencia / máscara dura.

En un tema similar al de la charla de Dario Goldfarb, Indira Seshadri hace una demostración en pila de patrones Ultrathin EUV usando un pincel de polímero como capa de promoción de la adhesión , que al emplear un material similar a un polímero que une las características diminutas con patrones de EUV y el sustrato subyacente, estos patrones de muy alta resolución se pueden grabar en el sustrato de abajo y conservar la forma de diseño deseada, clave para garantizar chips rendibles a esta longitud. escamas.

Con tantas nuevas soluciones de película delgada en juego, la capacidad de discernir y mejorar los procesos dignos de fabricación al principio de las fases de investigación es clave. En una charla titulada Reducir la densidad de defectos en las pilas de películas de modelado EUV compuestas , Luciana Meli demuestra estudios de casos sistemáticos, utilizando un híbrido de técnicas de inspección de defectos disponibles, para mostrar las mejoras de procesos y materiales necesarias para ofrecer la baja defectividad requerida para 7nm y más allá de la capacidad de fabricación EUV.

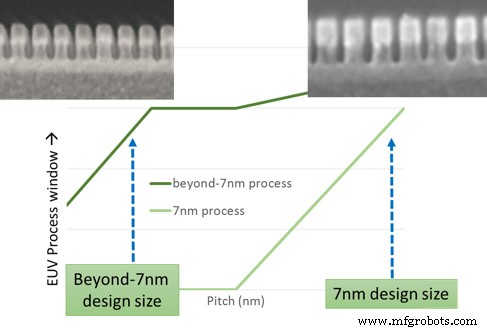

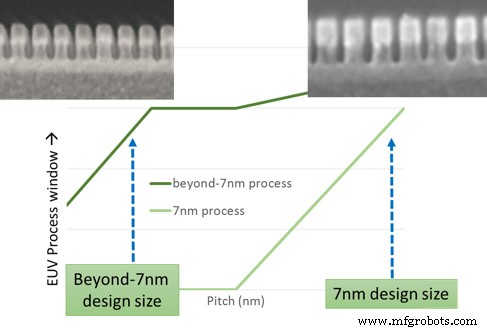

Al reunir muchos de estos conceptos de imágenes y mejoras de materiales, Anuja De Silva presentará una charla titulada Desarrollo de patrones de exposición única para litografía EUV , mostrando patrones exitosos de circuitos de cableado en las dimensiones de 30 nm e inferiores requeridas más allá del nodo de 7 nm. La capacidad para lograr esto representa un gran salto con respecto a las capacidades disponibles por primera vez para el nodo de 7 nm (ver Figura 3), y en realidad puede mejorar el nodo de 7 nm en sí, aunque ella destacará los desafíos que aún quedan para permitir chips productivos y en pleno funcionamiento en dimensiones requeridas para la tecnología más allá de 7 nm.

Un chip de 7 nm tiene 20 mil millones de transistores en el espacio aproximadamente del tamaño de una uña. Se abrirán camino en los sistemas y dispositivos, ampliando las capacidades, y la Ley de Moore, para realizar tareas cada vez más exigentes en el análisis de datos, la computación cognitiva y lo que sea que tenga la próxima generación de aplicaciones móviles. El trabajo presentado en SPIE este año acerca a la industria a soluciones de patrones que no solo hacen que el proceso de 7 nm sea más robusto con EUV de exposición única, sino que también permiten un mayor escalado para obtener aún más beneficios de potencia / rendimiento en los próximos años.

Figura 3 :La innovación en múltiples aspectos del proceso de creación de patrones permite a IBM ofrecer una capacidad de proceso de creación de patrones holística para ofrecer los tamaños de características necesarios más allá del nodo de 7 nm.

Otras presentaciones de IBM en 2017 SPIE

Optimización de la intención del diseño en el nodo más allá de los 7 nm:la intersección de las técnicas de mitigación estocásticas DTCO y EUVL , Michael Crouse, Nicole Saulnier, Derren Dunn

Investigación de pilas de máscaras alternativas en litografía EUV , Martin Burkhardt

Descomposición del TCC utilizando núcleos no coherentes para un cálculo más rápido de imágenes litográficas, Alan Rosenbluth

Desarrollo de máscaras duras que contienen Ti a través de la deposición PEALD, Anuja De Silva

Opciones de patrones de DSA para aplicaciones lógicas y de memoria, Charlie Liu

Estudio eléctrico del proceso de contracción DSA y el efecto de rectificación de CD a menos de 60 nm utilizando un vehículo de prueba EUV, Cheng Chi

Alcanzando la superposición verdadera en nodos avanzados, Chiew-Seng Koay

Estrategias sin capa superior para el control de la orientación de copolímeros de bloque alto totalmente orgánicos Dan Sanders

Análisis de sensibilidad de identificación y confiabilidad de un sistema de reglas básicas correlacionado (arco de diseño), Eric Eastman

Calibración y desarrollo de modelos DSA 3D rápidos y avanzados para la optimización conjunta de la tecnología de diseño Kafai Lai

Impactos inesperados de los gases RIE en las películas litográficas Martin Glodde

Predicción de pruebas eléctricas mediante metrología híbrida y aprendizaje automático, Mary Breton

Reducción de LER en Si y SiN mediante la optimización de RIE para aplicaciones de guías de ondas fotónicas, Nathan Marchack

Estrategias de creación de patrones de autoensamblaje dirigidas para aplicaciones de memoria de cambio de fase, R. Bruce

Caracterización de materiales para la integración de procesos de dispositivos de puerta multicanal en todos lados (GAA), Raja Muthinti

Análisis completo de la rugosidad del borde y del ancho de línea para la litografía EUV, Ravi Bonam

Nanomateriales

- Blanco de aleación de tungsteno y titanio para chips

- Objetivo de tungsteno de alta pureza para chips semiconductores

- Vaya más allá de los requisitos mínimos de red de Skype para obtener los mejores resultados

- Defensa de los chips neuromórficos para la informática de IA

- Debut de chips de inteligencia artificial neuromórfica para aumentar las redes neuronales

- Los científicos de IBM inventan un termómetro para nanoescala

- IBM 5 en 5:los laboratorios médicos "en un chip" servirán como detectives de salud para rastrear enfermedades a nanoescala

- Los investigadores de IBM se llevan el premio a la innovación en investigación de semiconductores

- IBM presenta una arquitectura de cadena de bloques híbrida para Internet de las cosas

- Más allá de AIOps:Observabilidad para operaciones de TI efectivas

- Los siete requisitos para el mecanizado optimizado