Cómo las radios definidas por software manejan la sintonización de frecuencia ultra ancha

Una radio definida por software (SDR) utiliza un procesador de computadora de propósito general para realizar aspectos del procesamiento de señales digitales en lugar del hardware de circuito analógico. Esto permite una mayor flexibilidad en la aplicación, la capacidad de procesamiento y el rango dinámico a menudo a un costo menor en relación con los circuitos dedicados. En comparación con una radio completamente analógica, un SDR reemplaza algunos circuitos analógicos con implementaciones de software equivalentes, aunque se requerirán algunos componentes analógicos.

El ejemplo principal de componentes analógicos necesarios para cualquier SDR es el circuito amplificador de transmisión o recepción que interactúa con la antena de radiofrecuencia. Una parte importante de cualquier sistema de radio es un mezclador cuyo propósito es cambiar la frecuencia de una señal, ya sea hacia arriba o hacia abajo en frecuencia, un proceso conocido como heterodino. Los SDR usan mezcladores digitales que representan señales usando números complejos, lo que les permite una ventaja significativa sobre sus equivalentes analógicos:pueden realizar cambios de frecuencia de una señal a CC, mientras que un mezclador analógico solo puede cambiar una señal a una frecuencia más baja.

Por lo general, los SDR tienen anchos de banda más altos alrededor de su frecuencia central, lo que permite monitorear una porción más grande del espectro de radio y sintonizar en un rango más amplio sin necesidad de volver a sintonizar. Dicho de otra manera, esto significa que los SDR a menudo son capaces de ofrecer altos anchos de banda instantáneos en un amplio rango de sintonización que va desde CC hasta más de 18 GHz. Debido a la combinación de estos dos atributos de radio de alto rendimiento, la radio y el hardware de procesamiento de señales necesarios para admitir la sintonización de frecuencia pueden variar.

Es importante tener en cuenta que, según el diseño y el rango de frecuencia, la mezcla y la sintonización de frecuencias se pueden implementar en cualquier punto de la cadena de señal, incluso en digital o analógica. Este artículo analiza los mecanismos específicos disponibles para sintonizar varias frecuencias, incluido el muestreo directo, la mezcla en cuadratura de fase (IQ) y la mezcla superheterodina.

¿Qué es la mecánica de frecuencia?

Este documento utiliza el término mecánica de frecuencia para referirse al proceso por el cual una señal de alta frecuencia se desplaza hacia abajo en frecuencia a un rango apropiado para el muestreo por un convertidor de analógico a digital (ADC), así como las posteriores traducciones de frecuencia que pueden ocurren una vez que la señal es digitalizada. Se debe seleccionar una ruta de radio específica en función de la frecuencia de la señal; se optimizan diferentes rutas de radio para diferentes rangos de frecuencia. Dentro de cada cadena de radio, la frecuencia puede ser mezclada por convertidores analógicos, cambiando efectivamente la frecuencia hacia arriba o hacia abajo.

De manera similar, una señal digital también se puede desplazar, ya sea dentro del convertidor o dentro de la FPGA. Dependiendo del rango de frecuencia seleccionado, se utilizan diferentes métodos de muestreo y conversión. En resumen, este artículo analiza la mecánica de sintonización específica, junto con la mecánica de frecuencia relevante para cada modo de operación.

Método Componentes de ajuste analógico Ubicación de ajuste de frecuencia Muestreo directo Ninguno Software IQ Mezclador Hardware seguido de software Convertidor descendente de IF superheterodino, posiblemente segundo mezclador HardwareMuestreo directo

El muestreo directo se refiere al muestreo (o envío) de señales directamente desde la antena con un mínimo o ningún componente analógico en el medio. En otras palabras, una parte de la señal de radiofrecuencia (RF) se muestrea, se digitaliza y se pasa al software para su procesamiento. Aunque simple, las limitaciones de este método incluyen el ruido y la disponibilidad de relojes y hardware de muestreo de alta velocidad. Dado que se muestrea una gran extensión del espectro de RF, las aplicaciones multibanda son posibles sin tener que volver a sintonizar.

La capacidad de sintonizar diferentes frecuencias depende de la frecuencia de muestreo del ADC o del convertidor de digital a analógico (DAC) durante la transmisión. Los dispositivos convertidores disponibles comercialmente pueden muestrear hasta 3GSPS (giga muestras por segundo), lo que permite digitalizar una gran cantidad de datos en poco tiempo. Estas frecuencias de muestreo permiten muestrear datos en múltiples bandas de frecuencia, incluidas muchas bandas de frecuencia celular comerciales.

Los SDR a menudo funcionan como transceptores, dispositivos capaces tanto de transmitir como de recibir, y la cadena de muestreo directo es una entre varias cadenas posibles en los SDR de banda ancha. La cadena de muestreo directo se elige automáticamente cuando se utilizan frecuencias inferiores a las admitidas por el convertidor descendente analógico.

Transmisión de banda base

La antena externa está conectada al SDR a través de interruptores y amplificadores, sin embargo, tenga en cuenta que no se utilizan componentes analógicos para la conversión de frecuencia. Todo el remuestreo y la conversión de frecuencia se implementan en software y los circuitos analógicos se utilizan únicamente para el acondicionamiento de la señal, el filtrado y la amplificación.

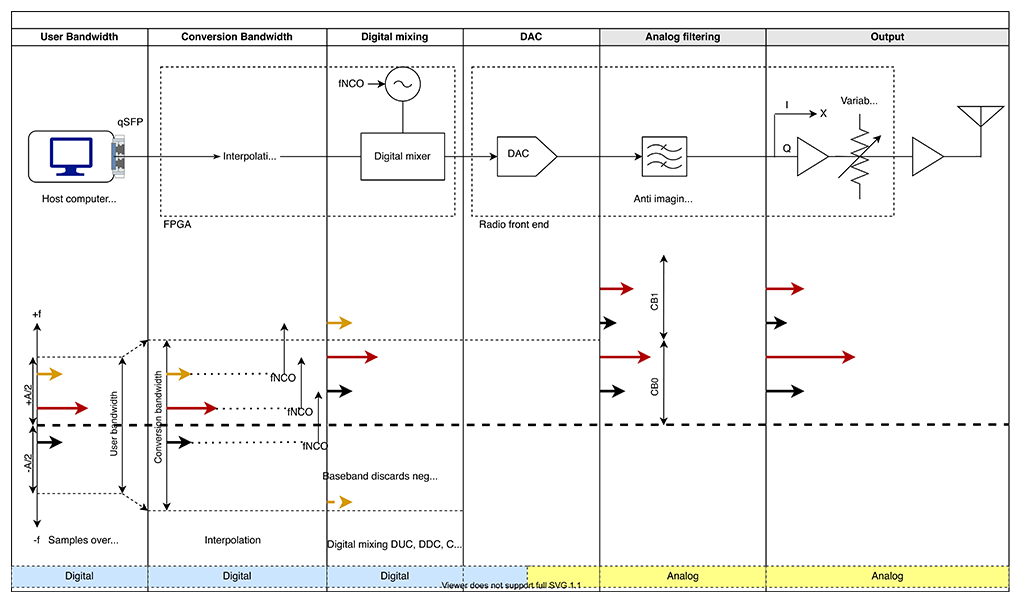

haga clic para ver la imagen a tamaño completo

Figura 1:El muestreo directo se refiere a la transmisión de señales directamente desde la antena con componentes analógicos mínimos o nulos en el medio. Fuente:Per Vices

Cuando el SDR funciona como transmisor, la aplicación del usuario genera los datos y la FPGA los recibe como muestras. Los puertos qSFP + envían los datos digitalizados a través de un enlace en serie a la FPGA, donde se produce el remuestreo y la mezcla de frecuencias en el dominio digital. Luego pasa por la rutina de interpolación basada en FPGA seguida de una conversión ascendente digital basada en FPGA, utilizando el oscilador de control numérico (NCO). Cualquier cambio de frecuencia aplicado por el usuario ocurre después de la interpolación, antes de enviar los datos al DAC, como se muestra en la Figura 1. Los datos digitales con desplazamiento de frecuencia son luego convertidos por el DAC en una señal analógica, que genera frecuencias de imagen como parte del proceso de conversión. . La señal ahora analógica pasa a través de filtros anti-imagen, a través de los amplificadores frontales de radio y luego a la antena de radio.

Mecánica de transmisión de banda base

A medida que las muestras se mueven a través de los distintos componentes del SDR, cambian las frecuencias y los anchos de banda. Ahora que tenemos una buena comprensión de nuestros circuitos, veamos qué sucede con la señal en cada uno de estos pasos.

Generando muestras

La mitad inferior de la Figura 1 muestra tres formas de onda que podríamos estar buscando transmitir. Antes de que se generen las muestras, el usuario define una frecuencia de muestreo (etiquetada A). La frecuencia de muestreo sirve para especificar el ancho de banda del usuario; un intervalo [-A / 2, A / 2] que se centra alrededor de 0 Hz. Dado que estas formas de onda serán compensadas por la frecuencia NCO en una etapa posterior, las ondas sinusoidales iniciales en algunos casos pueden tener una frecuencia negativa, como la señal negra en el diagrama. Una vez generadas, las muestras se enviarán al SDR a través de un enlace en serie para su posterior procesamiento. Es importante tener en cuenta que no se transmitirán todas las muestras en el ancho de banda del usuario; se aclarará más adelante (consulte la señal amarilla en el diagrama anterior).

Interpolación

Después de generar muestras de usuario, el siguiente paso es realizar una interpolación para obtener un ancho de banda mayor. Este nuevo ancho de banda especifica un intervalo más grande, también centrado alrededor de 0 Hz, que se define por la frecuencia de muestreo del dispositivo (325 MSPS para Crimson TNG, 1 GSPS para Cyan). El ancho de banda del usuario es siempre menor que el ancho de banda de conversión. Interpolar las muestras a un ancho de banda mayor es crucial para la siguiente etapa en la que tiene lugar la conversión ascendente digital.

Conversión ascendente

Después de interpolar la señal al ancho de banda de conversión del dispositivo, la FPGA puede proceder a convertir las muestras. Recuerde que la conversión ascendente simplemente desplaza todas las frecuencias hacia arriba en una cantidad fija:la frecuencia del suboficial. Tanto Crimson TNG como Cyan tienen mezcladores digitales CORDIC que son capaces tanto de conversión ascendente como descendente (DUC, DDC). La conversión ascendente se logra mezclando las muestras del usuario con un oscilador local que se encuentra en el FPGA (establecido en la frecuencia NCO). Esto hace que aumente la frecuencia de todas nuestras señales. El uso del ancho de banda de conversión más grande que obtuvimos de la interpolación garantiza que podamos capturar más de nuestros productos de mezcla.

En algunos casos (ver la señal en amarillo), mezclar nuestra señal generada con la frecuencia NCO da como resultado una frecuencia que no se encuentra dentro del ancho de banda del usuario. Aquí, el producto de mezcla todavía tendrá una imagen que se rotará para ajustarse a nuestro ancho de banda de captura (vea la línea de puntos en amarillo). Para las señales de banda base, los componentes de frecuencia negativa se descartan y, por lo tanto, esta imagen no es relevante y se ignora.

Luego, el DAC convierte las señales a su forma analógica. A pesar de lo bien que funcionan los DAC de hoy en día, existirán imágenes de Nyquist de las señales originales; en cada múltiplo de nuestro ancho de banda de conversión, es probable que veamos imágenes de la señal en sus compensaciones correspondientes. Los filtros anti-imagen se utilizan para suprimir las imágenes que normalmente aparecerían en zonas de Nyquist más altas, múltiplos del ancho de banda de conversión. La señal analógica final ahora se puede transmitir a través de la antena.

Direct IQ

Direct IQ o muestreo en cuadratura en fase es una variante del muestreo directo donde una señal de RF recibida se divide en dos componentes, separados por 90 grados en fase. Se utilizan dos canales ADC, o canales DAC para transmisión, para muestrear estas señales de fase desplazada. El proceso para la recepción directa de IQ se describe a continuación.

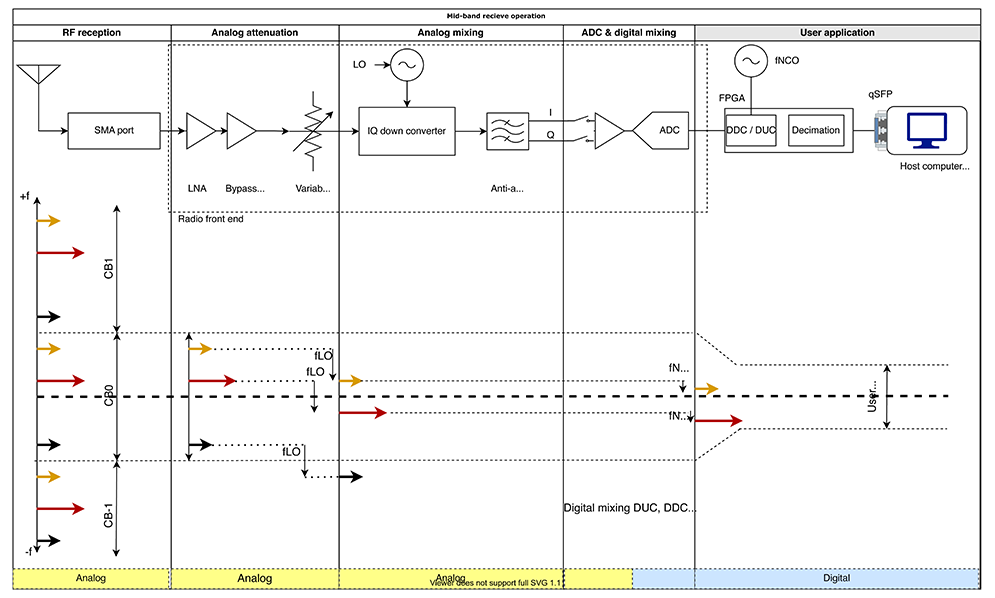

haga clic para ver la imagen a tamaño completo

Figura 2:El receptor Direct IQ, una variante del muestreo directo, emplea dos canales para muestrear señales con desfase. Fuente:Per Vices

La primera sección en el lado izquierdo de la Figura 2 muestra tres ondas sinusoidales puras y sus imágenes cuando son captadas por la antena. Un atenuador variable atenúa las frecuencias fuera de la banda de interés. La siguiente etapa, el modulador IQ, combina los componentes I y Q para formar la señal de RF. Este proceso desplaza todas las frecuencias hacia abajo en una cantidad determinada por el oscilador local (LO). Tenga en cuenta que este es un proceso analógico.

Un filtro anti-aliasing analógico tiene como objetivo restringir la señal entrante solo a aquellas que caen en el dominio del convertidor. Esto es importante porque el ADC tiene un rango operativo finito de frecuencia que está limitado por su frecuencia de muestreo. El ancho de banda del convertidor especifica un intervalo grande centrado alrededor de 0 Hz que se define por la frecuencia de muestreo del dispositivo (325 MSPS para Crimson TNG, 1 GSPS para Cyan). El ADC convierte las señales entrantes en una forma digital.

En este punto, el ancho de banda convertido es grande para el procesamiento digital. Para prepararse para la destrucción, las muestras se reducen digitalmente. Esto disminuye la frecuencia de todas las señales por la frecuencia NCO establecida en la FPGA. Crimson TNG y Cyan tienen mezcladores digitales CORDIC capaces tanto de DUC como de DDC. La conversión descendente se logra mezclando las muestras recibidas con un oscilador local que se encuentra en el FPGA, establecido en lo que se conoce como la frecuencia NCO. Tenga en cuenta que después de que esto suceda, algunas de las frecuencias, como la que se muestra en rojo, pueden ser negativas.

Antes de recibir las muestras, el usuario define una frecuencia de muestreo (etiquetada como B). La frecuencia de muestreo, a su vez, especifica el ancho de banda del usuario, un intervalo [-B / 2, B / 2] que se centra alrededor de 0 Hz. La diezma asegura que todas las señales entrantes caigan dentro del ancho de banda del usuario.

Súper heterodino

Un receptor heterodino mezcla la señal de RF recibida (f1) con una señal de referencia de un oscilador local (f2) para producir dos señales a frecuencias intermedias de (f1 ± f2). Se elige una frecuencia intermedia (IF) del receptor superheterodino, abreviado a super-het, de modo que sea más fácil de procesar con electrónica analógica y, en consecuencia, esté por encima de las frecuencias normales audibles por humanos (de ahí el prefijo de "super").

Receptor superhet

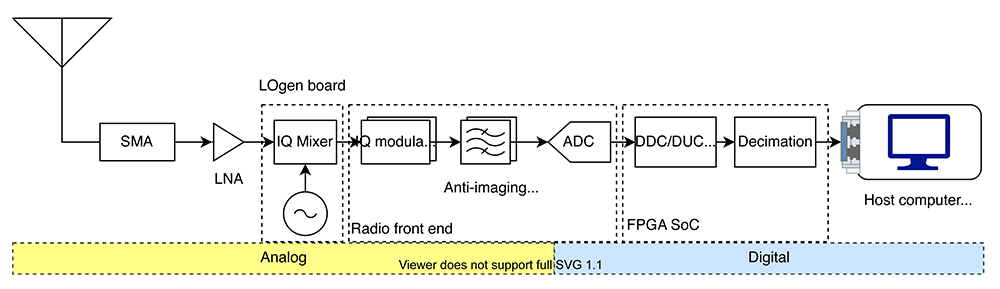

En la Figura 3 se muestra un receptor superhet. Tenga en cuenta que solo se muestra un receptor para simplificar; el circuito de transmisión equivalente utilizará componentes similares con el flujo de señal invertido. Las etapas analógicas asociadas se eligen automáticamente cuando el usuario selecciona una frecuencia de trabajo en el rango superhet. Un receptor superhet primero convierte la RF recibida usando un mezclador analógico. Esto se logra mediante un circuito separado adecuado etiquetado como “placa LOgen” en la Figura 3. El uso de una mezcla analógica de alta frecuencia de esta manera produce lo que se conoce como frecuencias de batido o múltiplos de IF. Se requieren filtros analógicos antes de la digitalización.

haga clic para ver la imagen a tamaño completo

Figura 3:El IF del receptor superheterodino se elige de modo que sea más fácil de procesar con electrónica analógica. Fuente:Per Vices

Se implementa una segunda etapa de conversión descendente utilizando el modulador IQ seguido de filtros anti-imagen para eliminar los productos de conversión generados por el proceso de mezcla de alta frecuencia. El IF ahora está digitalizado y se puede mezclar aún más utilizando mezcladores digitales antes de la diezma y el uso final en software.

Comprensión de las compensaciones

Dependiendo de la frecuencia de trabajo, un SDR de banda ancha selecciona entre los circuitos analógicos disponibles. Cuando se trabaja con frecuencias de banda base o muestreo directo, no es posible la mezcla analógica y la frecuencia está limitada por la velocidad del reloj del circuito. Cuando se trabaja con frecuencias más altas, se requieren circuitos mezcladores analógicos, y el número de etapas de mezcla analógica nuevamente depende de la frecuencia. Trabajar en el rango de GHz normalmente requiere un circuito analógico super-het y normalmente dos circuitos de mezcla analógicos para reducir la frecuencia de la señal al rango de trabajo de los componentes digitales, como ADC o DAC.

El uso de un solo dispositivo para la sintonización de banda ancha requiere una comprensión de las ventajas y desventajas de varios métodos. Los ejemplos incluyen artefactos de señal causados por la mezcla analógica o el costo de los dispositivos de conversión de alta velocidad si no se desea la mezcla analógica. Es importante trabajar con proveedores que tengan experiencia en desarrollo para operaciones de banda ancha y que tengan la capacidad de modificar sus productos para cumplir con los requisitos específicos asociados con un proyecto determinado. Es mejor seleccionar un proveedor en función de sus productos disponibles, especificaciones, aplicaciones compatibles y una discusión sobre sus capacidades.

>> Este artículo se publicó originalmente en nuestro sitio hermano, EDN .

Victor Wollesen es director ejecutivo de Per Vices Corporation.

Victor Wollesen es director ejecutivo de Per Vices Corporation.  Eldrich Rebello es ingeniero eléctrico en el Instituto de Energía Eólica de Canadá.

Eldrich Rebello es ingeniero eléctrico en el Instituto de Energía Eólica de Canadá. Contenidos relacionados:

- Navegación por satélite y radio definida por software

- Automóviles definidos por software:una plataforma eficiente para la paralelización esencial

- Seguridad de IoT:perímetro definido por software y blockchain

- El proyecto SDN de código abierto obtiene el código de Google

- Por qué los DSP están repentinamente en todas partes

Para obtener más información sobre Embedded, suscríbase al boletín informativo semanal por correo electrónico de Embedded.

Incrustado

- Radio

- Cómo garantizar el mejor rendimiento de la máquina de estado Qt

- Cómo la computación analógica en memoria puede resolver los desafíos de potencia de la inferencia de IA de borde

- Cómo hacer que los procesadores sean confiables

- Cómo el seguimiento de movimiento permite la comodidad del usuario

- ¿Qué tan bajo (potencia) puedes llegar?

- Velocidades del chip del procesador en memoria Cálculos de IA

- Los SoC habilitados para AI manejan múltiples transmisiones de video

- ¿Estás contratando ahora? Cómo manejar una afluencia de solicitantes

- ¿Cómo manejar las no conformidades en las líneas de producción?

- Cómo arreglar la manija de la puerta de tu auto