Distribución y sincronización de reinicio asíncrono - ASIC y FPGA

La falta de coordinación entre los reinicios asíncronos y los relojes lógicos síncronos conduce a fallas intermitentes en el encendido. En esta serie de artículos, discutimos los requisitos y desafíos del reinicio asincrónico y exploramos soluciones avanzadas para diseños ASIC vs FPGA.

Los restablecimientos asíncronos se emplean tradicionalmente en los diseños de VLSI para llevar los circuitos síncronos a un estado conocido después del encendido. La operación de liberación de reinicio asíncrono debe coordinarse con la señal de reloj lógico síncrono para eliminar fallas de sincronización debido a una posible contención entre el reinicio y el reloj. La falta de tal coordinación conduce a fallas intermitentes en el encendido. El problema se agrava cuando se consideran diseños grandes de dominios de reloj múltiple. Además de los problemas de sincronización, la distribución de un reinicio asincrónico a millones de flip-flops es un desafío, ya que requiere técnicas similares a CTS (Clock Tree Synthesis) y requiere un área y recursos de enrutamiento similares.

Se revisan los requisitos y desafíos del restablecimiento asincrónico, centrándose en los problemas de sincronización y distribución. Se discuten los inconvenientes de las soluciones clásicas para restablecer la sincronización (restablecer la sincronización de la fuente del árbol) y la distribución (restablecer la síntesis del árbol). Se presentan soluciones avanzadas para una convergencia de temporización más rápida y sencilla y una distribución y sincronización de reinicio más fiables. Se detallan diferentes enfoques para diseños ASIC versus FPGA.

La Parte 1 describe los problemas relacionados con los restablecimientos asincrónicos y describe los enfoques para resolverlos. La parte 2 (este artículo) analiza soluciones adicionales para el reinicio asíncrono correcto en ASIC y FPGA. En la Parte 3 se analizan algunos casos especiales útiles.

2. Técnicas de convergencia de tiempos de reinicio asincrónico

Uno de los principales problemas discutidos en la Parte 1 fue la complejidad de la liberación de reinicio para diseños grandes (con una red de distribución de reinicio de alta latencia), especialmente cuando se emplea un ciclo de reloj corto. La convergencia de tiempos basada en la optimización estándar de STA conduce a un diseño costoso y en algunos casos es incluso imposible. Aquí discutimos dos técnicas que mitigan este problema de tiempo. Ambas técnicas son aplicables para diseños ASIC y FPGA.

2.1. Canalización de restablecimiento asincrónico

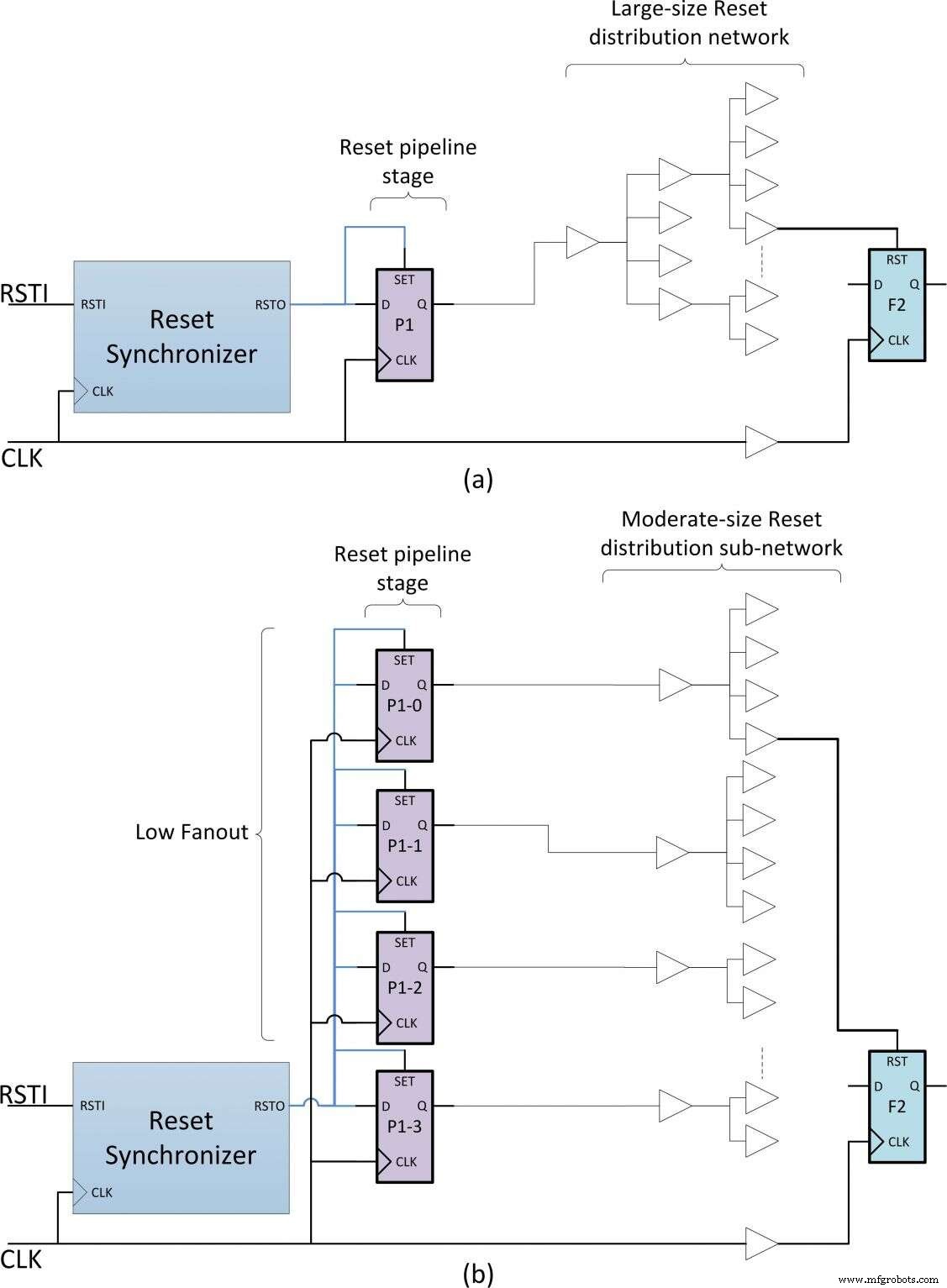

Una forma de lidiar con el problema de la sincronización de la liberación de reinicio asincrónica es intercambiar la latencia de liberación de reinicio por una sincronización más relajada. Esto se puede lograr canalizando el árbol de reinicio de la siguiente manera. Después de cada sincronizador, se incluye una etapa de flip-flop P1 de configuración asíncrona adicional en la línea de reinicio (Figura 6a). Ambas entradas SET y D del flip-flop están conectadas al RSTO de reinicio alto activo proveniente del sincronizador de reinicio. En la versión RSTO, las condiciones de configuración y retención se cumplen para las entradas P1 D y SET, ya que están restringidas como rutas sincrónicas regulares.

haz clic para ampliar la imagen

Figura 6:Restablecimiento asincrónico con canalización (Fuente:vSync Circuits)

El funcionamiento funcional del nuevo esquema es similar al normal descrito en la Parte 1 (Figura 3d), excepto por una latencia de ciclo único adicional en la versión de reinicio. La latencia de restablecimiento más alta incurrida por esta técnica suele ser aceptable para la mayoría de las aplicaciones, ya que solo se produce una vez por encendido.

Una parte complementaria de esta técnica cubre las limitaciones de diseño. Si bien los flip-flops del sincronizador deben restringirse contra la duplicación para evitar problemas de ruta de convergencia como se describe en la Parte 1, la etapa P1 de la tubería está sujeta a la restricción MAX_FANOUT. En la Figura 6b se muestra un ejemplo de restricción de abanico máximo. El flip-flop P1 es automáticamente duplicado por la herramienta de síntesis, creando cuatro subredes para la distribución de reinicio. Cada subred tiene una latencia más baja que la red original, cumpliendo con el requisito de tiempo para la liberación de reinicio. Además, la salida del sincronizador de reinicio se encuentra fácilmente con un abanico de ocho.

Esta técnica de canalización de reinicio asincrónico es escalable para cualquier tamaño de diseño y no requiere cambios cuando el diseño está cambiando, ya que la herramienta de síntesis duplica automáticamente la etapa P1, manteniendo acotada la subred de reinicio de latencia moderada. El fanout de la etapa P1 duplicado para la salida del sincronizador suele ser pequeño y no causa violaciones de tiempo. Sin embargo, cuando una sola etapa de canalización no conduce a la convergencia de tiempos, las etapas de canalización adicionales P2 - PN pueden incluirse y restringirse con diferentes restricciones MAX_FANOUT.

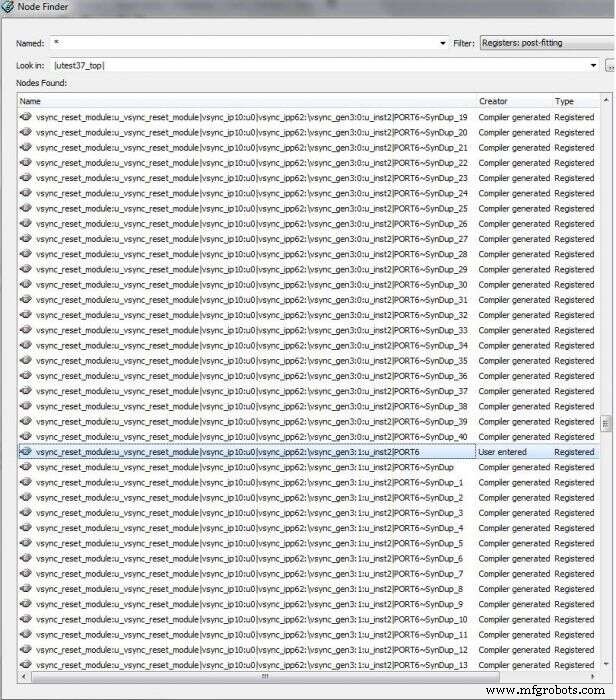

Un ejemplo de esta técnica aplicada a un diseño real se muestra en la Figura 7. El registro de etapa P1, llamado PORT6, fue automáticamente duplicado unas 40 veces por la herramienta de síntesis [6] para cumplir con la restricción MAX_FANOUT. Cada una de las 40 subredes cumplió con el tiempo para su distribución local.

haz clic para ampliar la imagen

Figura 7:Ejemplo de canalización de reinicio asíncrono (Fuente:vSync Circuits)

Incrustado

- Estructuras y clases en C ++

- Buzones de correo:introducción y servicios básicos

- Semáforos:introducción y servicios básicos

- Anvo-Systems y Mouser firman un acuerdo de distribución

- Mouser e Inventek Systems anuncian un acuerdo de distribución global

- Rutronik y AP Memory firman un acuerdo de distribución global

- Empresas de composición y distribución separada de plásticos de Albis

- El arte y la ciencia de la selección del sitio de distribución

- Seis formas de reducir las emisiones en el almacenamiento y la distribución

- RG Group acuerda una asociación de distribución e integración con AutoGuide Mobile Robots

- 20 blogs de fabricación que todo profesional de fabricación, cadena de suministro, distribución y logística debería leer