CPU más flujo de diseño FPGA para desarrolladores de software:una nueva realidad tangible

Recientemente, Brian Bailey organizó una mesa redonda que resultó en un artículo de dos partes llamado Soporte de CPU más FPGA . Los expertos discutieron la realidad cambiante del diseño de sistemas basados en FPGA y CPU. Esta discusión aborda los desarrollos recientes en el flujo de diseño y cómo el uso de nueva tecnología puede ayudar a los desarrolladores de software a alcanzar un tiempo de comercialización más rápido para las plataformas CPU más FPGA.

Introducción

Al observar el creciente interés en la inteligencia artificial (IA), la aparición de objetos conectados (IoT) y la tendencia de aceleración del centro de datos, todos nos llevan a preguntarnos:¿cuál es el denominador común entre los tres?

Los desarrolladores de software están en el centro de todas estas tendencias y buscan acelerar su programación y cálculos. Los últimos avances tecnológicos, incluida la baja latencia de comunicación entre FPGA y CPU, junto con el consumo de energía relativamente bajo de los FPGA actuales, hacen que los sistemas basados en FPGA y CPU sean la elección correcta para lograr el rendimiento deseado. Sin embargo, en el centro de esta convergencia, los desarrolladores de software se ven obstaculizados por la complejidad subyacente de la tecnología FPGA.

En los últimos años, las herramientas de síntesis de alto nivel (HLS) han mejorado enormemente con respecto a abordar la complejidad del sistema actual y acortar el tiempo de comercialización. Sin embargo, las herramientas de HLS se centran principalmente en bloques de IP (es decir, están centradas en IP). Existe una amplia gama de decisiones / optimizaciones a nivel del sistema que no pueden ser compatibles con las herramientas HLS para satisfacer los requisitos. Algunos de estos requisitos incluyen encontrar el equilibrio adecuado entre las tareas de software y los aceleradores de hardware, comparar la ejecución en paralelo con la ejecución en paralelo, lograr la granularidad de datos deseada, evaluar los mecanismos de comunicación y muchos más.

Para construir estos sistemas complejos, los desarrolladores de software requieren un flujo de diseño que ofrezca soporte conjunto tanto de hardware como de software. Dicho flujo debe ser lo suficientemente simple como para garantizar su uso (como el flujo del desarrollador de software) y la adopción por parte de los desarrolladores de software. El flujo también debe proporcionar comentarios profundos sobre las opciones de optimización disponibles para lograr los objetivos de rendimiento requeridos. Algunas empresas han allanado recientemente el camino para facilitar la tarea a los desarrolladores de software al abstraer los detalles tecnológicos del flujo de diseño de hardware. Estas empresas se inspiran en los enfoques de diseño a nivel de sistema descritos en Modelos de ESL y su aplicación:diseño y verificación a nivel de sistema electrónico en la práctica .

Comprensión de la metodología de flujo de diseño a nivel del sistema

El diseño a nivel de sistema se centra en preocupaciones de nivel de abstracción superior. Si bien existe la necesidad de concentrarse en el panorama general, se utilizan varios niveles de abstracciones para validar, verificar, refinar e integrar diferentes partes del sistema antes de que realmente se desarrolle. Aunque la comunidad de ingenieros no está de acuerdo sobre un lenguaje común para usar, la mayoría de los ingenieros de diseño comienzan en el nivel algorítmico. Los diseñadores validan especificaciones de sistemas funcionales y no funcionales mediante la creación de modelos de ejecución escritos en entornos C / C ++ / SystemC, MATLAB, Simulink y LabVIEW. Estos lenguajes de alto nivel se utilizan para modelar el comportamiento de todo el sistema.

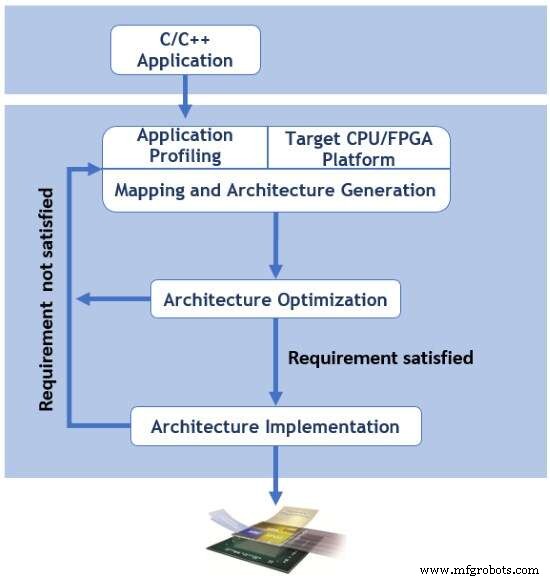

Para los propósitos de esta discusión, nos hemos centrado en un flujo de diseño a nivel de sistema basado en especificaciones C / C ++ (Figura 1). El primer bloque se divide en tres pasos. El primero de estos pasos representa el perfil de la aplicación (es decir, la partición de hardware-software) donde se considera que partes de código C / C ++ (funciones, bucles, etc.) se mueven al hardware (FPGA). El siguiente paso es la especificación de la plataforma CPU / FPGA (por ejemplo, ARM53 / FPGA, POWER8 / FPGA) y la configuración de los elementos de la plataforma de hardware (reloj del sistema, caché del procesador, interconexiones, etc.). El siguiente paso es mapear las tareas de la aplicación (según la aplicación perfilada) entre el hardware y el software (es decir, CPU dura y / o blanda) y, al final, la generación de una arquitectura ejecutable.

Figura 1. Flujo típico de diseño a nivel de sistema para CPU / FPGA

(Fuente:Space Codesign Systems, Inc.)

El segundo bloque de la Figura 1 implica la optimización de la arquitectura (también conocida como exploración arquitectónica o verificación del rendimiento). Esto se describe con más detalle en la Figura 2.

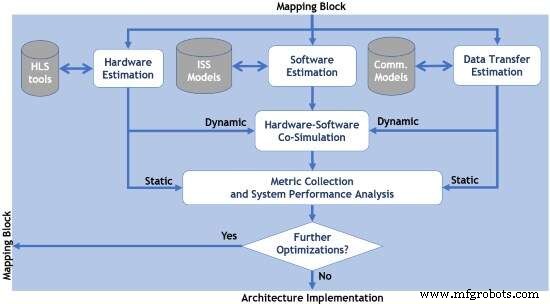

Figura 2. El proceso de optimización de la arquitectura

(Fuente:Space Codesign Systems, Inc.)

El proceso de optimización de la arquitectura aborda los siguientes estimadores:

- Estimación de hardware evalúa métricas de partición de hardware (es decir, código C / C ++ movido en la FPGA). Puede desglosarse por recursos, rendimiento (p. Ej., Latencia de bucle) y estimaciones de potencia. La estimación de hardware está impulsada por herramientas HLS (síntesis de alto nivel).

- Estimación de software evalúa métricas para el código de partición C / C ++ que se ejecuta en la CPU (es decir, CPU dura y / o blanda). Este proceso es complementario al paso de estimación de hardware. Ejemplos de métricas de rendimiento son la carga del procesador, la conmutación de tareas y las fallas de caché.

- Estimación de la transferencia de datos consiste en modelar las interfaces (es decir, interfaces mapeadas en memoria y de transmisión) mediante las cuales se comunican el hardware y el software. Algunos ejemplos de métricas recopiladas son el rendimiento del bus (p. Ej., Latencia y rendimiento), la cola y el uso de la memoria.

Estas estimaciones se agregan en una base de datos y se presenta al desarrollador un análisis de rendimiento del sistema para evaluar si se cumplen los requisitos del sistema. Las arquitecturas que satisfacen los requisitos proceden al proceso de implementación de la arquitectura; de lo contrario, se procesan intentos adicionales de optimización a nivel del sistema.

El último bloque de la Figura 1 se relaciona con la implementación de la arquitectura donde las arquitecturas del sistema se convierten a un flujo de bits (para la implementación de FPGA) utilizando herramientas de implementación como Xilinx Vivado o Intel Quartus Prime para la generación final y completa del sistema que se ejecutará en la plataforma física específica. Este paso debe producir un código de calidad y debe ser transparente para el desarrollador de software.

Optimización a nivel del sistema

La falta de herramientas automatizadas para la optimización de la arquitectura se ha percibido durante mucho tiempo como una debilidad clave de la computación basada en FPGA. El desarrollo de tales herramientas fue difícil debido a la complejidad y los desafíos involucrados.

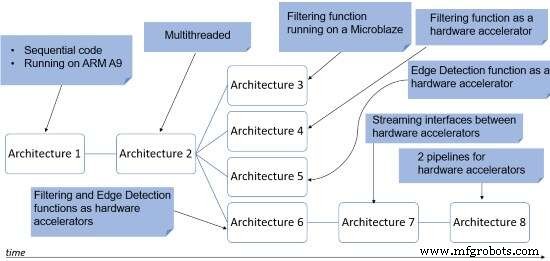

Para ilustrar estos desafíos, la Figura 3 muestra un proceso típico de optimización a nivel de sistema durante una exploración arquitectónica para una aplicación de procesamiento de imágenes compuesta por seis funciones (piezas de código C / C ++) que se implementarán en una plataforma Zynq-7000. Aquí, enumeramos ocho arquitecturas potenciales que se pueden implementar en la plataforma. Dado que el tiempo de comercialización no permite la implementación de cada arquitectura, se debe determinar rápidamente cuál es la mejor para implementar. Esta secuencia de optimizaciones puede ser un desafío, incluso para diseñadores de hardware experimentados.

Figura 3. Exploración de la arquitectura con decisiones a nivel de sistema mostradas en azul

(Fuente:Space Codesign Systems, Inc.)

Las herramientas de desarrollo de software FPGA como SDSoC / SDAccel (Xilinx), Merlin Compiler (Falcon Computing Solutions) y SpaceStudio (Space Codesign Systems) son soluciones comerciales que ayudan a los desarrolladores de software en el diseño de sistemas FPGA / CPU mientras logran la optimización a nivel del sistema. Estas herramientas adoptan un flujo similar al descrito en las Figuras 1 y 2 y, por eso, demuestran la existencia de una nueva generación de herramientas a nivel de sistema con diferentes enfoques.

SDSoC estima el rendimiento del sistema en un enfoque de dos pasos. Inicialmente, SDSoC estima las latencias para las funciones de hardware (de las herramientas HLS) y la caracterización interna (es decir, transferencia de datos) de la plataforma física objetivo y sus interfaces de comunicación. Posteriormente, esta estimación se compara con una versión de software de la aplicación que se ejecuta en la plataforma física.

Merlin Compiler propone la transformación de fuente a fuente. El objetivo de la transformación de fuente a fuente es reducir o eliminar la brecha de abstracción del diseño entre el desarrollo de software / algoritmos y los flujos de diseño de HLS existentes. Merlin Compiler se basa en cuatro pragmas para inferir diseños FPGA específicos. Además de las cuatro optimizaciones principales desencadenadas por pragmas explícitos, Merlin Compiler también contiene varias optimizaciones implícitas (es decir, pasadas de transformación del compilador) que se realizan junto con los pragmas para ayudar a mejorar los resultados de la canalización y la paralelización.

SpaceStudio genera sin problemas una plataforma virtual ejecutable (VP) para cada candidato de arquitectura (mapeo). Un VP típico se compone de simuladores de núcleo de procesador conectados a varios modelos de buses, controladores de memoria y otros modelos de periféricos de datos. Modela la plataforma de destino junto con las transferencias de datos en un entorno co-simulado que se adapta específicamente a la aplicación. Esto significa que el VP ejecutable permite una predicción de rendimiento más precisa y una validación del algoritmo de la aplicación. También integra capacidades de monitoreo y análisis para la generación de perfiles de desempeño no intrusivos tanto de funciones de hardware como de tareas de software. VP se basa en herramientas HLS para estimadores de hardware, mientras que los retrasos (p. Ej., Latencias) de las funciones asignadas por hardware se anotan automáticamente para aumentar la precisión del proceso de simulación. El desarrollador de software puede inspeccionar al vicepresidente para comprender cómo se implementan las tareas de optimización. Estos comentarios ayudan al desarrollador de software a lograr el diseño previsto para las optimizaciones aplicadas específicas.

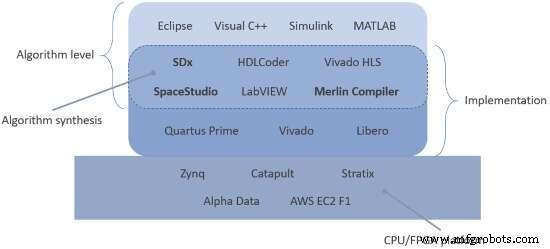

Una forma de ver el ecosistema comercial

La Figura 4 propone una vista del ecosistema comercial que gravita alrededor del mundo del diseño basado en plataformas de CPU y FPGA. El primer cuadro (superior) presenta la entrada de diseño principal a nivel de algoritmo. El segundo cuadro contiene entornos que admiten la síntesis algorítmica (es decir, desde el algoritmo hasta la implementación). Las herramientas marcadas en negrita admiten la entrada de diseño C / C ++ y realizan optimizaciones a nivel del sistema. El tercer recuadro representa las herramientas utilizadas para lograr la implementación de la arquitectura, principalmente herramientas de los proveedores de FPGA que realizan la síntesis de bajo nivel y la generación de flujo de bits. En la parte inferior de la figura, se ilustran ejemplos de plataformas CPU / FPGA.

Figura 4. Ecosistema comercial para plataformas CPU / FPGA

(Fuente:Space Codesign Systems, Inc.)

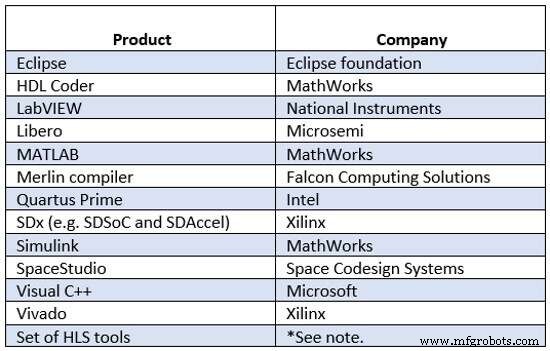

Además, la Tabla 1 enumera algunas de las principales herramientas comerciales utilizadas en el diseño de plataformas CPU / FPGA.

Tabla 1. Herramientas de automatización comercial (* Nota:se propone una lista en esta revisión)

Conclusión

El objetivo final es democratizar el desarrollo de CPU más plataformas FPGA para una población más amplia de usuarios, como la comunidad de desarrolladores de software. Al observar la analogía de los lenguajes de programación, la industria de las TI tardó más de 50 años en evolucionar hacia lenguajes amigables como Python o, más recientemente, Swift. Un proceso de evolución similar está ocurriendo en la industria de la programación FPGA. La aceptación de las herramientas HLS tomó algún tiempo para ser respaldada por los diseñadores de sistemas. Hoy, con la llegada de soluciones a nivel de sistema para desarrolladores de software, estamos entrando en una nueva fase. Herramientas comerciales como SpaceStudio, SDSoC y Merlin Compiler son testimonio de este proceso de aceptación. Aún así, queda mucho trabajo por hacer para tener un proceso totalmente automatizado y optimizado en todos los compiladores dirigidos a las plataformas CPU más FPGA.

Guy Bois, Ing., PhD es el fundador de Space Codesign Systems y profesor en el Departamento de Ingeniería de Software y Computación de la Polytechnique Montréal. Guy ha participado en muchos proyectos de I + D en colaboración con líderes de la industria como STMicroelectronics, Grass Valley, PMC Sierra, Design Workshops Technologies y Cadabra Systems. La experiencia en investigación de Guy en el campo del diseño de códigos de hardware / software llevó a la comercialización de la solución y al inicio de SpaceStudio de Space Codesign Systems Inc.

Incrustado

- Entrevista con expertos:AMendate sobre su software de optimización de topología automatizada para impresión 3D

- Entrevista con el experto:Ravi Kunju de Altair sobre el software de simulación para impresión 3D

- 5 preguntas para Stefan Ferber, nuevo director ejecutivo de Bosch Software Innovatons

- El proyecto explora un diseño confiable y un flujo de verificación para la seguridad de IoT

- La nueva herramienta basada en ML ofrece optimización automatizada del flujo de diseño de chips

- Acelerador FPGA para cámaras MIPI de visión integrada

- Cadence y UMC colaboran en la certificación del flujo de señal analógica / mixta para el proceso 28HPC +

- Automatización:nuevo hardware y software para robots de bajo costo

- Casos de uso geniales de IoT:nuevos mecanismos de seguridad para automóviles en red

- Omron lanza nuevo software para sus robots móviles

- Adaptación a una nueva realidad para la fabricación