Determinismo de la fase de encendido:uso de la sincronización multichip

La integración de múltiples bloques de procesamiento de señales digitales (DSP), convertidores de digital a analógico (DAC) de banda ancha y convertidores de analógico a digital (ADC) de banda ancha dentro de un solo chip monolítico ahora permite la descarga de recursos FPGA que consumen mucha energía para permiten plataformas de menor tamaño, menor consumo de energía y mayor cantidad de canales que pueden muestrear a velocidades más altas que las que se podían lograr anteriormente. Junto con esta nueva capacidad, vienen nuevos algoritmos de sincronización multichip (MCS) dentro de estos circuitos integrados (IC), que permiten a los usuarios lograr una fase conocida (determinista) para todos los canales al encender el sistema o realizar modificaciones de software en el sistema. Por lo tanto, esta fase determinista simplifica los algoritmos de calibración a nivel de sistema más amplios necesarios para lograr la sincronización de todos los canales en la salida o entrada a las redes frontales conectadas a estos circuitos integrados. Este artículo presenta resultados experimentales que demuestran esta capacidad MCS mientras se usa una plataforma de receptor / transmisor de 16 canales que consta de varios circuitos integrados digitalizadores, fuentes de reloj e interfaces digitales.

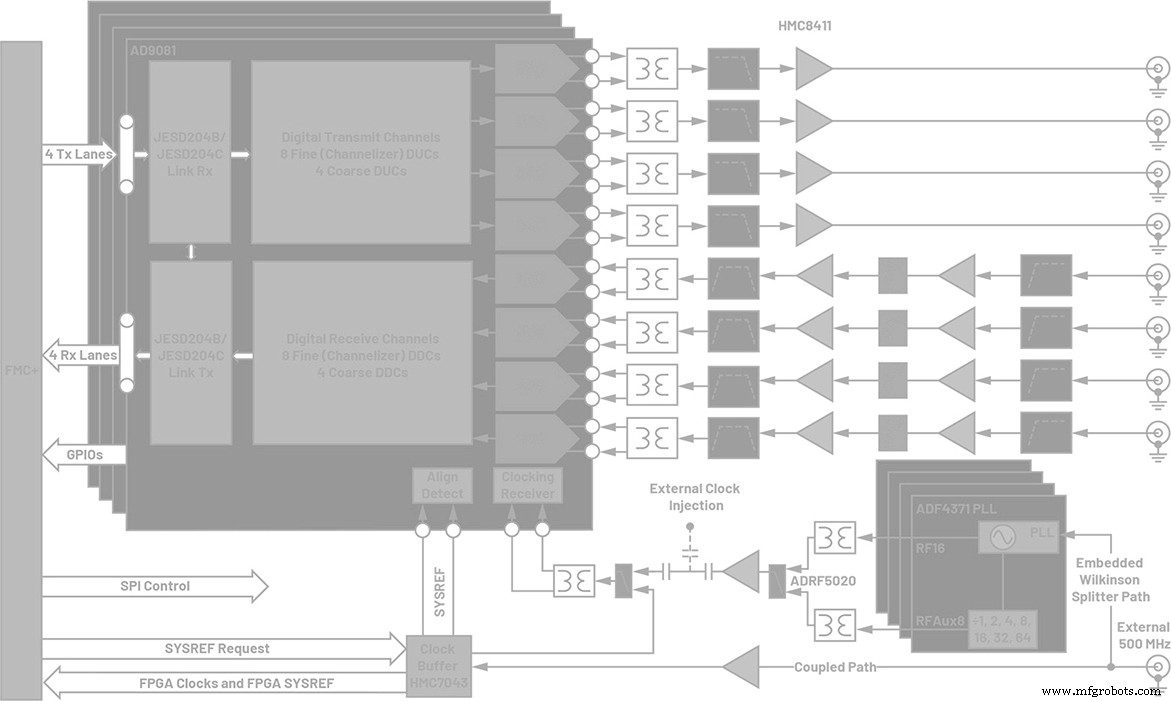

Diagrama de bloques del sistema de alto nivel

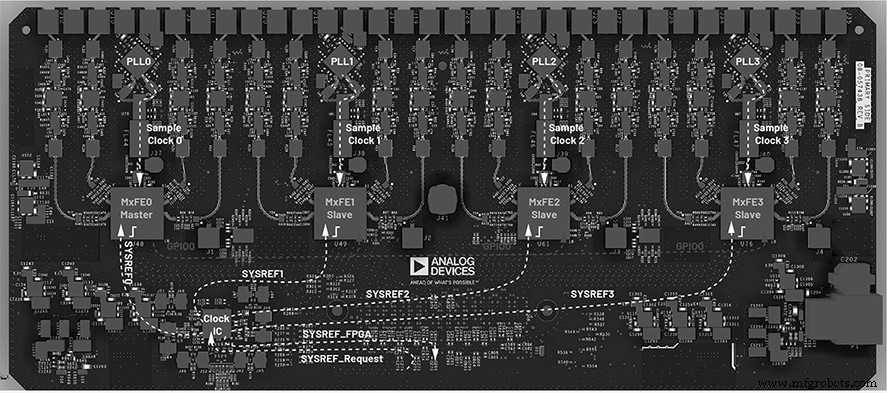

En la Figura 1 se muestra un diagrama de bloques del sistema utilizado para esta prueba y consta de cuatro circuitos integrados DAC / ADC / DSP integrados que constan cada uno de cuatro 12 GSPS DAC, cuatro 4 GSPS ADC y 12 convertidores digitales ascendentes (DUC) y 12 digitales. Bloques de convertidor descendente (DDC).

haz clic para ver la imagen en tamaño completo

Figura 1. Un diagrama de bloques de alto nivel del sistema utilizado para demostrar MCS y algoritmos de calibración multicanal. (Fuente:Analog Devices)

Los DUC / DDC permiten la traducción de frecuencia y / o la interpolación / diezmado dentro del dominio digital. Usando un solo reloj de referencia de 500 MHz inyectado en la placa, se utiliza un búfer de reloj bloqueado por referencia para generar las señales de referencia del sistema necesarias para MCS, así como los relojes requeridos para la interfaz digital al procesador de banda base (BBP). El sistema también contiene cuatro sintetizadores de bucle de bloqueo de fase (PLL) separados que generan las fuentes de 12 GHz necesarias para sincronizar cada circuito integrado digitalizador a partir de la referencia común. Se adjunta un extremo frontal de RF a cada salida / entrada del digitalizador, que crea una señal filtrada y amplificada hacia / desde los conectores de RF lanzados desde el borde. Se implementa una solución de distribución de energía completa. Todos los voltajes necesarios para el sistema se generan a partir de una única fuente de 12 V. Todas las señales de transmisión se propagan en la parte inferior de la placa, mientras que todas las señales de recepción se propagan en la parte superior de la placa para lograr el aislamiento de canal a canal más óptimo.

Estructura de árbol de reloj de subarreglo

Como se mencionó anteriormente, el árbol de reloj de subarreglos consta de una única fuente de referencia de 500 MHz que se divide y se envía a las entradas de referencia de cuatro circuitos integrados de sintetizador PLL separados, como se muestra arriba en la Figura 1. Esta señal de 500 MHz también está acoplada y amplificada a 10 dB y se envía a otro circuito integrado de búfer de reloj que es responsable de generar las referencias del sistema (SYSREF) y los relojes BBP necesarios para la interfaz digital. El objetivo de este árbol de reloj es triple, ya que:

- Permite retrasos SYSREF de canal individual para corregir cualquier falta de coincidencia de longitud de seguimiento entre circuitos integrados.

- Permite el ajuste de fase del sintetizador / PLL individual y, por lo tanto, garantiza la sincronización entre las respectivas fuentes de reloj IC del digitalizador, para compensar cualquier gradiente térmico inducido dentro del sistema.

- Permite al usuario lograr los requisitos de configuración y retención necesarios para los circuitos integrados de digitalización.

Los circuitos integrados de árbol de reloj se eligen para demostrar que varias anomalías en el diseño de la placa se pueden corregir en software y / o hardware con la ayuda de bloques de retardo digitales y analógicos presentes en estos chips. En última instancia, el resultado es un árbol de reloj que puede proporcionar un pulso SYSREF a todos los circuitos integrados necesarios dentro del mismo ciclo de reloj de muestra de cada uno de estos circuitos integrados.

Interfaz digital con procesador de banda base

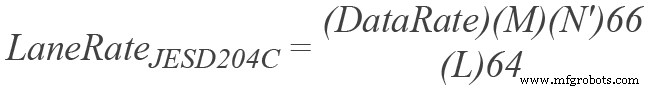

Cada uno de los cuatro circuitos integrados de digitalización establece una interfaz de enlace digital JESD204B o JESD204C con el BBP. 1,2 Esta interfaz es responsable de transmitir los códigos ADC y DAC a través de las trazas físicas (SERDES) hacia y desde el BBP. El número de trazas diferenciales de SERDES utilizadas en esta interfaz se denomina número de carriles (L) para este enlace. La resolución de bits del convertidor enviada a través del enlace se considera N '. El número de rutas de datos canalizadas, también convertidores virtuales acuñados, se etiqueta como M. Los resultados que se muestran en este artículo utilizan un enlace JESD204C con M =16, N '=16, L =4 para los enlaces del lado DAC y M =8 , N '=16, L =2 para los enlaces del lado de ADC.

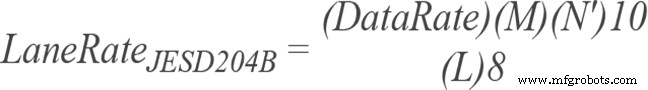

La velocidad a la que se transmiten y reciben los datos entre el IC digitalizador y el BBP se denomina velocidad de carril. Los bloques DSP en silicio (es decir, los DDC / DUC) permiten al usuario muestrear los digitalizadores a una velocidad diferente a la velocidad de datos enviada a través de los carriles físicos. Como tal, la tasa de carril depende de la tasa de datos interpolados / diezmados digitalmente para cada ruta de datos. Para este trabajo, se ha utilizado una velocidad de datos I / Q de 250 MSPS. Para una interfaz JESD204C, la tasa de carril se define como:

mientras que para una interfaz JESD204B, la tasa de carril se define como:

Los resultados que se muestran en este artículo utilizan una velocidad de carril de 16,5 Gbps para los enlaces JESD204C del lado del ADC y del DAC.

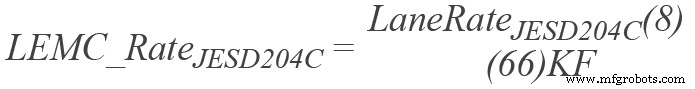

Cada enlace JESD204B / JESD204C se puede establecer dentro de diferentes subclases. Estas subclases se separan en función de si se requiere sincronización multichip o latencia determinista. Para este trabajo, los datos mostrados utilizan un modo de subclase 1 JESD204C y, por lo tanto, utilizan señales SYSREF para alinear partes de los datos digitales transmitidos a través de los múltiples enlaces presentes dentro del sistema. Específicamente, en este modo de subclase 1 JESD204C, las señales SYSREF se utilizan para alinear el contador multibloque extendido local (LEMC), que transmite a una velocidad:

donde F es el número de octetos por trama JESD por carril y K es el número de tramas por única multitrama. Para este trabajo, F =8 y K =32, y por lo tanto se utiliza una tasa LEMC de 7.8125 MSPS. El conocimiento de esta tasa LEMC es importante, ya que cualquier rutina de MCS exitosa deberá demostrar que las frecuencias de RF que no son un múltiplo entero de la tasa LEMC pueden lograr una fase de encendido determinista.

Método de sincronización de varios chips

Dentro de este sistema, los circuitos integrados ADC / DAC integrados de banda ancha proporcionan circuitos MCS para permitir una fase determinista de encendido en todos los canales de RF de transmisión y recepción, incluso mientras se utilizan los bloques DSP DUC / DDC dentro del IC. Esta función MCS permite a los usuarios completar una tabla de búsqueda (LUT) durante una calibración de fábrica para minimizar el tiempo de inactividad operativo. Cualquier demostración exitosa de MCS debe ser capaz de proporcionar una fase determinista en todos los canales dentro del sistema para cada frecuencia de RF, gradiente térmico y ciclo de energía del sistema que se intente.

Los circuitos integrados ADC / DAC integrados contienen 12 bloques DUC y 12 bloques DDC, como se muestra arriba en la Figura 1. Cada uno de estos bloques contiene un subbloque de interpolación (DUC) o diezmado (DDC) para cambiar la velocidad de datos de la señal de entrada digital DAC o Señal de salida digitalizada ADC, respectivamente. También dentro de cada DUC / DDC hay un oscilador de control numérico (NCO) complejo, que permite la traducción de frecuencia dentro del dominio digital. Cada uno de estos suboficiales es capaz de realizar un ajuste de fase complejo en tiempo real, de modo que la señal digital entre el DAC / ADC y el BBP se puede modificar para compensar varios desajustes de longitud de traza SERDES.

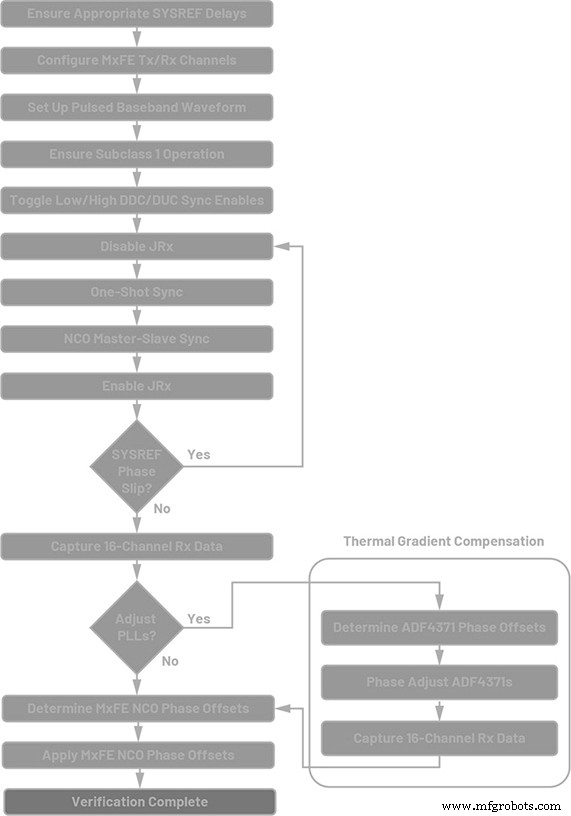

La función MCS para estos circuitos integrados ADC / DAC es responsable de lograr el determinismo de fase en todos los aspectos de la ruta de datos del circuito integrado digitalizador. El flujo de trabajo para lograr MCS se muestra en la Figura 2.

haz clic para ver la imagen en tamaño completo

Figura 2. El flujo de trabajo de MCS involucra características separadas que alinean diferentes partes de la ruta de datos. (Fuente:Analog Devices)

El algoritmo MCS se puede dividir en dos funciones independientes:

- Sincronización única:esta función es responsable de alinear los datos de banda base que se envían a través de los carriles físicos de todos los circuitos integrados del digitalizador dentro del sistema de subarreglos.

- Sincronización maestro-esclavo NCO:esta función es responsable de alinear todos los NCO en todos los circuitos integrados digitalizadores diferentes dentro del sistema de subarreglos.

La función de sincronización de un solo paso primero requiere que el usuario defina los parámetros de enlace JESD (como M, N ', L, etc.) y luego configure la lógica de sincronización para cualquier promedio SYSREF deseado (si usa pulsos SYSREF continuos). Además, los retrasos de LEMC deseados se pueden utilizar para forzar que el LEMC se genere con un cierto retraso después del borde SYSREF. Una vez completado esto, el usuario habilita el bit de sincronización de un solo paso dentro de cada IC digitalizador y luego solicita que se envíen pulsos SYSREF a cada IC dentro del mismo ciclo de reloj, como se muestra en la Figura 3.

haz clic para ver la imagen en tamaño completo

Figura 3. El algoritmo MCS utiliza señales SYSREF para implementar una sincronización de un solo paso y señales GPIO para implementar la sincronización NCO maestro-esclavo para lograr una fase determinista. (Fuente:Analog Devices)

Para este sistema, se han introducido retardos finos analógicos dentro del CI del búfer de reloj para permitir SYSREF síncronos a todos los CI del digitalizador. Se puede ejecutar una verificación posterior para verificar que el proceso de sincronización de una sola vez se haya realizado correctamente consultando registros dentro de cada IC que brinden información sobre la relación de fase entre la señal SYSREF y el límite LEMC del enlace de cada IC.

Una vez que se mide una fase estable (es decir, una vez que el registro de fase SYSREF-LEMC lee 0), el usuario sabe que los LEMC de todos los circuitos integrados del digitalizador están alineados y el usuario puede continuar con el proceso de sincronización maestro-esclavo NCO. Para esta actividad, las subtareas descritas para la sincronización única están contenidas en una interfaz de programación de aplicaciones (API) proporcionada por el fabricante del chip.

La función de sincronización NCO maestro-esclavo primero asigna uno de los circuitos integrados digitalizadores dentro del subarreglo para que actúe como un chip maestro, como se muestra arriba en la Figura 3. Todos los demás digitalizadores se consideran entonces circuitos integrados esclavos. El IC maestro está configurado de manera que el pin GPIO0 de este dispositivo se configura como una salida y se enruta a las redes GPIO0 de los tres IC digitalizadores esclavos. Las redes GPIO0 esclavas se configuran como entradas. A continuación, el usuario puede optar por disparar en el pulso SYSREF, el flanco ascendente de LEMC o el flanco descendente de LEMC. Para los datos que se muestran en este artículo, el borde ascendente de LEMC se utiliza como fuente de activación de sincronización maestro-esclavo NCO y las redes GPIO se enrutan a través de BBP en lugar de localmente en el subarreglo. A continuación, los bits de sincronización de DDC se cambian a bajo y luego a alto para armar el algoritmo de sincronización de NCO del lado de ADC. Del mismo modo, el bit de alineación del microprocesador se cambia a bajo y luego a alto para armar el algoritmo de sincronización de NCO del lado DAC.

Cuando se solicita este disparador, en el próximo flanco ascendente de LEMC, el IC del digitalizador maestro afirma una señal de salida maestra alta a través de su red GPIO0. Esta señal se propaga a las entradas GPIO0 de cada uno de los dispositivos esclavos. En el siguiente borde de LEMC, todos los circuitos integrados de digitalizadores experimentan un algoritmo de reinicio de NCO. Después de esto, cualquier pulso LEMC se ignora con respecto al algoritmo de sincronización maestro-esclavo NCO. Al igual que con la sincronización de un solo paso, estas subtareas de sincronización maestro-esclavo de NCO están incluidas dentro de las funciones de la API para facilitar el uso del usuario.

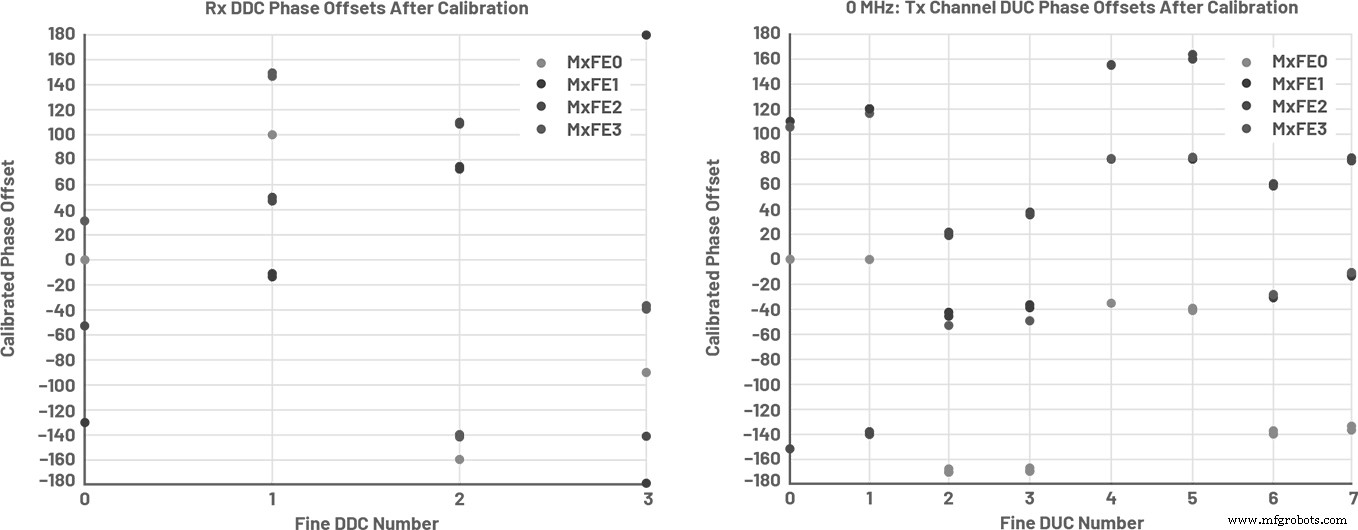

El uso de la sincronización de un solo paso y las funciones de sincronización maestro-esclavo NCO alinea ambas entradas con cada DDC / DUC de manera que el desfase de salida de cada canal de recepción y transmisión se puede repetir después de varios ciclos de encendido, como se muestra en la Figura 4. Los datos en la Figura 4 se muestran las compensaciones de fase calibradas durante 100 ciclos de energía (indicados por múltiples puntos sólidos) para cada canalizador de recepción y transmisión mientras el sistema está operando bajo un gradiente térmico estático durante cada reinicio.

haz clic para ver la imagen en tamaño completo

Figura 4. Los DDC finos de recepción (izquierda) y los DUC finos de transmisión (derecha) están alineados correctamente al realizar el algoritmo MCS. (Fuente:Analog Devices)

Como se puede ver en los múltiples puntos presentes en esta figura, los puntos de cada color para un DDC / DUC dado están todos agrupados estrechamente en la misma posición después de los ciclos de energía, representando así la fase determinista para ese canal en particular. Para los datos de esta prueba, los ocho DUC del canalizador se han utilizado en el lado de transmisión, mientras que sólo se utilizan cuatro de los ocho DDC del canalizador. Sin embargo, se ha confirmado que, de hecho, los ocho DDC de canalizador proporcionan una fase determinista al utilizar también el algoritmo MCS.

La emisión de este algoritmo en el arranque establece una fase determinista para cada canal si los relojes de muestra del sintetizador PLL y los IC SYSREF de reloj mantienen la misma relación de fase en el arranque. Sin embargo, cualquier sistema sufrirá gradientes térmicos, lo que puede resultar en una desviación del reloj PLL, y que puede resultar en una fase de encendido diferente si no se compensa. Para compensar la deriva del gradiente térmico dentro del sistema, esta plataforma utiliza ajustes de fase del sintetizador PLL.

En la siguiente parte de esta serie de artículos, exploraremos los ajustes de fase del sintetizador PLL, la escalabilidad a múltiples subarreglos y los algoritmos de calibración a nivel del sistema.

Referencias

1 Del Jones. "Manual JESD204C:Novedades y ventajas:Parte 1". Diálogo analógico , Vol. 53, No. 2, junio de 2019.

2 Del Jones. "Manual JESD204C:Novedades y ventajas para usted:Parte 2". Diálogo analógico , Vol. 53, No. 3, julio de 2019.

Incrustado

- Cambio de fase

- Fase CA

- Rotación de fase

- Reloj de cuco

- C # usando

- MACOM presenta un nuevo amplificador de ruido de fase ultrabaja

- Keysight lanza un nuevo sistema de prueba de ruido de fase

- El uso de varios chips de inferencia requiere una planificación cuidadosa

- Cómo generar una forma de onda de alta precisión utilizando un DAC y una PCB personalizada

- Generador de reloj Verilog

- Uso de una fresadora como torno