Cómo hacer que los procesadores sean confiables

Los circuitos integrados modernos (IC) proporcionan las capacidades de control de sistemas y computacionales para procesar enormes cantidades de datos, tomar decisiones críticas para la seguridad en tiempo real y proteger los datos confidenciales. Diseñar un circuito integrado de aplicación específica (ASIC) o un sistema en chip (SoC) de matriz de compuerta programable en campo (FPGA) desde cero sería prohibitivamente costoso y consumiría mucho tiempo. Muchas funciones críticas se implementan utilizando propiedades intelectuales (IP) de terceros. Los núcleos de procesador, por ejemplo, provienen de organizaciones especializadas y proporcionan una función flexible programable por software a través de su arquitectura de conjunto de instrucciones (ISA), que define la interfaz entre el hardware y el software. Las arquitecturas de procesador de código abierto brindan una oportunidad para un escrutinio más profundo y una garantía de seguridad rigurosa en sistemas que ya enfrentan un entorno de amenazas fluido. Este artículo describe un enfoque para proporcionar garantía de seguridad de IP y SoC basado en el ISA de código abierto RISC-V.

Inventado en la Universidad de California y administrado por la fundación sin fines de lucro RISC-V, RISC-V es el primer ISA de código abierto que se convierte en una opción industrial genuinamente viable para una amplia gama de aplicaciones.

RISC-V es un ISA de código abierto inventado en la Universidad de California y administrado por la Fundación RISC-V, una organización sin fines de lucro con más de 300 miembros fundada en 2015. RISC-V es el primer ISA de código abierto en convertirse en un Opción industrial genuinamente viable para una amplia gama de aplicaciones. El ecosistema de herramientas, software y experiencia es sólido y crece constantemente. Muchas personas y organizaciones ya han donado IP de hardware de código abierto que implementan RISC-V ISA. El Grupo OpenHW, por ejemplo, tiene como objetivo hacer realidad la perspectiva tan esperada del hardware de código abierto, en particular, los núcleos de procesador, para chips de gran volumen.

El surgimiento de RISC-V tiene muchas razones detrás. Construido desde cero con la extensibilidad personalizada en mente, RISC-V permite un nuevo nivel de optimización de hardware para cargas de trabajo específicas. La ley de Moore se está desacelerando y la personalización es crucial para mantener el nivel de mejoras de rendimiento que los avances tecnológicos en el proceso de fabricación de semiconductores ya no pueden proporcionar. Además, la arquitectura RISC-V está libre de costos de licencia y regalías, lo que permite a más empresas desarrollar productos innovadores y asequibles. Mucho está sucediendo en el campo de IoT y dispositivos portátiles con capacidades de inteligencia artificial, por ejemplo.

Los integradores de SoC a menudo utilizan IP de procesador RISC-V de código abierto o de terceros. Estos diseños y sus cadenas de herramientas asociadas se pueden ampliar con instrucciones personalizadas. Un entorno de verificación de alta calidad entregado con la IP y pruebas adicionales a nivel del sistema pueden brindar cierta confianza en que la IP no tiene errores críticos. Desafortunadamente, para muchas aplicaciones, esto no es suficiente y existen otros riesgos graves a considerar.

Vulnerabilidades y troyanos

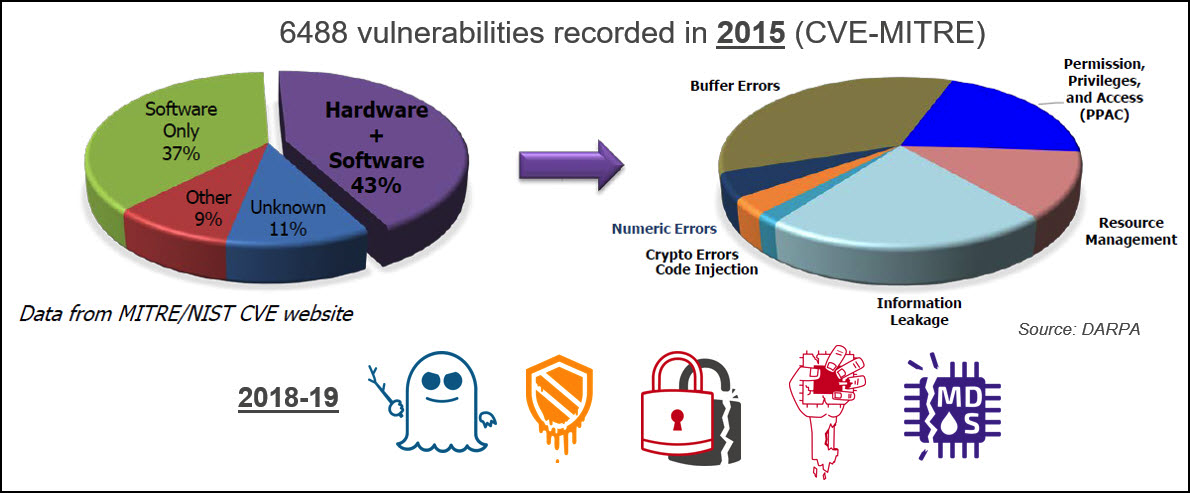

Tradicionalmente, las vulnerabilidades de seguridad en los sistemas electrónicos se han asociado con problemas de software y a nivel del sistema. Más recientemente, las IP de hardware, principalmente procesadores, también se han convertido en una preocupación central (ver Fig. 1). Las implementaciones de procesadores utilizan microarquitecturas basadas en canalizaciones y, a menudo, incluyen funciones de optimización de potencia y rendimiento. La complejidad aumenta el riesgo de perder no solo errores funcionales sino también vulnerabilidades de seguridad. Los investigadores de seguridad que descubrieron los ataques Meltdown y Spectre a principios de 2018 han demostrado que las funciones de optimización del rendimiento en los procesadores se pueden utilizar de formas no deseadas con fines nefastos. Desde entonces, se han descubierto muchas más vulnerabilidades en procesadores de gama alta y baja. Los canales laterales y los ataques de ejecución transitoria pueden violar enclaves seguros y permitir que aplicaciones maliciosas filtren datos confidenciales o incluso tomen el control del sistema. Y a diferencia del software, los problemas de hardware no se pueden reparar fácilmente con actualizaciones inalámbricas. Abordar un problema de hardware a través del software a menudo provoca una grave degradación del rendimiento.

La arquitectura RISC-V tiene muchas características que respaldan la implementación de sistemas integrados seguros. La especificación de privilegios define cuatro modos de privilegio (máquina, supervisor, hipervisor y usuario), por ejemplo. Las instrucciones personalizadas y las extensiones ISA en proceso de ratificación, como la extensión criptográfica, brindan capacidades de seguridad adicionales. Los diseñadores pueden implementar múltiples enclaves seguros para aislar aplicaciones y prevenir la fuga de datos confidenciales. Sin embargo, las características de la microarquitectura RTL aún pueden resultar en vulnerabilidades de seguridad. Estos riesgos no se pueden abordar por completo a nivel ISA. Un nuevo enfoque en exploración es el uso de una ISA aumentada (aISA) para definir aspectos de la ejecución de instrucciones a nivel de microarquitectura y, por ejemplo, controlar el estado de los búferes o registros no visibles a nivel de ISA. Los errores funcionales de RTL aún podrían comprometer todas estas características de seguridad.

Un riesgo menos probable, pero con una gravedad mucho mayor, es la presencia de troyanos lógicos o de hardware maliciosos en el núcleo de RISC-V. Un troyano de hardware es una función lógica diseñada deliberadamente para ser sigilosa, que se activa en circunstancias muy raras conocidas solo por el atacante. Una secuencia específica de datos y eventos de control que no ocurrirían mientras el sistema está operando en sus casos de uso objetivo activa la lógica troyana, que a su vez entrega una carga útil dañina, filtrando un secreto o corrompiendo críticamente el comportamiento del sistema, por ejemplo. Las integraciones de SoC que utilizan núcleos RISC-V de código abierto o de terceros ya no pueden ignorar este riesgo.

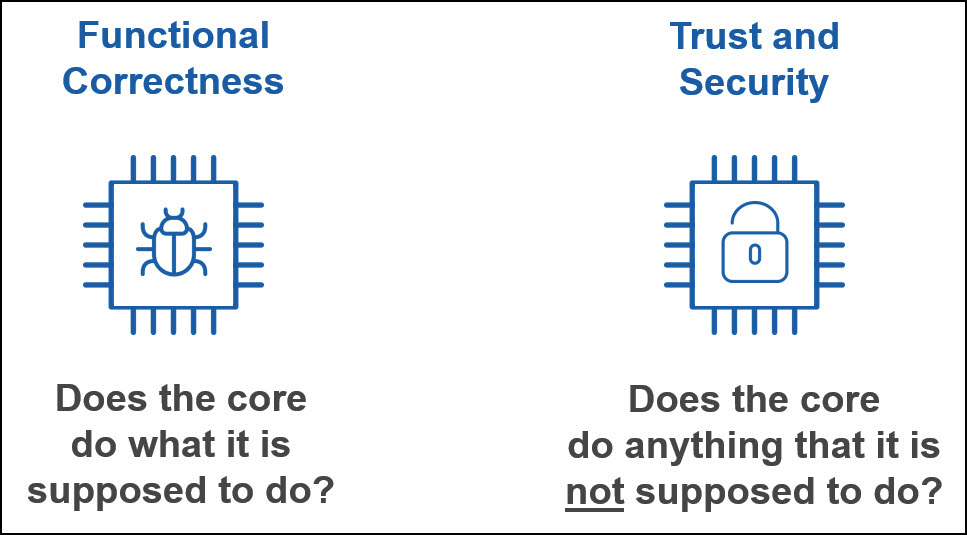

Asegurarse de que un procesador haga lo que se supone que debe hacer es difícil, pero asegurarse de que no haga nada que se supone que no debe hacer es una tarea aún más desafiante que aún no se ha abordado en gran medida. Los sistemas críticos para la seguridad y los sistemas donde la protección de la privacidad de los datos es primordial, necesitan soluciones eficientes y de alta calidad que aborden el riesgo de vulnerabilidades de seguridad y troyanos.

Figura 1:La base de datos CVE-MITRE registró 6488 vulnerabilidades en 2015, el 43% de las cuales se pueden clasificar como vulnerabilidades de hardware asistidas por software. En 2018 y 2019, los investigadores descubrieron e informaron numerosas vulnerabilidades en procesadores, incluidos Meltdown y Spectre, Foreshadow, ZombieLoad y RIDL y Fallout. (Fuente:DARPA y OneSpin)

Smart Hardware Assurance

Garantizar la confianza y la seguridad de las IP de RISC-V requiere soluciones técnicas innovadoras y eficientes que sean complementarias a los enfoques de corrección funcional, dirigidas principalmente a los casos de uso previstos de IP (ver Fig. 2). Los proveedores de IP son responsables de aplicar procesos de verificación de seguridad y confianza de última generación, mientras que los integradores de IP deben tener acceso a soluciones de aseguramiento independientes que se puedan implementar rápidamente y sin un conocimiento profundo de los detalles de implementación de IP.

Los métodos formales pueden analizar las funciones de hardware de manera exhaustiva y proporcionar pruebas de que la IP o el SoC coinciden con precisión con un comportamiento esperado que a menudo se captura en las afirmaciones de SystemVerilog. La verificación formal de hardware mediante comprobadores de modelos comerciales ha disfrutado de una adopción generalizada durante la última década. Por lo general, los proveedores de IP y los integradores de SoC tienen expertos en verificación formal en sus filas, tratando de reducir al mínimo el riesgo de fallar errores funcionales. Si bien ciertas tareas de verificación formales bien definidas se pueden automatizar a través de Aplicaciones , en general, es necesario un esfuerzo de ingeniería significativo para capturar el comportamiento esperado del IP en las afirmaciones. Además, no hay garantía de que se hayan escrito suficientes afirmaciones. Las funciones no documentadas o las lagunas no intencionadas en el conjunto de afirmaciones podrían dar lugar a una funcionalidad de IP no verificada.

La naturaleza de código abierto de RISC-V permite el desarrollo de soluciones de aseguramiento independientes preempaquetadas. La solución de verificación de integridad RISC-V de OneSpin, por ejemplo, se puede aplicar a una amplia gama de microarquitecturas. Incluye modelos de RISC-V ISA e ISA privilegiado que son extensibles y pueden acomodar instrucciones personalizadas. Un aspecto crucial de esta solución es que se basa en el proceso GapFreeVerification ™ de OneSpin, que ofrece una prueba rigurosa de que el conjunto de afirmaciones que modelan el RISC-V ISA está completo y libre de lagunas. Este aspecto es de suma importancia cuando la detección de troyanos de hardware o lógica indocumentada es un objetivo crucial. La solución permite a los integradores de SoC con experiencia limitada en RISC-V y la implementación de RTL bajo escrutinio ganar confianza en la calidad y confiabilidad de la IP. Los desarrolladores de IP pueden usarlo para detectar debilidades de seguridad y errores funcionales antes de su lanzamiento.

Figura 2:La verificación de la corrección funcional proporciona la confianza de que la implementación de un procesador se comporta como se especifica y satisface los requisitos de los usuarios finales. La verificación de confianza y seguridad, por otro lado, brinda la confianza de que el procesador no tiene funciones indocumentadas, canales laterales imprevistos, troyanos de hardware u otras vulnerabilidades que puedan ser explotadas por actores malintencionados. (Fuente:OneSpin)

¿Funciona?

El proceso de garantía de integridad RISC-V descrito en la sección anterior se ha aplicado con éxito a múltiples diseños RTL. Edaptive Computing, una empresa que integra soluciones innovadoras para optimizar, asegurar y automatizar rápidamente sistemas de sistemas y procesos para una variedad de clientes del Departamento de Defensa de EE. UU. Y del sector comercial, ha aplicado el proceso a RocketCore, por ejemplo. El RocketCore es un núcleo RISC-V de 64 bits probado en silicio de código abierto con un sistema de memoria virtual de 39 bits. Tiene una canalización en orden de cinco etapas, un solo problema, con finalización fuera de orden para instrucciones de latencia prolongada, como la división. Incluye las funciones avanzadas de predicción de rama y reproducción de instrucciones.

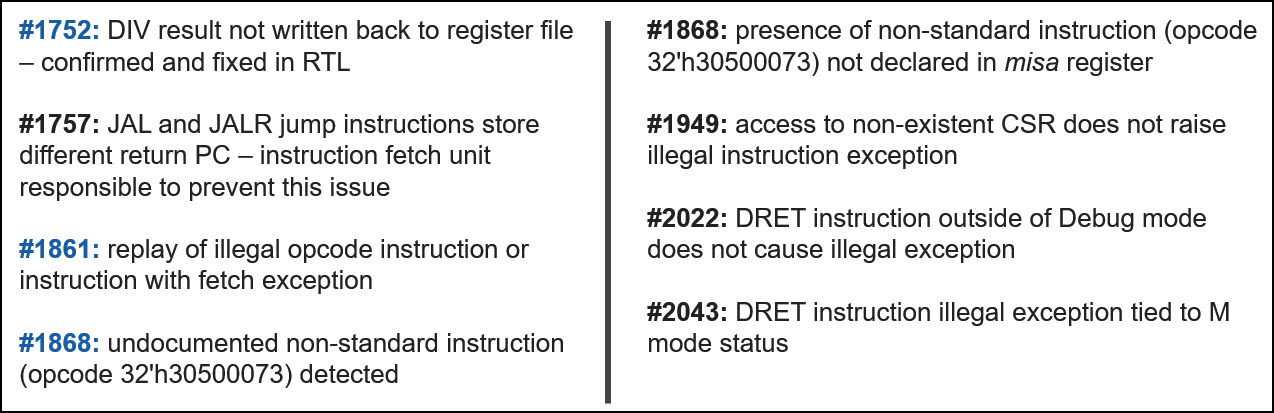

La Solución de Verificación de Integridad RISC-V se aplicó al diseño con todas las instrucciones, niveles de privilegios, interrupciones y mecanismos de excepción, y se detectaron 8 problemas (ver Fig. 3). A continuación, se proporciona información adicional sobre 3 de ellos.

Esquinero de división :un error profundo en el caso de las esquinas asociado con la finalización desordenada de la instrucción de división. Este problema podría haber causado que un programa de software que utiliza la operación de división calcule resultados incorrectos y provoque un mal comportamiento del sistema. El problema aparece solo en una combinación de circunstancias excepcionales, y es por eso que los esfuerzos de verificación anteriores no lo detectaron.

Reproducción de instrucción ilegal :este no es un error de caso de esquina. Reproducir una instrucción ilegal puede desperdiciar los ciclos de procesamiento, pero si esto ocurre solo en situaciones excepcionales, el impacto en el rendimiento es insignificante. Sin embargo, hay otros aspectos a considerar. La reproducción de instrucciones puede provocar solicitudes de memoria innecesarias. Estas solicitudes pueden tener efectos secundarios que podrían aprovecharse en ataques de canal lateral. Como resultado, este comportamiento debe eliminarse o entenderse y documentarse claramente.

Instrucción no documentada :se detectó una instrucción no estándar no documentada llamada CEASE que detiene el núcleo. En efecto, el RISC-V RocketCore podría hacer algo que se suponía que no debía hacer. Las funciones ocultas no documentadas no son aceptables cuando la confianza y la seguridad son una preocupación, incluso cuando se relacionan con casos de uso que se consideran no relevantes para la aplicación final.

El estudio de caso de RocketCore se presenta en detalle en el documento de GOMACTech 2019 titulado Verificación formal completa de las direcciones IP del procesador RISC-V para circuitos integrados de confianza sin troyanos. Para obtener una copia, visite onespin.com/resources/white-papers.

Figura 3:Lista de problemas detectados por las soluciones de verificación de integridad RISC-V de OneSpin e informados en el proyecto GitHub RocketCore. (Fuente:OneSpin)

¿Qué sigue?

El proceso de garantía RISC-V presentado en este artículo detecta escenarios que podrían afectar la seguridad y desvela sistemáticamente funciones no documentadas y troyanos de hardware que afectan el comportamiento del procesador, independientemente de cuán raros y sigilosos puedan ser. Sin embargo, los canales laterales no se detectan sistemáticamente. La detección exhaustiva de todos los canales laterales potenciales requiere una solución dedicada con la tecnología adecuada. Ya existen prototipos que abordan este desafío. Para obtener más información, visite onespin.com/resources/technical-articles y lea el artículo de EE Times Ataques de canal lateral en procesadores integrados .

Los núcleos de procesador son direcciones IP cruciales dentro de los sistemas integrados. Sin embargo, un SoC típico integra muchas otras IP que también podrían contener troyanos de hardware. A diferencia de los núcleos RISC-V, es posible que las soluciones independientes de garantía de confianza no estén fácilmente disponibles. En este caso, sería valioso tener un proceso de evaluación de confianza automatizado y de bajo esfuerzo aplicable a cualquier IP. Un proceso que no incluye un modelo confiable de IP no puede garantizar la ausencia de un troyano. Sin embargo, es posible identificar patrones de código inusuales y sospechosos y firmas troyanas conocidas, y debilidades que podrían explotarse en etapas posteriores de desarrollo con fines nefastos. Un documento sobre este tema titulado Evaluación automatizada de confiabilidad de IP previa al silicio para la garantía del hardware , escrito por AEROSPACE Corporation y los ingenieros de OneSpin, se presentará en la conferencia GOMACTech 2020.

Incrustado

- Cómo aprovechar al máximo sus datos

- Una guía para acelerar aplicaciones con las instrucciones personalizadas de RISC-V adecuadas

- Cómo hacer una plataforma de robot Arduino + Raspberry Pi

- Cómo hacer que el mantenimiento basado en condiciones sea más eficaz

- Cómo hacer fibra de vidrio

- Cómo hacer que los datos de la cadena de suministro sean confiables

- Cómo hacer una animación de corte en Solidworks

- Como hacer un prototipo

- Cómo reemplazar una manguera hidráulica

- Cómo hacer que funcione un programa integral de seguridad

- Cómo hacer un portabrocas para torno de metal