Cómo usar la creación de instancias de mapas de puertos en VHDL

Un módulo es una unidad autónoma de código VHDL. Los módulos se comunican con el mundo exterior a través de la entidad . Mapa del puerto es la parte de la instanciación del módulo en la que declara a qué señales locales se conectarán las entradas y salidas del módulo.

En tutoriales anteriores de esta serie, hemos estado escribiendo todo nuestro código en el archivo VHDL principal, pero normalmente no haríamos eso. Creamos lógica con el propósito de usarla en un diseño FPGA o ASIC, no para el simulador.

Un módulo VHDL creado para ejecutarse en un simulador generalmente no tiene señales de entrada o salida. Es completamente autónomo. Por eso la entidad de nuestros diseños ha quedado vacía. No ha habido nada entre el entity etiqueta y el end entity; etiqueta.

Esta publicación de blog es parte de la serie Tutoriales básicos de VHDL.

Un módulo sin señales de entrada o salida no se puede utilizar en un diseño real. Su único propósito es permitirnos ejecutar código VHDL en un simulador. Por lo tanto, se lo conoce como un banco de prueba . Para simular un módulo con señales de entrada y salida tenemos que instanciar en un banco de pruebas.

Los módulos y los bancos de pruebas a menudo vienen en pares y se almacenan en archivos diferentes. Un esquema de nomenclatura común es llamar al banco de pruebas el nombre del módulo con "Tb" adjunto, y nombrar la arquitectura "sim". Si el módulo se llama "MyModule", el banco de pruebas se llamará "MyModuleTb". En consecuencia, los nombres de archivo se convierten en "MyModuleTb.vhd" y "MyModule.vhd".

Con la ayuda del código del banco de pruebas podemos verificar que el módulo funciona correctamente en un entorno de simulación. El módulo que se está probando se conoce comúnmente como el dispositivo bajo prueba (DUT).

Los módulos también se pueden instanciar dentro de otros módulos. Particionar el código en módulos permite instanciarlo varias veces. Puede crear varias instancias de un módulo dentro del mismo diseño y se puede reutilizar en muchos diseños.

La sintaxis para una entidad con puerto en VHDL es:entity <entity_name> is

port(

<entity_signal_name> : in|out|inout <signal_type>;

...

);

end entity;

La sintaxis para instanciar dicho módulo en otro archivo VHDL es:<label> : entity <library_name>.<entity_name>(<architecture_name>) port map(

<entity_signal_name> => <local_signal_name>,

...

);

El <label> puede ser cualquier nombre y aparecerá en la ventana de jerarquía en ModelSim. El <library_name> para un módulo se establece en el simulador, no en el código VHDL. Por defecto, cada módulo se compila en el work biblioteca. El <entity_name> y <architecture_name> debe coincidir con el módulo del que estamos creando una instancia. Finalmente, cada una de las señales de entidad debe asignarse a un nombre de señal local.

Hay otras formas de instanciar un módulo en VHDL, pero esta es la sintaxis básica para la instanciación explícita.

Ejercicio

En este video tutorial aprenderemos a crear e instanciar un módulo en VHDL:

El código final para el testbench de MUX :

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T15_PortMapTb is

end entity;

architecture sim of T15_PortMapTb is

signal Sig1 : unsigned(7 downto 0) := x"AA";

signal Sig2 : unsigned(7 downto 0) := x"BB";

signal Sig3 : unsigned(7 downto 0) := x"CC";

signal Sig4 : unsigned(7 downto 0) := x"DD";

signal Sel : unsigned(1 downto 0) := (others => '0');

signal Output : unsigned(7 downto 0);

begin

-- An instance of T15_Mux with architecture rtl

i_Mux1 : entity work.T15_Mux(rtl) port map(

Sel => Sel,

Sig1 => Sig1,

Sig2 => Sig2,

Sig3 => Sig3,

Sig4 => Sig4,

Output => Output);

-- Testbench process

process is

begin

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= "UU";

wait;

end process;

end architecture;

El código final para el módulo MUX :

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T15_Mux is

port(

-- Inputs

Sig1 : in unsigned(7 downto 0);

Sig2 : in unsigned(7 downto 0);

Sig3 : in unsigned(7 downto 0);

Sig4 : in unsigned(7 downto 0);

Sel : in unsigned(1 downto 0);

-- Outputs

Output : out unsigned(7 downto 0));

end entity;

architecture rtl of T15_Mux is

begin

process(Sel, Sig1, Sig2, Sig3, Sig4) is

begin

case Sel is

when "00" =>

Output <= Sig1;

when "01" =>

Output <= Sig2;

when "10" =>

Output <= Sig3;

when "11" =>

Output <= Sig4;

when others => -- 'U', 'X', '-', etc.

Output <= (others => 'X');

end case;

end process;

end architecture;

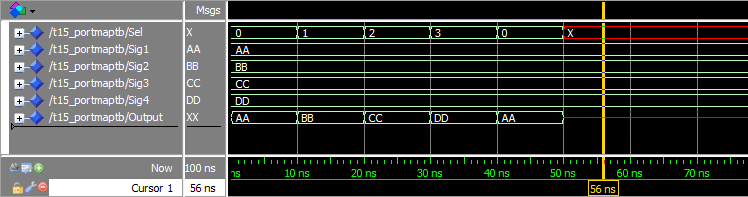

La ventana de forma de onda en ModelSim después de presionar Ejecutar y hacer zoom en la línea de tiempo:

Análisis

Como podemos ver en la forma de onda, el módulo multiplexor (MUX) funciona como se esperaba. La forma de onda es idéntica a la del tutorial anterior que creamos sin usar módulos.

Ahora hay una clara separación entre el módulo de diseño y el banco de pruebas. El módulo que contiene el MUX es lo que pretendemos usar en un diseño, y el único propósito del banco de pruebas es permitirnos ejecutarlo en un simulador. Hay un proceso en el banco de pruebas que usa wait instrucciones para crear retardos de tiempo artificiales en la simulación. El módulo de diseño no tiene noción del tiempo, solo reacciona a estímulos externos.

Llamamos a la arquitectura del banco de pruebas sim , para simulación. La arquitectura del módulo de diseño se denominó rtl , que significa nivel de transferencia de registro. Estas son solo convenciones de nomenclatura. Cuando ve un archivo con ese nombre, inmediatamente sabe si es un banco de pruebas o un módulo de diseño. Diferentes empresas pueden tener diferentes convenciones de nomenclatura.

Para llevar

- Las señales de entrada y salida se especifican en la entidad de un módulo

- Un módulo sin señales de entrada/salida se denomina banco de prueba , y solo se puede usar en un simulador

- Por lo general, un módulo con señales de entrada/salida no se puede ejecutar directamente en un simulador

Ir al siguiente tutorial »

VHDL

- ¿Cómo utilizamos el molibdeno?

- Cómo crear una lista de cadenas en VHDL

- Cómo crear un banco de pruebas controlado por Tcl para un módulo de bloqueo de código VHDL

- Cómo detener la simulación en un banco de pruebas VHDL

- Cómo crear un controlador PWM en VHDL

- Cómo generar números aleatorios en VHDL

- Cómo usar un procedimiento en un proceso en VHDL

- Cómo usar una función impura en VHDL

- Cómo usar una función en VHDL

- Cómo crear una máquina de estados finitos en VHDL

- Cómo usar una amoladora cortadora