Simulación Verilog

Verilog es un lenguaje de descripción de hardware y no es necesario que los diseñadores simulen sus diseños RTL para poder convertirlos en puertas lógicas. Entonces, ¿cuál es la necesidad de simular?

La simulación es una técnica de aplicar diferentes estímulos de entrada al diseño en diferentes momentos para verificar si el código RTL se comporta de la manera prevista. Esencialmente, la simulación es una técnica bien seguida para verificar la robustez del diseño. También es similar a cómo se usará un chip fabricado en el mundo real y cómo reacciona a diferentes entradas.

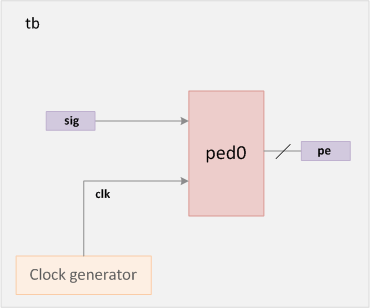

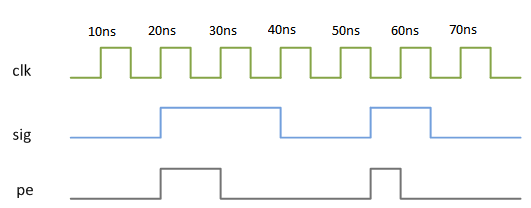

Por ejemplo, el diseño anterior representa un detector de flanco positivo con entradas de reloj y señal que se evalúan a intervalos periódicos para encontrar la salida pe como se muestra. La simulación nos permite ver el diagrama de tiempo de las señales relacionadas para comprender cómo se comporta realmente la descripción del diseño en Verilog.

Hay varias empresas de EDA que desarrollan simuladores capaz de averiguar las salidas para varias entradas al diseño. Verilog se define en términos de un evento discreto El modelo de ejecución y los diferentes simuladores son libres de usar diferentes algoritmos para proporcionar al usuario un conjunto consistente de resultados. El código de Verilog se divide en múltiples procesos e hilos y se puede evaluar en diferentes momentos en el curso de una simulación, que se abordará más adelante.

Ejemplo

El banco de pruebas llamado tb es un contenedor para albergar un módulo de diseño. Sin embargo, en este ejemplo no hemos utilizado ninguna instancia de diseño. Hay dos variables o señales que se le pueden asignar ciertos valores en momentos específicos. clk representa un reloj que se genera dentro del banco de pruebas. Esto lo hace el always declaración alternando el valor del reloj después de cada 5ns. El initial El bloque contiene un conjunto de declaraciones que asignan diferentes valores a ambas señales en diferentes momentos.

module tb;

reg clk;

reg sig;

// Clock generation

// Process starts at time 0ns and loops after every 5ns

always #5 clk = ~clk;

// Initial block : Process starts at time 0ns

initial begin

// This system task will print out the signal values everytime they change

$monitor("Time = %0t clk = %0d sig = %0d", $time, clk, sig);

// Also called stimulus, we simply assign different values to the variables

// after some simulation "delay"

sig = 0;

#5 clk = 0; // Assign clk to 0 at time 5ns

#15 sig = 1; // Assign sig to 1 at time 20ns (#5 + #15)

#20 sig = 0; // Assign sig to 0 at time 40ns (#5 + #15 + #20)

#15 sig = 1; // Assign sig to 1 at time 55ns (#5 + #15 + #20 + #15)

#10 sig = 0; // Assign sig to 0 at time 65ns (#5 + #15 + #20 + #15 + #10)

#20 $finish; // Finish simulation at time 85ns

end

endmodule

El simulador proporciona el siguiente resultado después de la ejecución del banco de pruebas anterior.

Registro de simulaciónncsim> run Time = 0 clk = x sig = 0 Time = 5 clk = 0 sig = 0 Time = 10 clk = 1 sig = 0 Time = 15 clk = 0 sig = 0 Time = 20 clk = 1 sig = 1 Time = 25 clk = 0 sig = 1 Time = 30 clk = 1 sig = 1 Time = 35 clk = 0 sig = 1 Time = 40 clk = 1 sig = 0 Time = 45 clk = 0 sig = 0 Time = 50 clk = 1 sig = 0 Time = 55 clk = 0 sig = 1 Time = 60 clk = 1 sig = 1 Time = 65 clk = 0 sig = 0 Time = 70 clk = 1 sig = 0 Time = 75 clk = 0 sig = 0 Time = 80 clk = 1 sig = 0 Simulation complete via $finish(1) at time 85 NS + 0

¿Qué es una forma de onda de simulación?

Las simulaciones nos permiten volcar el diseño y las señales del banco de pruebas en una forma de onda que se puede representar gráficamente para analizar y depurar la funcionalidad del diseño RTL. La forma de onda que se muestra a continuación se obtiene de una herramienta EDA y muestra el progreso de cada señal con respecto al tiempo y es igual al diagrama de tiempo que se muestra antes.

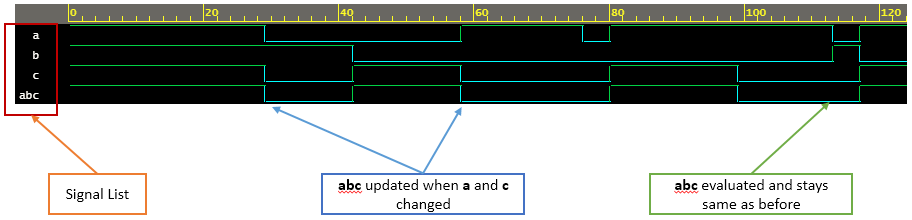

Cada cambio en el valor de una variable o red se denomina evento de actualización . Y los procesos son sensibles a los eventos de actualización de tal manera que estos procesos se evalúan cada vez que ocurre el evento de actualización y se denomina evento de evaluación . Debido a la posibilidad de que varios procesos se evalúen arbitrariamente, el orden de los cambios debe rastrearse en algo llamado cola de eventos .

Naturalmente, están ordenados por el tiempo de simulación. La colocación de un nuevo evento en la cola se denomina programación . El tiempo de simulación se utiliza para referirse al valor de tiempo mantenido por el simulador para modelar el tiempo real que le tomaría al circuito que se está simulando. Los valores de tiempo para el ejemplo anterior se muestran en nanosegundos ns en el diagrama de tiempos.

module des;

wire abc;

wire a, b, c;

assign abc = a & b | c; // abc is updated via the assign statement (process) whenever a, b or c change -> update event

endmodule

¡Actualice Verilog y vea un ejemplo!

Regiones en cola de eventos

La cola de eventos de Verilog se divide lógicamente en cinco regiones y se pueden agregar eventos a cualquiera de ellas. Sin embargo, solo se puede eliminar de la región activa.

| Eventos | Descripción |

|---|---|

| Activo | Ocurre en el momento actual de la simulación y puede procesarse en cualquier orden |

| Inactivo | Ocurre en el momento actual de la simulación, pero se procesa después de que se hayan realizado todos los eventos activos |

| Sin bloqueo | Evaluado en algún momento anterior, pero la asignación se realiza en el tiempo de simulación actual después de que se realizan los eventos activos e inactivos |

| Monitor | Procesado después de que se hayan realizado todos los eventos activos, inactivos y sin bloqueo |

| Futuro | Ocurrir en algún tiempo de simulación futuro |

Un ciclo de simulación es donde se procesan todos los eventos activos. La norma garantiza un determinado orden de programación salvo contados casos y. Por ejemplo, las instrucciones dentro de un bloque de inicio y fin solo se ejecutarán en el orden en que aparecen.

module tb;

reg [3:0] a;

reg [3:0] b;

initial begin // Statements are executed one after the other at appropriate simulation times

a = 5; // At time 0ns, a is assigned 5

b = 2; // In the same simulation step (time 0ns), b is assigned 2

#10 a = 7; // When simulation advances to 10ns, a is assigned 7

end

endmodule

La cola de eventos define esa asignación a b debería ocurrir después de la asignación a a .

Verilog

- Tutorial de Verilog

- Concatenación Verilog

- Asignaciones de Verilog

- Bloqueo y no bloqueo de Verilog

- Funciones de Verilog

- Tarea Verilog

- Compilación condicional de Verilog `ifdef

- Semántica de programación de Verilog

- Generador de reloj Verilog

- Tareas de visualización de Verilog

- Funciones matemáticas de Verilog