Verilog escalar y vectorial

Verilog necesita representar bits individuales así como grupos de bits. Por ejemplo, un elemento secuencial de un solo bit es un flip-flop. Sin embargo, un elemento secuencial de 16 bits es un registro que puede contener 16 bits. Para este propósito, Verilog tiene scalar y vectores redes y variables.

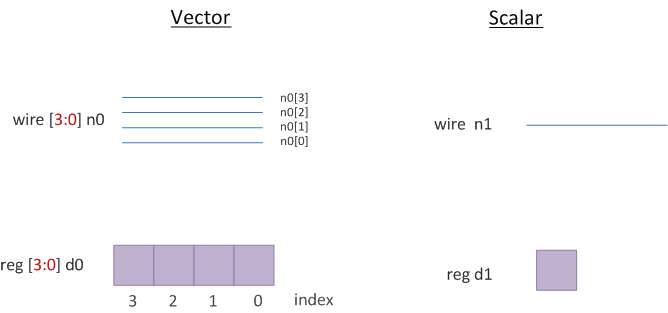

Escalares y vectoriales

Una red o reg la declaración sin una especificación de rango se considera de 1 bit de ancho y es un escalar . Si se especifica un rango, entonces la red o reg se convierte en una entidad multibit conocida como vector .

wire o_nor; // single bit scalar net

wire [7:0] o_flop; // 8-bit vector net

reg parity; // single bit scalar variable

reg [31:0] addr; // 32 bit vector variable to store address

El rango brinda la capacidad de direccionar bits individuales en un vector. El bit más significativo del vector debe especificarse como el valor de la izquierda en el rango, mientras que el bit menos significativo del vector debe especificarse a la derecha.

wire [msb:lsb] name;

integer my_msb;

wire [15:0] priority; // msb = 15, lsb = 0

wire [my_msb: 2] prior; // illegal

En el ejemplo anterior, se creará una red de 16 bits de ancho denominada prioridad. Tenga en cuenta que msb y lsb debe ser una expresión constante y no puede ser sustituida por una variable. Pero pueden ser cualquier valor entero:positivo, negativo o cero; y el lsb el valor puede ser mayor, igual o menor que el valor msb.

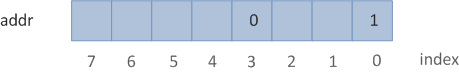

Selección de bits

Cualquier bit en una variable vectorizada puede seleccionarse individualmente y asignarse un nuevo valor como se muestra a continuación. Esto se denomina selección de bits . Si la selección de bits está fuera de los límites o la selección de bits es x o z , entonces el valor devuelto será x .

reg [7:0] addr; // 8-bit reg variable [7, 6, 5, 4, 3, 2, 1, 0]

addr [0] = 1; // assign 1 to bit 0 of addr

addr [3] = 0; // assign 0 to bit 3 of addr

addr [8] = 1; // illegal : bit8 does not exist in addr

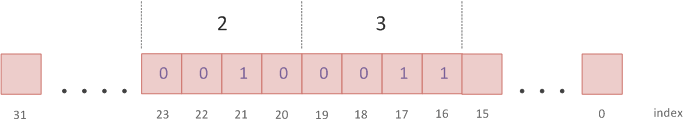

Selecciones parciales

Se puede seleccionar un rango de bits contiguos y se conoce como selección parcial . Hay dos tipos de selecciones parciales, una con una selección parcial constante y otra con una selección parcial indexada.

reg [31:0] addr;

addr [23:16] = 8'h23; // bits 23 to 16 will be replaced by the new value 'h23 -> constant part-select

Tener una selección de parte variable permite que se use de manera efectiva en bucles para seleccionar partes del vector. Aunque el bit de inicio se puede variar, el ancho debe ser constante.

[<start_bit> +: <width>] // part-select increments from start-bit [<start_bit> -: <width>] // part-select decrements from start-bit

module des;

reg [31:0] data;

int i;

initial begin

data = 32'hFACE_CAFE;

for (i = 0; i < 4; i++) begin

$display ("data[8*%0d +: 8] = 0x%0h", i, data[8*i +: 8]);

end

$display ("data[7:0] = 0x%0h", data[7:0]);

$display ("data[15:8] = 0x%0h", data[15:8]);

$display ("data[23:16] = 0x%0h", data[23:16]);

$display ("data[31:24] = 0x%0h", data[31:24]);

end

endmodule

Registro de simulación ncsim> run data[8*0 +: 8] = 0xfe // ~ data [8*0+8 : 8*0] data[8*1 +: 8] = 0xca // ~ data [8*1+8 : 8*1] data[8*2 +: 8] = 0xce // ~ data [8*2+8 : 8*2] data[8*3 +: 8] = 0xfa // ~ data [8*3+8 : 8*3] data[7:0] = 0xfe data[15:8] = 0xca data[23:16] = 0xce data[31:24] = 0xfa ncsim: *W,RNQUIE: Simulation is complete.

Errores comunes

module tb;

reg [15:0] data;

initial begin

$display ("data[0:9] = 0x%0h", data[0:9]); // Error : Reversed part-select index expression ordering

end

endmodule

Verilog

- Tutorial de Verilog

- Concatenación Verilog

- Asignaciones de Verilog

- Bloqueo y no bloqueo de Verilog

- Funciones de Verilog

- Tarea Verilog

- Retraso de asignación inter e intra de Verilog

- Generador de reloj Verilog

- Funciones matemáticas de Verilog

- Formato de hora de Verilog

- Alcance de la escala de tiempo de Verilog