Introducción a Verilog

Verilog es un tipo de lenguaje de descripción de hardware (HDL). Verilog es uno de los dos lenguajes utilizados por la educación y las empresas para diseñar FPGA y ASIC. Si no está familiarizado con el funcionamiento de los FPGA y ASIC, debe leer esta página para obtener una introducción a los FPGA y ASIC. Verilog y VHDL son los dos HDL más populares utilizados. En comparación con los lenguajes de software tradicionales como Java o C, Verilog funciona de manera muy diferente. Comencemos mirando un ejemplo simple.

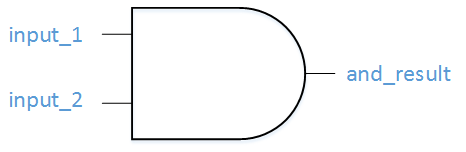

Primero crearemos un archivo Verilog que describe una puerta Y. Como repaso, un And Gate simple tiene dos entradas y una salida. La salida es igual a 1 solo cuando ambas entradas son iguales a 1. A continuación se muestra una imagen de la puerta Y que describiremos con Verilog.

Una puerta Y

Una puerta Y ¡Hagámoslo! Una unidad fundamental de Verilog se llama alambre. Por ahora, supongamos que un cable solo puede ser un 0 o un 1. Aquí hay una lógica de cable básica:

wire and_temp; assign and_temp = input_1 & input_2;

Estamos creando un cable llamado and_temp en la primera línea de código. En la segunda línea del código, tomamos el cable que creamos y asignamos el alambre. Para asignarlo, usamos la función booleana AND, que en Verilog es el símbolo Ampersand (&). Si tuviera que describir el código que se muestra arriba, podría decir:"La señal and_temp obtiene input_1 AND-ed con input_2."

Input_1 y Input_2 son entradas para esta pieza de Verilog Code. Vamos a mostrar la lista completa de entradas y salidas. Esto se hace en el módulo definición. Módulo es una palabra clave reservada en Verilog que muestra la creación de un bloque de código con entradas y salidas definidas.

module example_and_gate

(

input_1,

input_2,

and_result);

input input_1;

input input_2;

output and_result;

Este es su módulo básico. Define nuestro módulo llamado example_and_gate y 3 señales, 2 entradas y 1 salida. Pongamos todo junto para terminar el archivo. Lo único que nos falta es la asignación de la salida and_result . Otra nota, // en Verilog se usa para un comentario.

///////////////////////////////////////////////////////////////////////////////

// File Downloaded from http://www.nandland.com

///////////////////////////////////////////////////////////////////////////////

module example_and_gate

(

input_1,

input_2,

and_result);

input input_1;

input input_2;

output and_result;

wire and_temp;

assign and_temp = input_1 & input_2;

assign and_result = and_temp;

endmodule // example_and_gate

¡Felicidades! Ha creado su primer archivo Verilog.

¿Parece que tuviste que escribir mucho código solo para crear una puerta estúpida? En primer lugar, y las puertas no son estúpidas. En segundo lugar, tiene razón, los HDL requieren mucho código para realizar tareas relativamente simples. Puede consolarse un poco con el hecho de que Verilog es al menos menos detallado que VHDL. Acostúmbrese al hecho de que hacer algo que era muy fácil en el software le llevará mucho más tiempo en un HDL como Verilog o VHDL. ¡Pero solo pídale a algún tipo de software que intente generar una imagen en un monitor VGA que muestre el Juego de la vida de Conway y observe cómo su cabeza da vueltas con asombro! Por cierto, ese video se crea con un FPGA. ¡Podrás hacerlo muy pronto!

Verilog

- Tutorial de Verilog

- Concatenación Verilog

- Asignaciones de Verilog

- Bloqueo y no bloqueo de Verilog

- Funciones de Verilog

- Tarea Verilog

- Generador de reloj Verilog

- Funciones matemáticas de Verilog

- Formato de hora de Verilog

- Alcance de la escala de tiempo de Verilog

- Operaciones de E/S de archivos de Verilog