Control de impedancia en el diseño de PCB de circuito digital de alta velocidad

Las tecnologías de control de impedancia son bastante importantes en el diseño de circuitos digitales de alta velocidad en los que se deben adoptar métodos efectivos para garantizar el excelente rendimiento de las PCB de alta velocidad.

Cálculo de Impedancia y Control de Impedancia de Líneas de Transmisión de Circuitos de Alta Velocidad en PCB

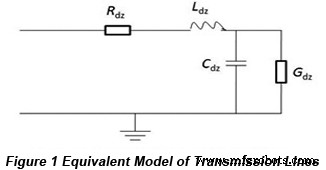

• Modelo Equivalente en Líneas de Transmisión

La Figura 1 muestra el efecto equivalente de las líneas de transmisión en las PCB, que es una estructura que incluye capacitores, resistencias e inductores en tándem y múltiples (modelo RLGC).

El valor típico de la resistencia en tándem está en el rango de 0,25 a 0,55 ohmios/pie y el valor de resistencia de múltiples resistencias suele permanecer bastante alto. Con la resistencia parásita, la capacitancia y la inductancia añadidas en las líneas de transmisión de PCB, la impedancia general en las líneas de transmisión se denomina impedancia característica (Z0 ). El valor de la impedancia característica es relativamente pequeño en la condición de que el diámetro de la línea sea grande, la línea esté cerca de la alimentación/tierra o la constante dieléctrica sea alta. La figura 3 muestra el modelo equivalente de la línea de transmisión con una longitud de dz, a partir del cual se puede deducir la impedancia característica de la línea de transmisión como fórmula: . En esta fórmula, L se refiere a la inductancia de cada unidad de longitud en la línea de transmisión, mientras que C se refiere a la capacitancia de cada unidad de longitud en la línea de transmisión.

. En esta fórmula, L se refiere a la inductancia de cada unidad de longitud en la línea de transmisión, mientras que C se refiere a la capacitancia de cada unidad de longitud en la línea de transmisión.

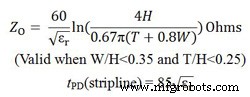

• Fórmula de cálculo de impedancia y retardo de líneas de transmisión en PCB

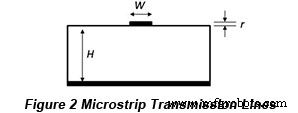

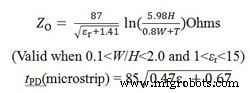

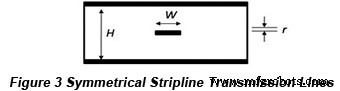

| Líneas de transmisión en PCB | Fórmula de cálculo de impedancia y retardo |

|  |

|  |

En las fórmulas anteriores, Z0 se refiere a la impedancia (ohmios), W se refiere al ancho de las líneas (pulgadas), T se refiere al grosor de las líneas (pulgadas), H se refiere a la distancia al suelo (pulgadas), se refiere a la constante dieléctrica relativa del sustrato, y tPD se refiere al tiempo de retardo (ps/pulgada).

• Reglas de diseño de control de impedancia de líneas de transmisión

Según el análisis anterior, el retardo unitario de la impedancia y la señal es independiente de la frecuencia de las señales, pero está relacionado con la estructura de la placa, la constante dieléctrica relativa del material de la placa y los atributos físicos del enrutamiento. Esta conclusión es extremadamente importante para comprender la PCB de alta velocidad y para el diseño de PCB de alta velocidad. Además, la velocidad de transmisión de la línea de transmisión de señal en la capa exterior es mucho más rápida que en la capa interior, por lo que estos elementos deben tenerse en cuenta para la disposición del diseño de las líneas clave.

El control de impedancia es la premisa importante para la implementación de la transmisión de señales. Sin embargo, de acuerdo con la estructura de la placa y la fórmula de cálculo de impedancia de las líneas de transmisión, la impedancia solo depende del material de PCB y la estructura de la capa de PCB con el ancho de línea y las características de enrutamiento sin cambios para la misma línea. Por lo tanto, la impedancia de una línea no cambiará en diferentes capas de PCB, lo que no está permitido en el diseño de circuitos de alta velocidad.

Para este artículo se ha diseñado una PCB de alta velocidad con alta densidad y la mayoría de las señales a bordo tienen requisitos de impedancia. Por ejemplo, la línea de señal CPCI debe tener una impedancia de 65 ohmios, una señal diferencial de 100 ohmios y otras señales de 50 ohmios cada una. De acuerdo con el espacio de enrutamiento de PCB, se debe usar un enrutamiento de al menos diez capas y se determina un plan de diseño de PCB de 16 capas.

Dado que el grosor total del tablero no puede exceder los 2 mm, existen algunas dificultades en términos de apilamiento con algunos problemas considerados:

1). Cada capa de señal tiene planos de imagen adyacentes para proteger la impedancia y la calidad de la señal.

2). Cada avión de potencia tiene una capa de tierra completa junto a ellos para que el rendimiento de la potencia esté bien garantizado.

3). El apilamiento de la tabla requiere equilibrio, evitando la deformación de la tabla.

La constante dieléctrica del medio se establece en 4,3. Según el diseño de apilamiento anterior, el ancho de línea y la distancia entre líneas deben establecerse de acuerdo con el resultado del cálculo para garantizar el requisito de impedancia de señal. El ancho de línea se obtiene como el siguiente resultado:

1). El ancho de la línea de señal en la capa superficial es de 5 milésimas de pulgada con una impedancia de 58,7 ohmios.

2). El ancho de la línea de señal CPCI en la capa superficial es de 4,5 mils con una impedancia de 61,7 ohmios.

3). El ancho de la línea de señal en la capa interna es de 4,5 mil con una impedancia de 50,2 ohmios.

4). El ancho de las líneas en el área BGA en la capa interna y la capa superficial es de 4 milésimas de pulgada con una impedancia de la capa superficial de 64,6 ohmios y una impedancia de la capa interna de 52,7 ohmios.

5). El ancho de la línea diferencial microstrip en la capa interna es de 5 mil con una distancia entre líneas de 6 mil y una impedancia de 100,54 ohmios.

6). El ancho de la línea diferencial de la línea de banda en la capa interna es de 4,5 milésimas de pulgada con una distancia entre líneas de 10 milésimas de pulgada y una impedancia de 96,6 ohmios.

La distancia entre líneas se establece de la siguiente manera:

1). La distancia entre las líneas de señal (5 milésimas de pulgada) en la capa superficial es de 5,0 milésimas de pulgada.

2). La distancia entre las líneas de señal de CPCI (4,5 mils) en la capa superficial es de 9,0 mils.

3).. La distancia entre las líneas de señal (4.5mils) en la capa interna es de 7.0mils.

4). La distancia entre las líneas de la capa superficial y la capa interna es de 4,0 mils.

5). La distancia entre las líneas de señal diferencial en la capa interna y entre ellas y otras líneas de señal debe mantenerse al menos en 25 mils.

6). La distancia entre las líneas de señal diferencial en la capa superficial y entre ellas y otras líneas de señal debe mantenerse al menos en 20 mils.

Después de la impresión de PCB, el probador de impedancia POLAR-Cits500 prueba la impedancia de la placa de prueba con los resultados en la siguiente tabla. Los datos indican que la impedancia debe controlarse en el rango de 50 ohmios, 60 ohmios y 100 ohmios en el proceso de diseño y fabricación de PCB de alta velocidad.

| Impedancia preestablecida (ohmios) | Impedancia práctica (ohmios) |

| 50 | 47,52-52,33 |

| 60 | 57,65-61,35 |

| 100 | 93,65-106,35 |

LVDS y su control de impedancia en PCB

• LVDS

LVDS es un tipo de nivel de transmisión de señal serial de alta velocidad con ventajas de alta velocidad de transmisión, bajo consumo de energía, fuerte capacidad antiinterferente, larga distancia de transmisión y coincidencia factible. Los campos de aplicación de LVDS incluyen informática, comunicación y consumo.

• Diseño de impedancia de LVDS

LVDS presenta una oscilación de voltaje de solo 350MV con la distancia de transmisión más larga de más de 10 metros. Para garantizar que las señales no se vean influenciadas por la señal reflejada en el proceso de transmisión de señales en las líneas de transmisión, la impedancia de las líneas de transmisión debe estar bajo control con una impedancia de línea única de 50 ohmios y una impedancia diferencial de 100 ohmios. En la aplicación práctica, la impedancia se puede controlar estableciendo un grosor de apilamiento razonable y parámetros medios, ajustando el ancho de línea y la distancia entre líneas y calculando la impedancia de líneas individuales y líneas diferenciales con la ayuda de algunas herramientas de análisis de simulación de alta velocidad.

Sin embargo, la mayoría de las veces, es relativamente difícil cumplir con los requisitos de impedancia de línea única e impedancia diferencial. Por un lado, el rango de ajuste del ancho de línea W y la distancia entre líneas S está controlado por el espacio de diseño físico. Por ejemplo, el enrutamiento y el ancho de línea en los conectores de margen con BGA o DIP están influenciados por el tamaño y la distancia del pad. Por otro lado, el cambio de W y S influirá en el resultado de la impedancia de línea única y diferencial. Hasta ahora, es fácil y conveniente averiguar la relación entre el ancho de línea preestablecido y la distancia de línea.

• Reglas de enrutamiento LVDS

En términos generales, el enrutamiento de señal diferencial se implementa de acuerdo con las reglas de diseño de impedancia, que es capaz de garantizar la calidad de LVDS. En el enrutamiento práctico, LVDS debe cumplir con las siguientes reglas:

1). Los pares diferenciales deben ser lo más cortos posible, las líneas deben ser rectas y el número de orificios pasantes debe reducirse. La distancia entre las líneas de señal en pares diferenciales debe ser la misma. Todas estas reglas contribuyen a evitar rutas largas y numerosos desvíos. En cuanto a los desvíos, se debe utilizar un desvío de 45 grados en lugar de 90 grados.

2). La distancia entre pares diferenciales debe mantenerse más de 10 veces para disminuir la diafonía entre líneas. Cuando sea necesario, se pueden colocar orificios pasantes a tierra entre pares diferenciales para el aislamiento.

3). LVDS no se puede dividir en la superficie. Aunque dos señales diferenciales son rutas de retorno mutuas, la ruta de retorno de la señal no se puede cortar como resultado de la división a lo largo de la superficie. Sin embargo, las líneas de transmisión posiblemente provocarán una discontinuidad de impedancia como resultado de la falta de planos de imagen.

4). Evite la señal diferencial entre capas. Durante la fabricación de PCB, la precisión de alineación de apilamiento entre capas es mucho menor que la precisión de grabado en la misma capa más la pérdida media durante el apilamiento, todo lo cual conduce al cambio de impedancia diferencial entre pares diferenciales.

5). En el diseño de impedancia, se debe utilizar el método de acoplamiento.

6). Se debe configurar una estructura de apilamiento de PCB adecuada para garantizar el aislamiento entre las señales de nivel de voltaje y LVDS. Cuando sea posible, las señales como TTL/CMOS de alta velocidad se pueden configurar en diferentes capas, aisladas del enrutamiento LVDS por capas de tierra y energía.

7). Los pares de señales diferenciales deben ser compatibles con la longitud del enrutamiento.

Recursos útiles

• Elementos que afectan la impedancia característica de PCB y soluciones

• Consideraciones de diseño de impedancia para PCB flexible-rígido

• Cómo analizar y prohibir la impedancia de la alimentación de PCB de alta velocidad

• Control de impedancia de vías y su influencia en la integridad de la señal en el diseño de PCB

• Servicio completo de fabricación de PCB de PCBCart:múltiples opciones de valor agregado

• Servicio avanzado de ensamblaje de PCB de PCBCart:comience desde 1 pieza

Tecnología Industrial

- Circuitos de control del motor

- Software de diseño de PCB

- Causas de la corrosión de PCB

- Consideraciones de diseño de PCB

- Consideraciones de diseño de impedancia para PCB rígido flexible

- Retrocesos y soluciones en el diseño de PCB RF

- 3 técnicas de enrutamiento en el diseño de circuito de señal de alta velocidad de PCB

- Sugerencias de diseño de alta velocidad

- Análisis de integridad de señal y diseño de PCB en circuito mixto digital-analógico de alta velocidad

- Desafíos del diseño de PCB de alta velocidad en la integridad de la señal y sus soluciones

- Control de impedancia de vías y su influencia en la integridad de la señal en el diseño de PCB