La GPU de código abierto se basa en RISC-V

Un grupo de entusiastas está proponiendo un nuevo conjunto de instrucciones gráficas diseñadas para gráficos 3D y procesamiento de medios. Estas nuevas instrucciones se basan en el conjunto de instrucciones de vector base RISC-V. Agregarán soporte para nuevos tipos de datos que son gráficos específicos como extensiones en capas en el espíritu de la arquitectura de conjunto de instrucciones (ISA) de RISC-V central. Se admiten vectores, matemáticas trascendentales, píxeles y texturas y operaciones de búfer Z / Frame. Puede ser un ISA CPU-GPU fusionado. El grupo lo llama RV64X, ya que las instrucciones tendrán una longitud de 64 bits (32 bits no serán suficientes para admitir un ISA robusto).

¿Por qué ahora?

El mundo tiene muchas GPU para elegir, ¿por qué esto? Porque, dice el grupo, las GPU comerciales son menos efectivas para satisfacer necesidades inusuales, como el recorte trifásico 3D de doble fase, HPC adaptable (FFT de profundidad de bits arbitraria), hardware SLAM. Creen que la colaboración proporciona estándares flexibles, reduce el esfuerzo de 10 a 20 años-hombre que de otro modo se necesitaría y ayudará con la verificación cruzada para evitar errores.

El equipo dice que su motivación y objetivos están impulsados por el deseo de crear un diseño pequeño y eficiente en áreas con programabilidad y extensibilidad personalizadas. Debe ofrecer propiedad y desarrollo de propiedad intelectual a bajo costo, y no competir con ofertas comerciales. Se puede implementar en objetivos FPGA y ASIC y será gratuito y de código abierto. El diseño inicial estará dirigido a microcontroladores de bajo consumo. Será compatible con Khronos Vulkan y, con el tiempo, admitirá otras API (OpenGL, DirectX y otras).

El hardware final será un núcleo RISC-V con una unidad funcional GPU. Para el programador, parecerá una sola pieza de hardware con instrucciones de 64 bits codificadas como instrucciones escalares. El modelo de programación es un SIMD aparente, es decir, el compilador genera SIMD a partir de códigos de operación escalares prefijados. Incluirá backend de SIMD predicado de problema variable, front-end de vector, excepciones precisas, sombreado de rama y mucho más. No habrá necesidad de que el mecanismo de llamada RPC / IPC envíe llamadas API 3D desde / hacia el espacio de memoria de la CPU no utilizado al espacio de memoria de la GPU y viceversa, dice el equipo. Y estará disponible como punto fijo de 16 bits (ideal para FPGA), así como como punto flotante de 32 bits (ASIC o FPGA).

El diseño empleará el formato Vblock (del esfuerzo de Libre GPU):

- Es un poco como VLIW (solo que no realmente)

- Un bloque de instrucciones está prefijado con etiquetas de registro que dan contexto adicional a las instrucciones escalares dentro del bloque

- Los sub-bloques incluyen:longitud de vector, swizzling, anulaciones de vector / ancho y predicación.

- Todo esto se agrega a los códigos de operación escalares

- No hay códigos de operación vectoriales (y no es necesario)

- En el contexto de vector, es así:si un código de operación escalar usa un registro y el registro está listado en el contexto de vector, el modo de vector está activado

- La activación da como resultado un bucle for a nivel de hardware que emite múltiples operaciones escalares contiguas (en lugar de solo una).

- Los implementadores son libres de implementar el ciclo de la forma que deseen:SIMD, múltiples problemas, ejecución única.

El diseño empleará escalares (fijos y flotantes de 8, 16, 24 y 32 bits), así como trascendentales (sincos, atan, pow, exp, log, rcp, rsq, sqrt, etc.). Los vectores (RV32-V) admitirán operaciones vectoriales de 2-4 elementos (8, 16 o 32 bits / elemento), junto con instrucciones especializadas para una canalización general de representación de gráficos 3D para puntos, píxeles, texels (esencialmente vectores especiales )

- Puntos XYZW (fijos y flotantes de 64 y 128 bits)

- Píxeles RGBA (píxeles de 8, 16, 24 y 32 bits)

- Téxels UVW (8, 16 bits por componente)

- Luces y materiales (Ia, ka, Id, kd, Is, ks ...)

Las matrices serán 2 × 2, 3 × 3 y las matrices 4 × 4 se admitirán como un tipo de datos nativo junto con estructuras de memoria para admitirlas para los vectores de atributos y estarán esencialmente representadas en una matriz de 4 × 4.

Entre las ventajas de ISA CPU-GPU fusionada se encuentra la capacidad de implementar una canalización de gráficos estándar en microcódigo, brindar soporte para sombreadores personalizados e implementar extensiones de trazado de rayos. También admite vectores para simulaciones numéricas con tipos de datos enteros de 8 bits para inteligencia artificial y aprendizaje automático.

Se pueden implementar rasterizadores personalizados como splines, superficies SubDiv y parches.

El diseño será lo suficientemente flexible como para poder implementar etapas de canalización personalizadas, etapas de búfer de geometría / píxel / fotogramas personalizadas, teseladores personalizados y operaciones de creación de instancias personalizadas.

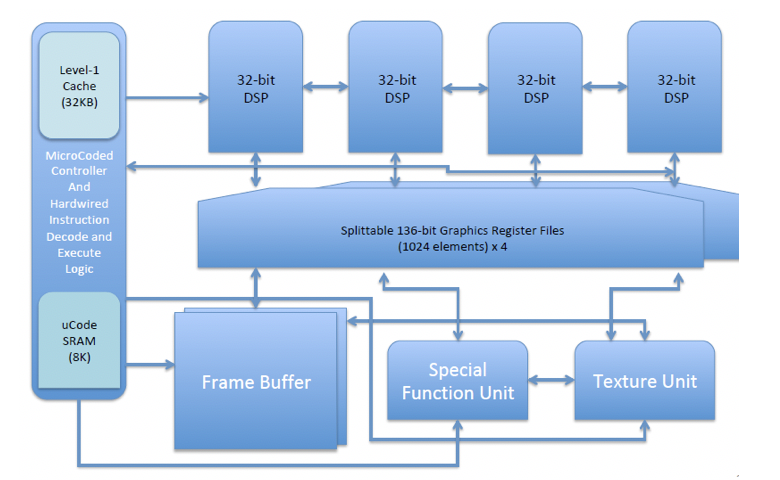

Diagrama de bloques RV64X

La implementación de referencia RV64X incluirá:

- Caché SRAM de instrucciones / datos (32 KB)

- Microcódigo SRAM (8 KB)

- Decodificador de instrucciones de función dual

- Implementación cableada de RV32V y X

- Decodificador de instrucciones microcodificado para ISA personalizado

- Quad Vector ALU (32 bits / ALU:fijo / flotante)

- Archivos de registro de 136 bits (elementos de 1K)

- Unidad de función especial

- Unidad de textura

- Búfer de tramas local configurable

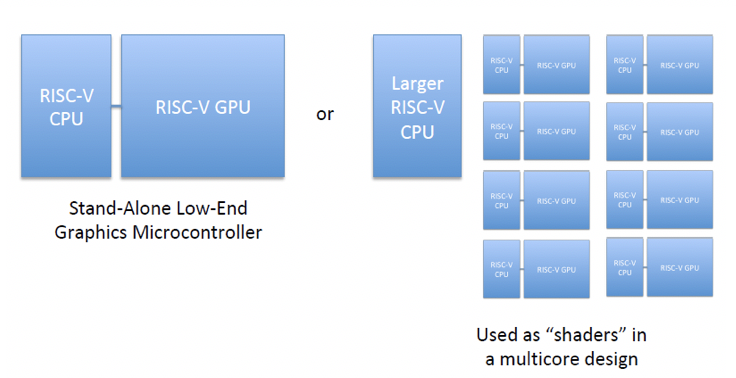

El diseño está destinado a ser escalable como se indica a continuación.

Diseño escalable de RV64X

El diseño RV64X tiene varias ideas novedosas que incluyen CPU-GPU ISA unificada fusionada, registros configurables para tipos de datos personalizados y microcódigo basado en SRAM definido por el usuario para extensiones de hardware personalizadas definidas por la aplicación para:

- Etapas de rasterizador personalizadas

- Trazado de rayos

- Aprendizaje automático

- Visión por computadora

El mismo diseño sirve tanto como un microcontrolador de gráficos independiente o como una unidad de sombreado escalable, y los formatos de datos admiten implementaciones nativas de FPGA o ASIC.

¿Por qué se necesitan gráficos abiertos?

Los desarrolladores piensan que la mayoría de los procesadores de gráficos cubren la gama alta, como los juegos, el comercio de alta frecuencia, la visión por computadora y el aprendizaje automático. Creen que el ecosistema carece de un núcleo gráfico escalable para aplicaciones más convencionales para cosas como quioscos, vallas publicitarias, juegos de casino, juguetes, robótica, electrodomésticos, dispositivos portátiles, interfaces industriales hombre-máquina, infoentretenimiento y grupos de indicadores automotrices. Mientras tanto, se deben usar lenguajes de programación especializados para programar núcleos de GPU para OpenGL, OpenCL, CUDA, DirectCompute y DirectX.

Una extensión de gráficos para RISC-V resolvería la escalabilidad y las cargas multilingües permitiendo un mayor nivel de innovación de casos de uso.

Pasos siguientes

Esta es una especificación muy temprana, aún en desarrollo y sujeta a cambios en función de los aportes de las partes interesadas y de la industria. El equipo establecerá un foro de discusión. Un objetivo inmediato es construir una implementación de muestra con un simulador de conjunto de instrucciones, una implementación de FPGA utilizando IP de código abierto e IP personalizado diseñado como proyecto de código abierto. Se están diseñando demostraciones y evaluaciones comparativas. Los desarrolladores interesados en participar deben contratar a Atif Zafar.

En cuanto a la GPU Libre-RISC 3D, el objetivo de la organización es diseñar una CPU, VPU y GPU híbridas. No es, como se informó ampliamente, una "GPU exclusiva dedicada". Existe la opción de crear un producto de GPU independiente. Su objetivo principal es diseñar un SoC de procesador todo en uno completo que incluya una VPU y una GPU con licencia Libre.

¿Qué pensamos?

La población de proveedores de GPU está aumentando. Ahora tenemos más de una docena.

AppleLibre-RISC-V 3D GPUQualcommAMDNvidiaRISC-V GraphicsArmIntelThink-SiliconDMPJingjia MicroVeriSilcionImagination TechnologiesUna aplicación que no figura como usuario potencial de una GPU pequeña, flexible y gratuita incluye la criptomoneda y la minería.

Si el objetivo de la comunidad RISC-V es emular a los proveedores de IP como Arm e Imagination, entonces podemos esperar ver diseños de DSP, ISP y DP. Hay al menos una propuesta de Open DSP; tal vez se pueda incorporar a la comunidad RISC-V.

Pasarán al menos dos años antes de que surjan implementaciones de hardware. Uno de los candidatos más lógicos para adoptar este diseño es Xilinx, que ahora usa Arm's Mali en su diseño Zynq. También esperaríamos ver varias implementaciones en China.

>> Este artículo se publicó originalmente el nuestro sitio hermano, EE Times.

Jon Peddie , pionero en la industria gráfica, es presidente de Jon Peddie Research.

Jon Peddie , pionero en la industria gráfica, es presidente de Jon Peddie Research. Para obtener más información sobre Embedded, suscríbase al boletín informativo semanal por correo electrónico de Embedded.

Incrustado

- Introducción a la terminología de código abierto

- El código abierto y el IoT:innovación mediante la colaboración

- Cumbre RISC-V:aspectos destacados de la agenda

- La seguridad de IoT industrial se basa en hardware

- Un registro de proyecto para FirePick Delta, la MicroFactory de código abierto

- AT&T y Tech Mahindra colaboran en una nueva plataforma de inteligencia artificial de código abierto

- Riesgos de software:protección de código abierto en IoT

- Herramientas de desarrollo de IoT de código abierto frente a herramientas compatibles con el proveedor

- MassRobotics publica los primeros estándares de interoperabilidad de robots móviles autónomos de código abierto del mundo

- La necesidad del código abierto en el perímetro (eBook)

- El código abierto impulsa la adopción de IoT y Edge Computing