Determinismo de la fase de encendido:sintetizador PLL y calibración a nivel del sistema

En la primera parte de esta serie de artículos, exploramos cómo lograr fases conocidas (deterministas) para todos los canales dentro de chips integrados con múltiples bloques de procesamiento de señales digitales (DSP), convertidores de digital a analógico (DAC) de banda ancha y analógicos de banda ancha. -convertidores digitales (ADC). Comenzamos con un diagrama de bloques del sistema de alto nivel que emplea una estructura de árbol de reloj de subarreglo y describimos un método de sincronización de múltiples chips. En esta segunda parte, exploraremos los ajustes de fase del sintetizador PLL, la escalabilidad a múltiples subarreglos y los algoritmos de calibración a nivel del sistema.

Ajustes de fase del sintetizador PLL

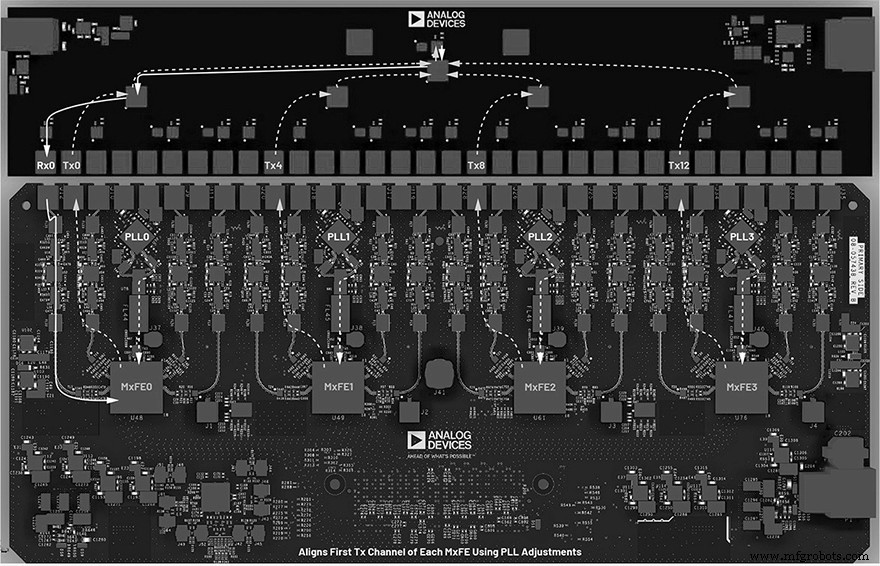

Los circuitos integrados de sintetizador PLL elegidos se han seleccionado para permitir ajustes relativos de la fase del reloj de muestra inyectados en cada circuito integrado digitalizador. La deriva térmica, y la deriva de fase PLL resultante entre el reloj de muestra y el SYSREF de cada IC, se compensa mediante la creación de un mecanismo de retroalimentación que asegura que el primer canal de transmisión de cada IC digitalizador esté alineado en fase con el primer canal de transmisión del IC digitalizador. Para lograr este bucle de retroalimentación, el primer canal de transmisión de cada IC emite una señal que se diferencia de los otros canales de transmisión, como se muestra en la Figura 1. Estas cuatro señales se combinan y envían a un receptor común, que para este sistema se etiqueta como Rx0 .

haz clic para ver la imagen a tamaño completo

Figura 1. La función de ajuste de fase del sintetizador PLL permite alinear el primer canal de transmisión de cada circuito integrado digitalizador a través del subarreglo. (Fuente:Analog Devices)

Se obtienen datos de recepción simultáneos para todos los canales de recepción, lo que luego permite a los usuarios aplicar técnicas de correlación cruzada y determinar las complejas desviaciones de fase entre estos cuatro canales de transmisión, Φ TxOffset . Los circuitos integrados del sintetizador PLL contienen dentro de ellos un oscilador controlado por voltaje (VCO) que está operando a una frecuencia ƒ VCO_PLL .

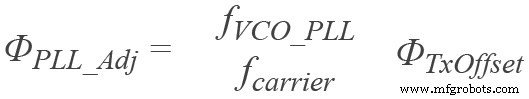

Las compensaciones de fase medidas Φ TxOffset luego se relacionan con el ajuste de fase PLL requerido Φ PLL_Adj y la frecuencia de RF ƒ transportista tal que:

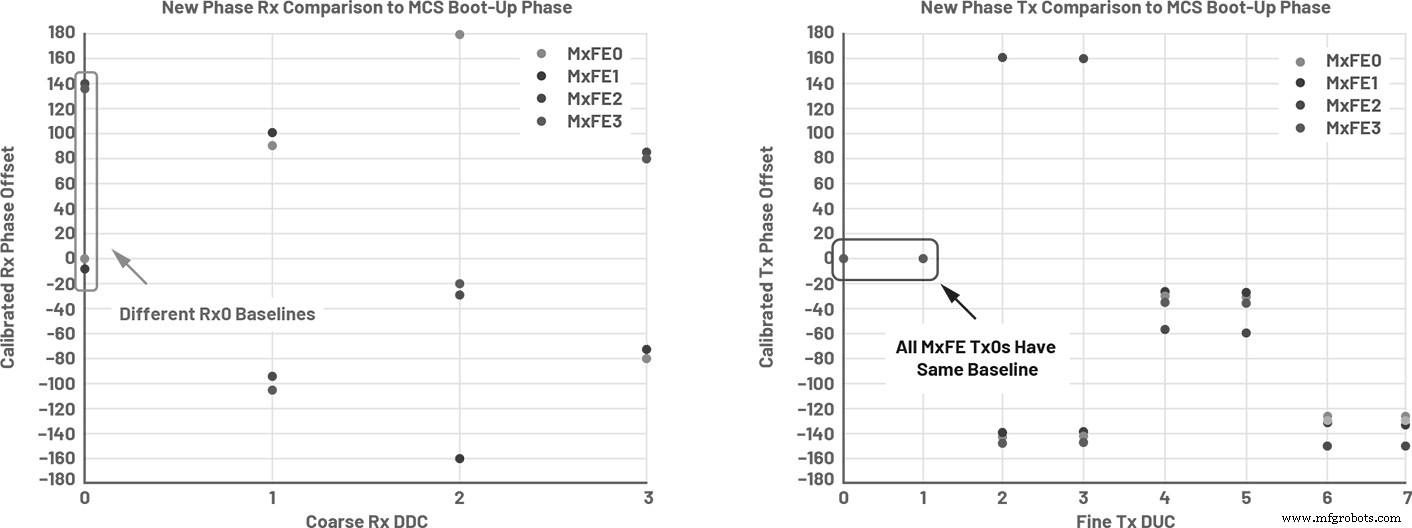

Con esta fórmula, las fases del sintetizador PLL se pueden ajustar por una nueva cantidad conocida para establecer una línea base de transmisión común entre todos los circuitos integrados del digitalizador para todos los ciclos de energía, como se muestra en la Figura 2. Los círculos abiertos para cada canal que se muestran en la Figura 2 corresponden a la primer ciclo de encendido, mientras que todos los demás puntos sólidos corresponden a ciclos de encendido posteriores. Como puede verse en esta figura, las desviaciones de fase de transmisión calibradas para el primer (y segundo) canalizador de todos los circuitos integrados de digitalizador están alineadas en fase. El segundo canalizador de cada circuito integrado digitalizador también está alineado en esta instancia, porque se utilizan dos canalizadores para cada DAC en el sistema.

Agregar este paso de ajuste de fase del sintetizador PLL antes de las rutinas MCS discutidas en la sección anterior crea una fase determinista en todos los gradientes térmicos inducidos dentro del sistema al forzar el sistema a la misma relación de fase de reloj de muestra-SYSREF, que se manifiesta como una transmisión línea de base de alineación en todos los circuitos integrados del digitalizador.

haz clic para ver la imagen en tamaño completo

Figura 2. Al ajustar la fase PLL, el usuario puede alinear el primer canal de transmisión de todos los circuitos integrados del digitalizador. (Fuente:Analog Devices)

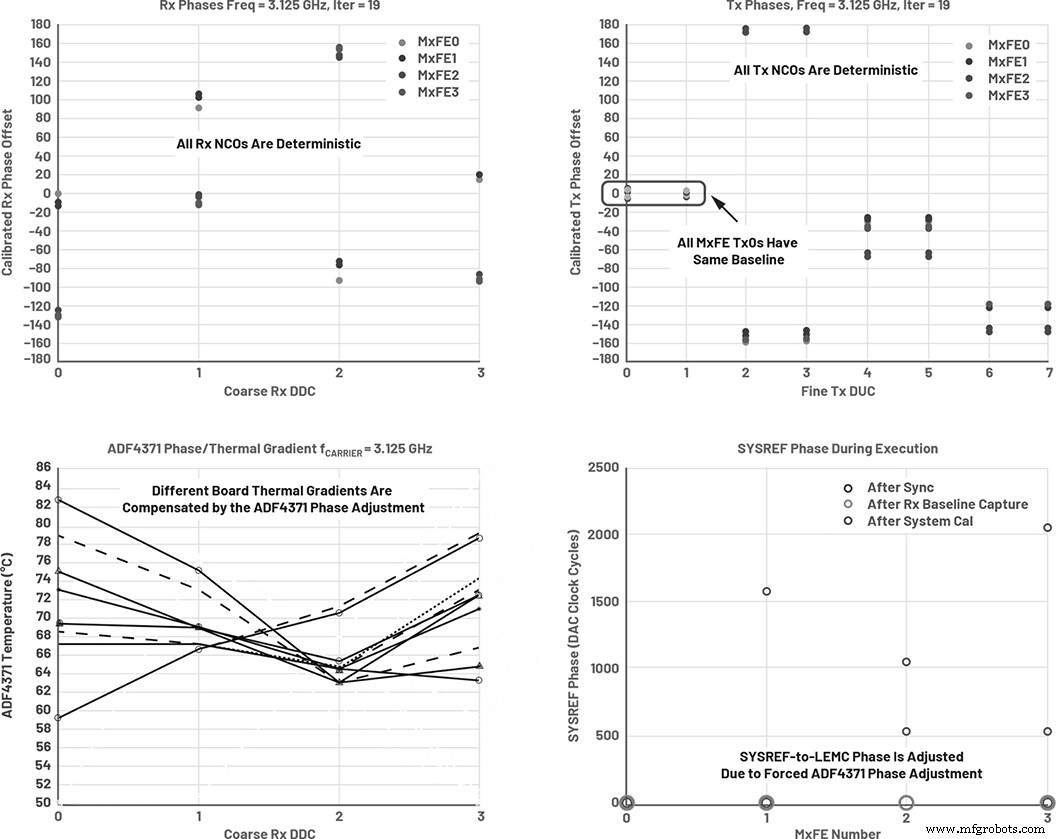

La Figura 3 muestra que se puede detectar un gradiente térmico inducido mediante la unidad de medición de temperatura (TMU) en cada chip sintetizador PLL. Como se puede ver en el trazo azul en la parte inferior izquierda de la Figura 3, se han inducido intencionalmente temperaturas muy variables en la plataforma mediante la aplicación de diferentes flujos de aire de ventilador al sistema. Sin embargo, el uso del ajuste de fase PLL para cada IC demuestra que, independientemente del flujo de aire aplicado a la placa, las compensaciones de fase NCO calibradas para cada canal de recepción y transmisión son deterministas al forzar al primer canalizador de transmisión de cada IC digitalizador a alinearse con cada uno. otro. Esto se revela al observar el grupo apretado del mismo color de puntos en los dos gráficos superiores en la Figura 3 a pesar de los diferentes gradientes térmicos aplicados a la placa durante diferentes ciclos de energía.

haz clic para ver la imagen a tamaño completo

Figura 3. La función MCS utilizada junto con la función de ajuste de fase PLL demuestra el determinismo de la fase de encendido para todos los canales de recepción y transmisión, independientemente del gradiente térmico inducido en la plataforma. (Fuente:Analog Devices)

En la parte inferior derecha de la Figura 3 se muestran los registros IC del digitalizador sondeados, que muestran la relación de fase SYSREF-LEMC medida después de aplicar el desplazamiento de fase del sintetizador PLL. Observe a partir de las trazas naranjas en la gráfica inferior izquierda que los ajustes de fase del sintetizador PLL compensan completamente cualquier fase SYSREF distinta de cero medida que resulte de un gradiente térmico inducido diferente.

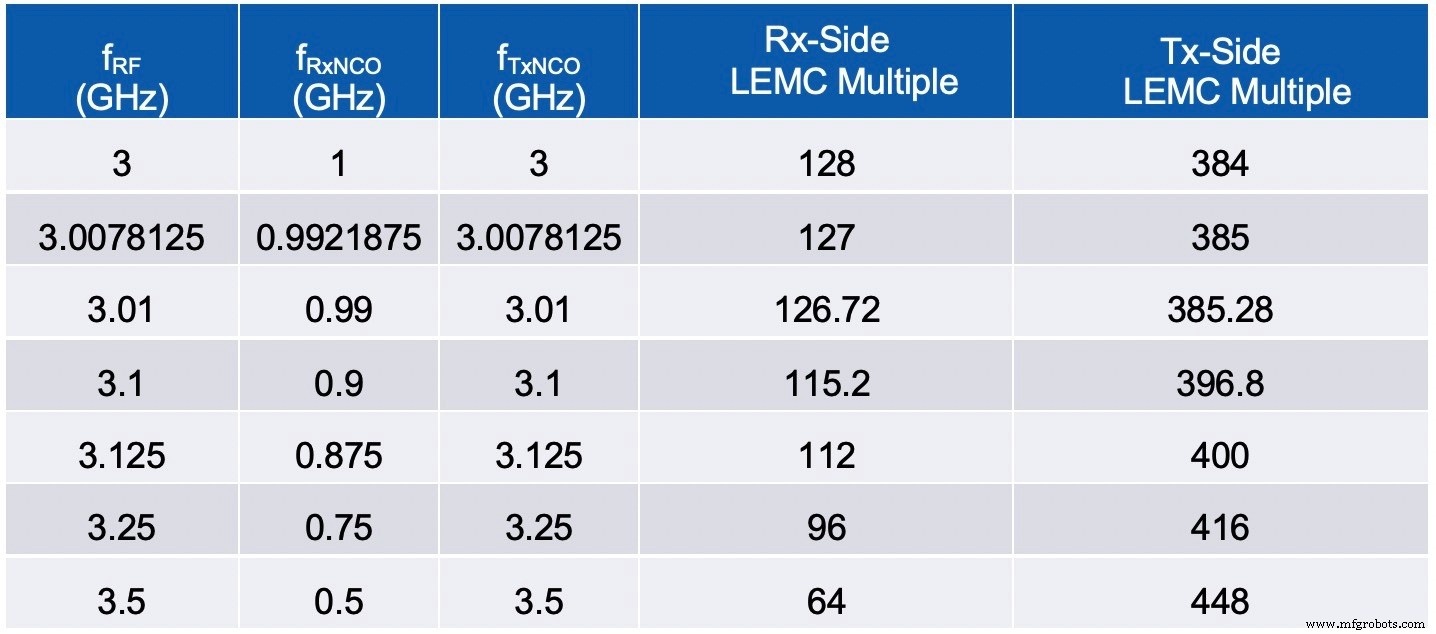

Se han medido muchas frecuencias, todas las cuales demuestran una fase de transmisión y recepción determinista. Las frecuencias específicas elegidas para este artículo se muestran en la Figura 4, y fueron elegidas de manera que MCS se demuestre sobre muchos gradientes térmicos inducidos cuando se utilizan múltiplos no enteros del reloj de referencia o LEMC.

Figura 4. Las frecuencias de RF utilizadas en este artículo se eligen para demostrar las funciones de MCS en una amplia gama de fuentes de reloj, incluidos los múltiplos no enteros del reloj de referencia y LEMC. (Fuente:Analog Devices)

Escalabilidad a múltiples submatrices

Los datos que se muestran en este artículo se centran principalmente en el rendimiento de MCS en el nivel de subarreglo, pero también es necesario garantizar que estas características de sincronización se puedan realizar en el nivel de arreglo más grande y en varios subarreglos. Para lograr este nivel más alto de sincronización, se requiere un árbol de reloj a nivel de arreglo para asegurar que las solicitudes SYSREF a cada subarreglo que se muestra en la Figura 1 en la Parte 1 lleguen sincrónicamente al CI de búfer de reloj de cada subarreglo. Luego, dado este criterio, cada subarreglo puede emitir los relojes SYSREF y BBP requeridos, como se describió anteriormente, de modo que estas señales lleguen a los circuitos integrados del digitalizador del subarreglo y al BBP dentro del mismo ciclo de reloj de muestra a través del arreglo más grande. Este árbol de reloj a nivel de matriz requiere que la distribución de reloj a cada submatriz posea los bloques de ajuste de retardo necesarios para lograr la distribución de solicitudes SYSREF síncrona a cada uno de los circuitos integrados de chip de reloj de subarreglo descendente. De esta manera, múltiples BBP conectados a múltiples subarreglos se sincronizan en última instancia.

Algoritmo de calibración a nivel del sistema

Si bien los algoritmos MCS que se muestran en las secciones anteriores proporcionan una fase determinista de encendido para cada canal de recepción y transmisión, estas fases no están necesariamente alineadas en fase en todos los canales dentro del dominio de RF debido a las diferencias en las longitudes de traza del front-end de RF a través de los canales. . Por lo tanto, aunque los algoritmos MCS sí simplifican el proceso de calibración de la matriz, todavía existe la necesidad de someterse a una rutina de calibración a nivel del sistema para alinear las fases de cada canal de RF dentro del sistema.

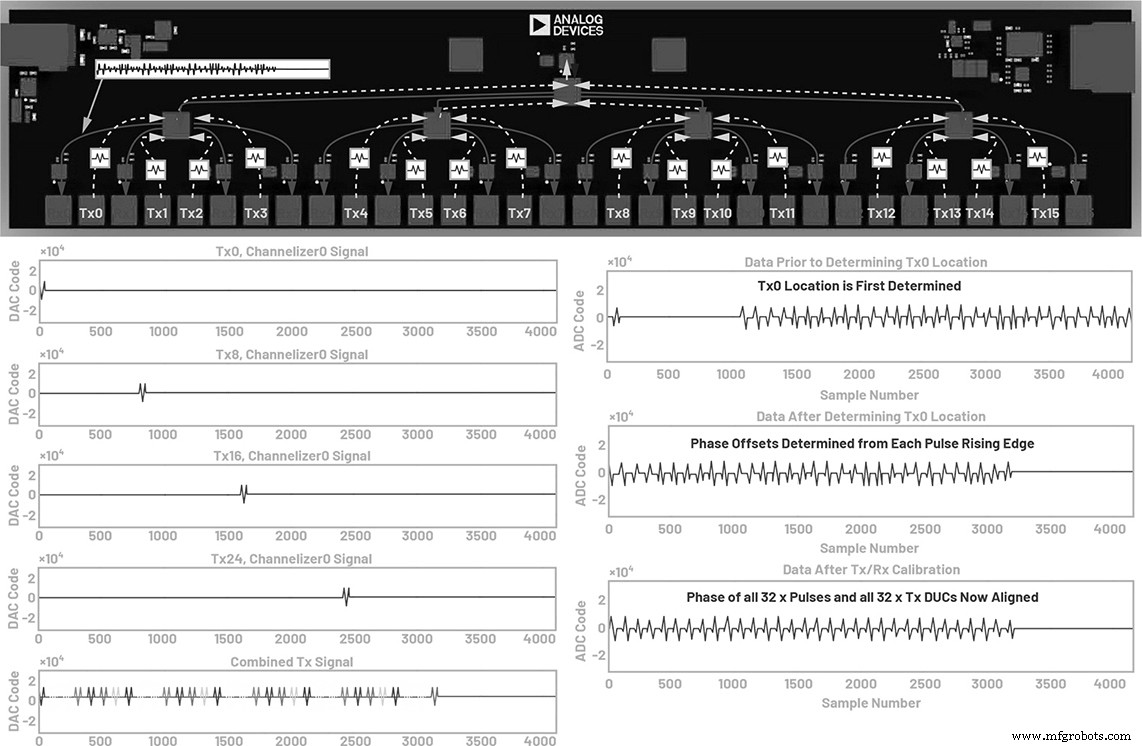

Por lo tanto, es necesario desarrollar un algoritmo de calibración a nivel de sistema eficiente además de realizar los algoritmos MCS. El método de calibración a nivel del sistema para este artículo utiliza una forma de onda de banda base específica y es completamente autónomo sin la necesidad de ningún equipo externo. El sistema descrito en este artículo es capaz de inyectar formas de onda de banda base separadas en cada canalizador de la plataforma. Utilizando esta capacidad, una forma de onda de banda base que consiste en un pulso de un período para cada canalizador de transmisión se inyecta en el subarreglo, como se muestra en la parte inferior izquierda de la Figura 5. Por lo tanto, cada canalizador de transmisión genera solo un pulso. Sin embargo, las formas de onda están escalonadas en todos los canalizadores de transmisión de modo que solo se emite un pulso de un período a la vez en todo el sistema. La salida de todos los canalizadores de transmisión se combina dentro del dominio de RF y luego se divide y se envía de vuelta a todos los canales de recepción, como se muestra en la parte superior de la Figura 5. Finalmente, se realiza una captura de datos de recepción simultánea para todos los canales de recepción y se guardan los datos. a una matriz de 4096 × 16, donde 4096 es el tamaño de muestra recopilado para los 16 canales de recepción.

haz clic para ver la imagen a tamaño completo

Figura 5. Se utiliza un algoritmo de calibración a nivel de sistema junto con MCS para lograr rápidamente la alineación de todos los canales de recepción y transmisión en el sistema. (Fuente:Analog Devices)

Luego, estos datos se analizan verticalmente a lo largo de la primera columna (correspondiente a Rx0) para ubicar el pulso del canalizador Tx0, como se muestra en la subparcela superior en la parte inferior derecha de la Figura 5. Después de identificar el pulso Tx0, se conocen todas las demás ubicaciones de pulsos. y la fase compleja del flanco ascendente de cada pulso se calcula y se guarda en un vector de 1 × 16 que corresponde a los desfases de fase medidos presentes en todos los canales de transmisión en todo el sistema. Con este conocimiento, y utilizando Tx0 como referencia de línea base, las fases complejas de todos los canales de transmisión se modifican en función de las compensaciones medidas.

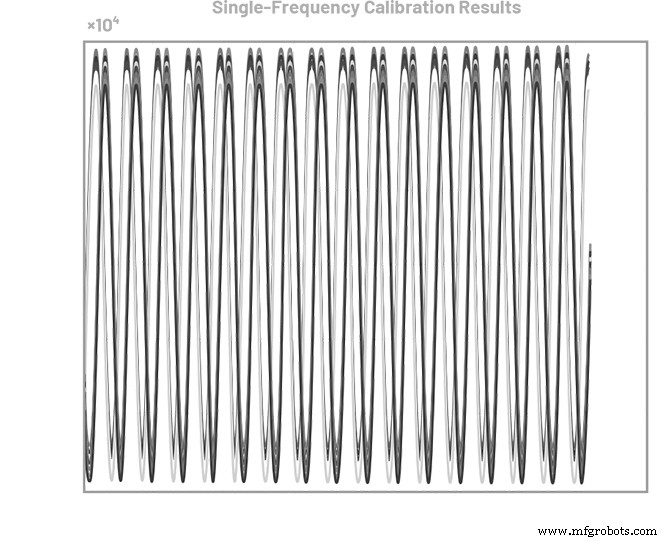

De manera similar, dado que se envía la misma señal combinada a todos los canales de recepción, los datos se analizan horizontalmente a lo largo de la matriz (mirando a través de todos los canales de recepción). Las fases complejas de todos los canales de recepción se miden entonces con respecto a Rx0 y se guardan en un vector de 1 × 16 correspondiente a los desfases de fase de recepción medidos presentes en el sistema. Las fases del complejo NCO de recepción se ajustan luego en todo el subconjunto para alinear en fase todos los canales con respecto a Rx0, como se muestra en los códigos ADC en fase (I) y en cuadratura (Q) para los 16 canales de recepción en la Figura 6. Puede observarse que, si bien el gráfico de la fase de la Figura 6 alinea todos los canales, no necesariamente alinea en amplitud todos los canales. Sin embargo, al usar los filtros de respuesta de impulso finito (FIR) en el chip que ahora están presentes en estos circuitos integrados de digitalizador, se podría alternativamente lograr la alineación de amplitud y fase a través de los canales sin la necesidad de asignar recursos FPGA que consumen mucha energía para lograr el mismo resultado.

haga clic para ver la imagen a tamaño completo

Figura 6. La alineación de fase I&Q de recepción de 16 canales se logra con la ayuda de MCS y un algoritmo de calibración de nivel de sistema autónomo. (Fuente:Analog Devices)

Este algoritmo de calibración a nivel del sistema se logra actualmente en MATLAB ® y tarda aproximadamente tres segundos en completarse. Sin embargo, si se implementa en lenguaje de descripción de hardware (HDL), este tiempo de calibración puede reducirse aún más mientras se mantiene un algoritmo completamente autónomo. Además, al confiar en los algoritmos MCS, si la frecuencia y amplitud del sistema se conocen en el arranque, los usuarios pueden cargar valores de desfase de una tabla de búsqueda en lugar de tener que someterse a las mediciones descritas en este método de calibración a nivel del sistema. En este caso, el método de calibración a nivel del sistema se puede utilizar para completar los desfases de fase guardados en una tabla de búsqueda durante una calibración de fábrica.

Conclusión

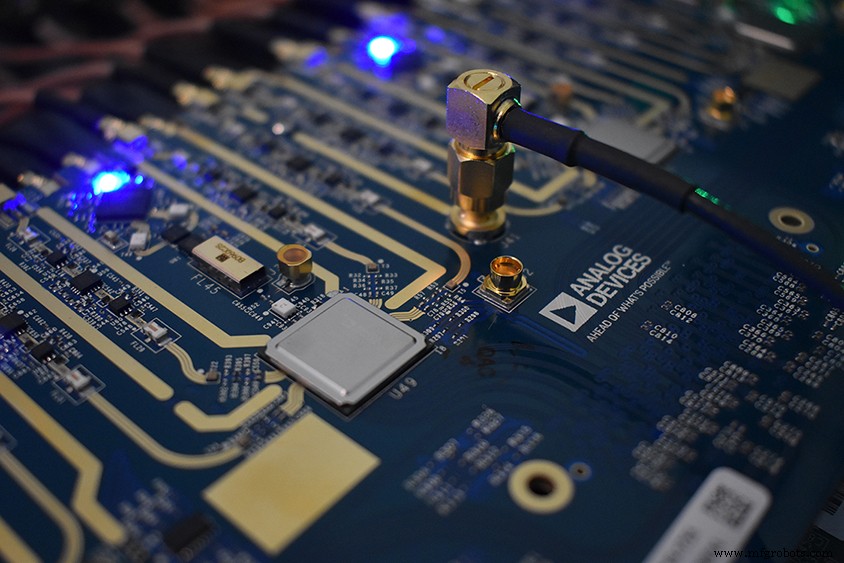

Se ha demostrado un proceso MCS exitoso utilizando cuatro circuitos integrados AD9081 MxFETM de Analog Devices como la columna vertebral del subarreglo. Los gradientes térmicos en la plataforma se compensan con la ayuda de bloques de ajuste de fase dentro de cuatro sintetizadores PLL ADF4371. Se utiliza un IC de reloj HMC7043 para distribuir los relojes SYSREF y BBP necesarios para la interfaz JESD204C. Los algoritmos MCS dentro del AD9081 permiten calibraciones simplificadas a nivel del sistema y proporcionan una fase determinista de encendido para múltiples frecuencias y gradientes térmicos presentes en el sistema. También se presenta un algoritmo de calibración a nivel de sistema eficiente que se utiliza para completar las LUT durante la calibración de fábrica y, por lo tanto, reduce drásticamente el tiempo de arranque del sistema. Esta plataforma se muestra en la Figura 7 y se llama Quad-MxFE. El sistema está disponible para su compra en Analog Devices. Este trabajo es pertinente para cualquier sistema multicanal presente en cualquier radar de matriz en fase, guerra electrónica, instrumentación o plataforma 5G.

Figura 7. La plataforma Quad-MxFE está disponible para su compra en Analog Devices. (Fuente:Analog Devices)

Referencias

1 Del Jones. "Manual JESD204C:Novedades y ventajas:Parte 1". Diálogo analógico , Vol. 53, No. 2, junio de 2019.

2 Del Jones. "Manual JESD204C:Novedades y ventajas para usted:Parte 2". Diálogo analógico , Vol. 53, No. 3, julio de 2019.

Incrustado

- 3 razones por las que DevOps y la nube se necesitan mutuamente; DevCloudOps

- Vectores y formas de onda de CA

- Medición de frecuencia y fase

- ¿Qué es la calibración del sensor? Definición y su aplicación

- Estructuras y clases en C ++

- Buzones de correo:introducción y servicios básicos

- Semáforos:introducción y servicios básicos

- Colas:introducción y servicios básicos

- Próxima fase de ventas al por menor de vídeo inmersivo, inteligencia artificial y modelado tecnológico

- El torneado duro y el rectificado cilíndrico se hicieron el uno para el otro

- Tipos comunes de fresadoras y cuándo usar cada una