Introducción al lenguaje de descripción de hardware Verilog

En este artículo, estudiaremos la estructura básica de un módulo Verilog, veremos algunos ejemplos del uso del tipo de datos Verilog "wire" y su forma vectorial y mencione brevemente algunas diferencias entre VHDL y Verilog.

En este artículo, estudiaremos la estructura básica de un módulo Verilog, veremos algunos ejemplos del uso del tipo de datos "cable" de Verilog y su forma vectorial, y abordaremos brevemente algunas diferencias entre VHDL y Verilog.

Verilog y VHDL son dos lenguajes que se utilizan comúnmente para describir circuitos digitales. AAC tiene una serie de artículos técnicos que discuten los conceptos básicos de VHDL. Este artículo funciona como un punto de partida para nuestra serie sobre Verilog.

¿Necesito tanto Verilog como VHDL?

Antes de comenzar nuestra discusión, abordemos una pregunta obvia:¿realmente necesitamos conocer estos dos idiomas?

Tanto Verilog como VHDL son herramientas poderosas que se pueden utilizar para diseñar un circuito digital complejo. Aunque existen algunas diferencias entre estos dos HDL, puede elegir cualquiera para dominar y usar. Sin embargo, creo que en algún momento, se beneficiará de tener al menos un conocimiento básico de ambos idiomas. A veces, como diseñadores, necesitamos un segmento de código de muestra para tener una idea sobre la codificación de un proyecto. Navegamos por la red durante horas y finalmente encontramos lo que necesitamos, pero no tiene sentido para nosotros; está escrito en HDL que es completamente desconocido para nosotros. Sin tener una comprensión básica del idioma, es posible que no podamos comprender completamente las técnicas.

Verilog Evolution

Verilog fue diseñado a principios de 1984 por Gateway Design Automation (aproximadamente tres años después de que el Departamento de Defensa de EE. UU. Iniciara VHDL). Con el apoyo del DoD, VHDL se convirtió en un estándar IEEE en 1987. Verilog no apareció en escena hasta 1995. Hoy en día, tanto VHDL como Verilog son HDL populares y las herramientas de diseño FPGA generalmente admiten ambos idiomas.

La palabra "Verilog" es un acrónimo de las palabras "verificación" y "lógica" porque el lenguaje se sugirió por primera vez como una herramienta de simulación y verificación. Comencemos con los conceptos y la sintaxis de Verilog.

Ejemplo 1

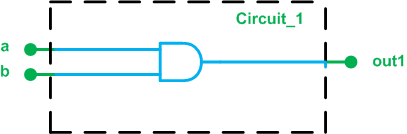

Como primer ejemplo, escribamos el código Verilog para el circuito que se muestra en la Figura 1.

Figura 1. Circuit_1

Hay dos entradas y una salida. Los puertos son todos de un poco de ancho. La funcionalidad del circuito es hacer Y las dos entradas y poner el resultado en el puerto out1.

Una posible descripción de Verilog para el módulo Circuit_1 es:

Líneas 1 y 8

Estas dos líneas usan las palabras clave "módulo" y "endmodule" para especificar que las líneas intermedias (líneas 2 a 7) describen un circuito llamado "Circuito_1". Este nombre es arbitrario y nos permite hacer referencia a este circuito más adelante.

Líneas 2 a 6

Estas líneas especifican la interfaz de "Circuit_1" con su entorno circundante. Los puertos de entrada y salida se describen utilizando las palabras clave "entrada" y "salida". Estas palabras clave van seguidas de otra palabra clave "cable" y luego el nombre del puerto (consulte la Figura 1). ¿Qué especifica la palabra clave "cable"? "Cable" es un tipo de datos de Verilog que representa un cable físico en el diseño. Discutiremos los tipos de datos de Verilog con mayor detalle en un artículo futuro, pero por ahora, sabemos que habría tres cables llamados a, by out1 en nuestro módulo y, dado que estos se especifican en la declaración del puerto, corresponden a la interfaz del módulo.

Línea 7

Esta línea utiliza el operador AND bit a bit, es decir, &, para describir la funcionalidad del circuito. La palabra clave "asignar" pone a &b en el puerto de salida out1. Este tipo de asignación se denomina asignación continua. Se llama así porque la asignación siempre está activa cada vez que cambia un operando en el lado derecho, a &b se evalúa y se asigna a out1. Podemos imaginar una asignación continua como un circuito combinacional cuya salida se actualiza continuamente en función de sus entradas. En nuestro ejemplo, este circuito combinacional es una puerta AND simple. También hay asignaciones de procedimientos en Verilog HDL que se discutirán en artículos futuros.

Ahora, podemos usar un paquete de software como Xilinx ISE para verificar el código anterior. Puede encontrar un tutorial basado en Verilog de este software aquí (PDF).

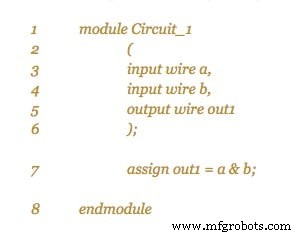

Comparación del ejemplo 1 con el código VHDL

La Figura 2 a continuación muestra las descripciones de Verilog y VHDL para el módulo Circuit_1.

Figura 2. Comparación de las descripciones de Verilog y VHDL para Circuit_1.

Como puede ver, tenemos que incluir algunas bibliotecas al codificar en VHDL. Estas bibliotecas dan la definición de los tipos de datos y los operadores. Considerando la adición de estas bibliotecas y el formato general de VHDL, observamos que el código VHDL es más detallado. Sin embargo, esta verbosidad no está exenta de ventajas. Por ejemplo, la función de administración de bibliotecas de VHDL puede resultar útil al modelar sistemas de nivel superior. En artículos futuros, discutiremos ocasionalmente los pros y los contras de estos dos HDL.

Verilog tiene un sistema de cuatro valores

Hay cuatro valores básicos que se utilizan en la mayoría de los tipos de datos de Verilog. Los cables definidos en el Listado 1 pueden adoptar uno de los siguientes valores:

- 0:para una condición lógica baja o falsa

- 1:para una condición lógica alta o verdadera

- z:para el estado de alta impedancia (se puede usar para describir la salida de un búfer de tres estados)

- x:para un valor desconocido o indiferente (cuando una entrada no se inicializa o dos o más salidas en conflicto están conectadas juntas).

El tipo de datos VHDL std_logic puede tomar nueve valores diferentes, pero sus valores de uso común son "0", "1", "Z" y "-" ("-" denota un indiferente).

Ejemplo 2

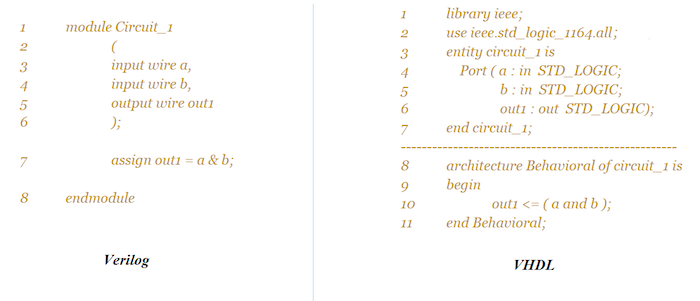

Como otro ejemplo, escribamos el código Verilog para el circuito (que etiquetaremos como Circuito_2) que se muestra en la Figura 3.

Figura 3. Circuito_2

El siguiente código de Verilog describe este circuito:

Los elementos usados en el código anterior son similares a los del Ejemplo 1, excepto que se define una señal interna en la línea 10 del código. La palabra clave "cable" se utiliza para especificar el tipo de datos de esta conexión. Como se mencionó anteriormente, el tipo de datos "cable" se traduciría en un cable físico en el diseño.

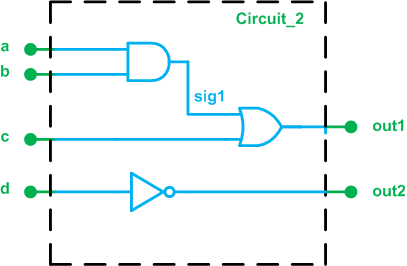

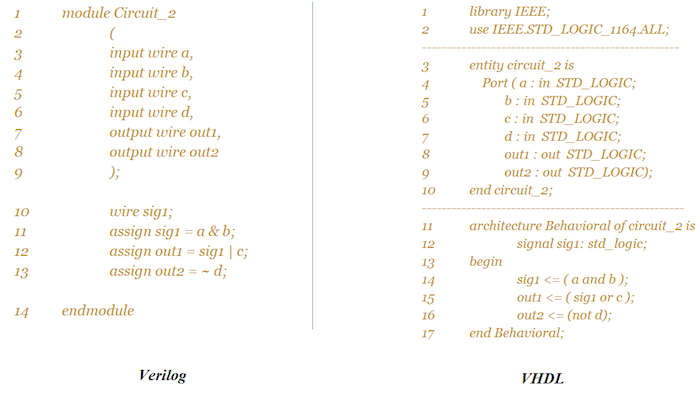

El código anterior también usa algunos nuevos operadores bit a bit de Verilog:~ para NOT y | para la operación OR. Otro operador bit a bit útil es ^ para la operación XOR. La Figura 4 muestra las descripciones de Verilog y VHDL para el módulo Circuit_2. Estas comparaciones pueden ayudarlo a ver las diferencias y similitudes entre estos dos idiomas.

Figura 4. Comparación de las descripciones de Verilog y VHDL para Circuit_2.

Ejemplo 3

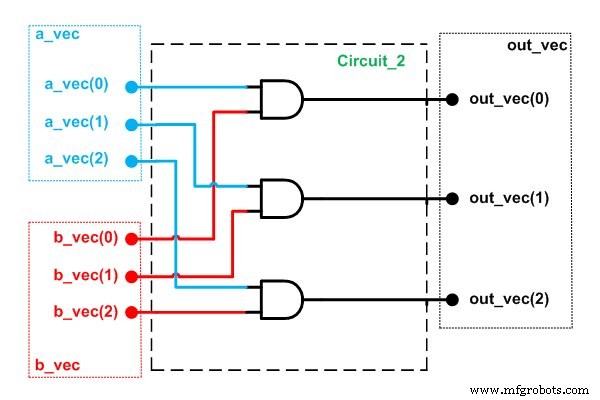

Para nuestro tercer y último ejemplo, proporcionaremos el código Verilog para el esquema que se muestra en la Figura 5.

Figura 5. Esquema, por ejemplo 3.

Como puede ver, existe una cierta relación entre los puertos de entrada azules y los rojos:las entradas correspondientes se combinan con el operador AND. El resultado se asigna a un puerto de salida. En tales casos, podemos agrupar las señales y tratarlas como un vector. Esto hace que el código sea compacto y legible.

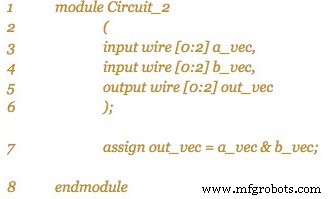

Usando el concepto de vector en Verilog, podemos extender fácilmente el código en el Listado 1 para describir el circuito anterior (Vea el código en el Listado 3 a continuación).

Tenga en cuenta que el rango de índice de los vectores puede ser ascendente ([0:2] como se usó anteriormente) o descendente ([2:0]). Aunque el formato ascendente se usa anteriormente, generalmente es menos propenso a errores usar el formato descendente. Esto se debe al hecho de que el estilo descendente coincide con nuestra percepción de que la posición más a la izquierda de un número binario tiene el índice más alto. Tenga en cuenta que los vectores también se utilizan en VHDL.

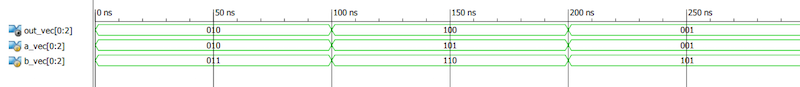

La Figura 6 a continuación muestra una simulación ISE del código del Listado 3.

Figura 6. Simulación ISE del código del Ejemplo 3.

En este artículo, discutimos que es una buena idea aprender tanto VHDL como Verilog, estudiamos la estructura básica de un módulo Verilog y nos familiarizamos con el tipo de datos "cable" de Verilog y su forma vectorial. También mencionamos brevemente algunas diferencias entre VHDL y Verilog. El próximo artículo de nuestra serie Verilog discutirá el diseño de circuitos combinacionales en Verilog.

Incrustado

- Contenedores listos para el código:Introducción a las herramientas de automatización de procesos en la nube

- Introducción a la impresión 3D de cerámica

- Introducción a TJBot

- Introducción a RAK 831 Lora Gateway y RPi3

- Introducción a RAK831 LoRa Gateway y RPi3

- Introducción a la IA en seguros:una guía introductoria

- Cómo comenzar con la inferencia de IA en el perímetro

- Primeros pasos con Eagle Group:lo que necesita saber

- Cómo comenzar con My.Cat.com

- Node-RED y los primeros pasos con Docker

- Primeros pasos con Go on PLCnext