Diseño embebido con FPGA:Construyendo un proyecto

Nota del editor:a medida que continúan surgiendo algoritmos avanzados para diseños de productos inteligentes, los desarrolladores a menudo se encuentran luchando para implementar sistemas integrados capaces de satisfacer las demandas de procesamiento asociadas de estos algoritmos. Los FPGA pueden ofrecer el rendimiento requerido, pero el diseño con FPGA se ha considerado durante mucho tiempo limitado al ámbito de los expertos en programación de FPGA. Sin embargo, hoy en día, la disponibilidad de FPGA más potentes y entornos de desarrollo más efectivos ha hecho que el desarrollo de FPGA sea ampliamente accesible. En este extracto, Capítulo 4 del libro Architecting High-Performance Embedded Systems, el autor ofrece una revisión completa de los dispositivos FPGA, los lenguajes de implementación y el proceso de desarrollo de FPGA, así como un tutorial detallado de cómo comenzar a implementar FPGA en su propio diseño. El extracto completo se presenta en la siguiente serie de entregas:

Nota del editor:a medida que continúan surgiendo algoritmos avanzados para diseños de productos inteligentes, los desarrolladores a menudo se encuentran luchando para implementar sistemas integrados capaces de satisfacer las demandas de procesamiento asociadas de estos algoritmos. Los FPGA pueden ofrecer el rendimiento requerido, pero el diseño con FPGA se ha considerado durante mucho tiempo limitado al ámbito de los expertos en programación de FPGA. Sin embargo, hoy en día, la disponibilidad de FPGA más potentes y entornos de desarrollo más efectivos ha hecho que el desarrollo de FPGA sea ampliamente accesible. En este extracto, Capítulo 4 del libro Architecting High-Performance Embedded Systems, el autor ofrece una revisión completa de los dispositivos FPGA, los lenguajes de implementación y el proceso de desarrollo de FPGA, así como un tutorial detallado de cómo comenzar a implementar FPGA en su propio diseño. El extracto completo se presenta en la siguiente serie de entregas:

1:Recursos de hardware

2:Idiomas de implementación

3:Proceso de desarrollo

4:Construyendo un proyecto (este artículo)

5:Implementación

Adaptado de Architecting High-Performance Embedded Systems, por Jim Ledin.

Desarrollando su primer proyecto FPGA

En esta sección, desarrollaremos e implementaremos un proyecto simple pero completo utilizando un dispositivo FPGA Xilinx Artix-7 instalado en una placa de desarrollo Digilent Arty A7. Esta placa viene en dos variantes, una versión de menor costo (US $ 129) con un número de modelo que termina en-35T y una versión más capaz, pero más costosa (US $ 249) con un número de modelo que termina en -100T. La única diferencia entre las dos placas es el modelo de Artix-7 FPGA instalado en la placa. Como era de esperar, el -35T tiene menos recursos disponibles que el -100T.

Puede utilizar la variante -35T o -100T para este proyecto. La única diferencia en el proceso de desarrollo es especificar el modelo de placa correcto siempre que surja la necesidad. Sin embargo, en capítulos posteriores, se requerirá la variante -100T debido a los requisitos de recursos del diseño de proyecto de osciloscopio digital de ejemplo, por lo que se recomienda la placa más capaz.

Las placas Arty A7 están disponibles para su compra en https://store.digilentinc.com/arty-a7-artix-7-fpga-development-board-for-makers-and-hobbyists/ y de otras fuentes, como Amazon.

Para el propósito de este proyecto, los recursos en la placa de interés son el dispositivo FPGA en sí, así como los cuatro interruptores, cuatro botones y cinco LED. Este proyecto demostrará cómo instalar la suite de herramientas Vivado, crear un proyecto, ingresar código HDL, probar el código y, finalmente, producir un flujo de bits y descargarlo a la placa. Después de descargar el flujo de bits a la placa, podrá probar manualmente el funcionamiento del sistema. También verá cómo programar la imagen FPGA en la memoria flash de la placa Arty A7 para que se cargue y se ejecute cada vez que se encienda la placa.

Descripción del proyecto

Este proyecto implementará un sumador binario de cuatro bits en la FPGA. Este es intencionalmente un diseño muy simple porque el enfoque aquí está en configurar las herramientas y aprender a usarlas, y no en implementar un modelo HDL complejo.

Los cuatro interruptores de la placa representan un número binario de 4 bits y los cuatro botones pulsadores representan otro número de 4 bits. La lógica FPGA realizará continuamente una operación de suma entre estos dos números y mostrará el resultado como un número binario de 4 bits en cuatro LED con un quinto LED que representa el bit de acarreo.

El código sumador de 4 bits se basa en el circuito sumador completo de un solo bit descrito en los lenguajes de diseño de hardware sección del Capítulo 1 , Arquitectura de sistemas integrados de alto rendimiento .

Instalación de las herramientas de Vivado

Usaremos la suite Xilinx Vivado de herramientas de desarrollo FPGA para este proyecto y para proyectos en capítulos futuros. Estas herramientas están disponibles de forma gratuita y son compatibles con los sistemas operativos Windows y Linux. Puede instalar las herramientas en cualquier sistema operativo. La descripción en esta sección cubre la versión de Windows de las herramientas, pero si está instalando en Linux, las diferencias deberían ser obvias. Trabajar con las herramientas de Vivado debería ser casi idéntico en los diferentes sistemas operativos:

- Si aún no tiene una, cree una cuenta de usuario de Xilinx en https://www.xilinx.com/registration/create-account.html.

- Visite https://xilinx.com e inicie sesión en su cuenta de usuario. Una vez que haya iniciado sesión, vaya a la página de descarga de herramientas en https://www.xilinx.com/support/download.html.

- Descargue Xilinx Unified Installer:Windows Self-Extracting Web Installer . Probablemente debería seleccionar la última versión disponible, pero si desea seguir junto con la versión utilizada en este libro, seleccione la versión 2020.1 .

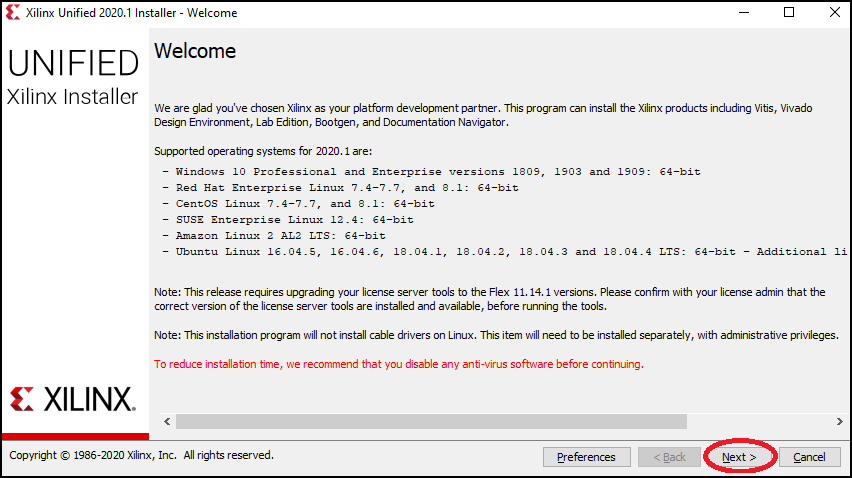

- El archivo de instalación tendrá un nombre similar a Xilinx_ 1_0602_1208_Win64.exe. Busque este archivo en su directorio de descargas y ejecútelo. Si un cuadro de diálogo le advierte sobre la instalación de una aplicación que no está verificada por Microsoft, haga clic en Instalar de todos modos .

- Cuando la bienvenida aparece la pantalla, haga clic en Siguiente :

Figura 4.3 - Cuadro de diálogo de bienvenida del instalador

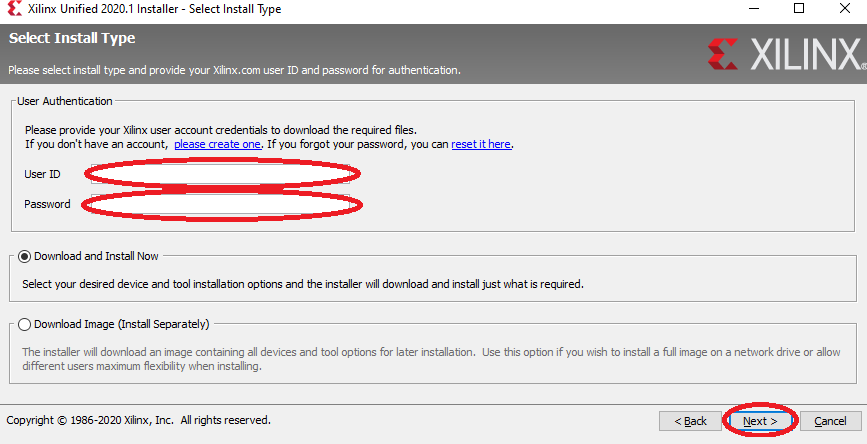

- En la siguiente pantalla, ingrese su ID de usuario y contraseña de xilinx.com, luego haga clic en Siguiente :

Figura 4.4 - Cuadro de diálogo de inicio de sesión del instalador

- El siguiente cuadro de diálogo le solicita que acepte algunos acuerdos de licencia. Marca las casillas que dicen Acepto . , luego haga clic en Siguiente .

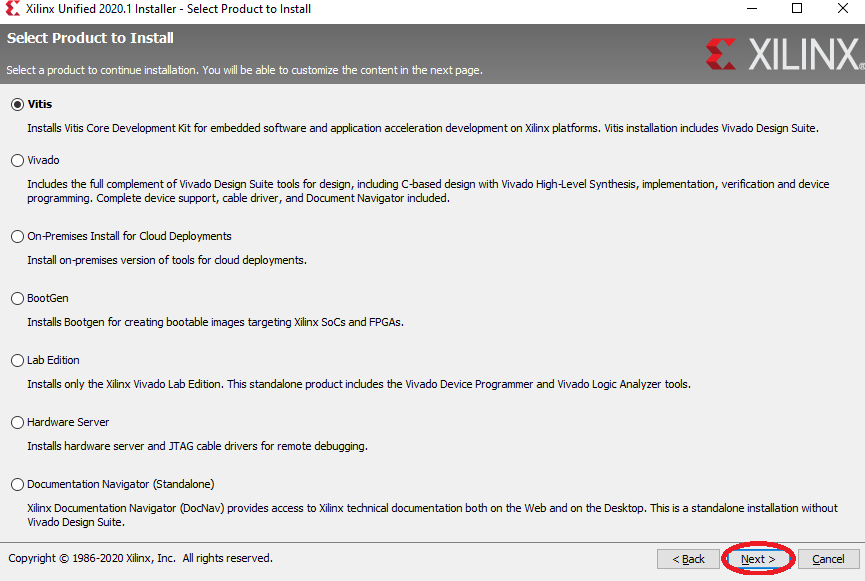

- En el siguiente cuadro de diálogo, deje Vitis seleccionado como producto a instalar y haga clic en Siguiente . Vitis incluye el conjunto de herramientas Vivado junto con una colección de otras herramientas de desarrollo de Xilinx:

Figura 4.5 - Cuadro de diálogo de selección de producto del instalador

- El siguiente cuadro de diálogo le permite seleccionar los componentes de software que se instalarán. Deje las selecciones en sus valores predeterminados y haga clic en Siguiente .

- El siguiente cuadro de diálogo le permite seleccionar un directorio de destino y especificar opciones de acceso directo al programa. Un directorio de destino de C:\ Xilinx es una ubicación adecuada. Cree este directorio si no existe. Haga clic en Siguiente . .

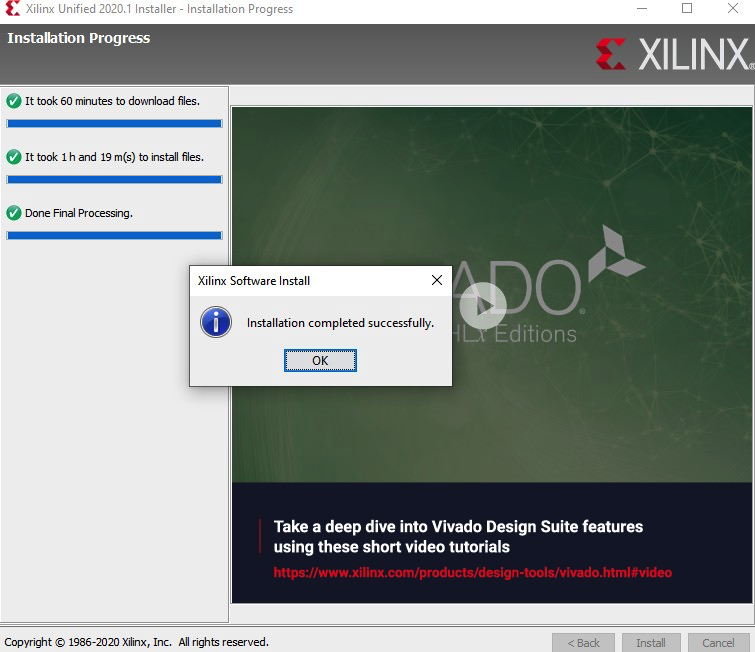

- El siguiente cuadro de diálogo muestra un resumen de las opciones de instalación. Haga clic en Instalar . para continuar con la instalación. Según la velocidad de su computadora y su conexión a Internet, la instalación puede demorar algunas horas en completarse:

Figura 4.6 - Cuadro de diálogo de instalación completa

Una vez completada la instalación, crearemos nuestro primer proyecto.

Creación de un proyecto

Siga estos pasos para crear y construir el proyecto sumador binario de 4 bits para la placa Arty A7:

- Ubique el ícono del escritorio titulado Vivado 2020.1 (o busque su número de versión, si es diferente) y haga doble clic en él.

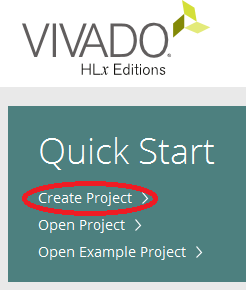

- Cuando Vivado muestre su pantalla principal, haga clic en Crear proyecto en el Inicio rápido sección:

Figura 4.7 - Cuadro de diálogo de inicio rápido de Vivado

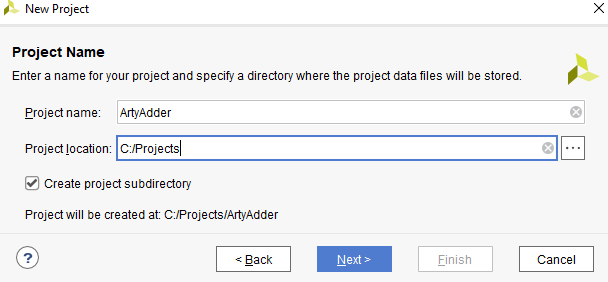

- Esto iniciará Crear un nuevo proyecto de Vivado mago. Haga clic en Siguiente . para llegar al nombre del proyecto e ingrese ArtyAdder como el nombre del proyecto. Seleccione una ubicación de directorio apropiada para el proyecto y marque la casilla para crear un subdirectorio, luego haga clic en Siguiente . Los ejemplos de este libro utilizarán el directorio C:\ Proyectos como ubicación para todos los proyectos:

Figura 4.8 - Cuadro de diálogo Nombre del proyecto

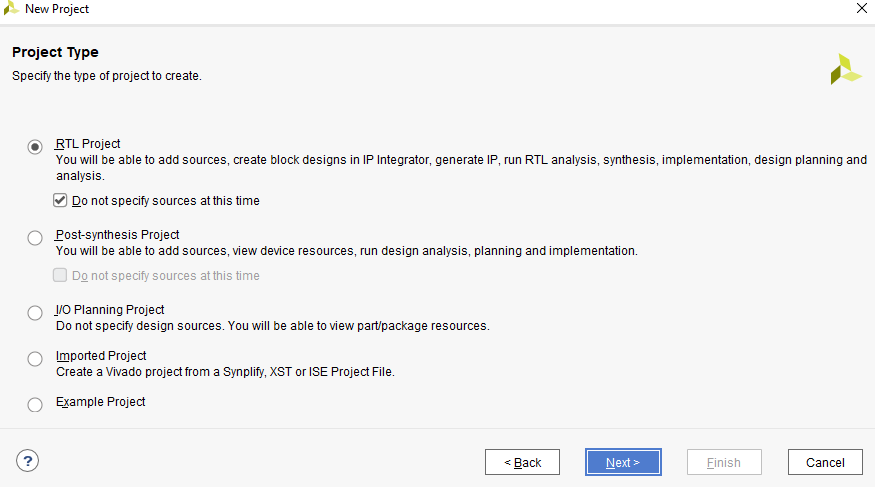

- En Tipo de proyecto cuadro de diálogo, seleccione Proyecto RTL y marque la casilla junto a No especificar fuentes en este momento . Haga clic en Siguiente . :

Figura 4.9 - Cuadro de diálogo Tipo de proyecto

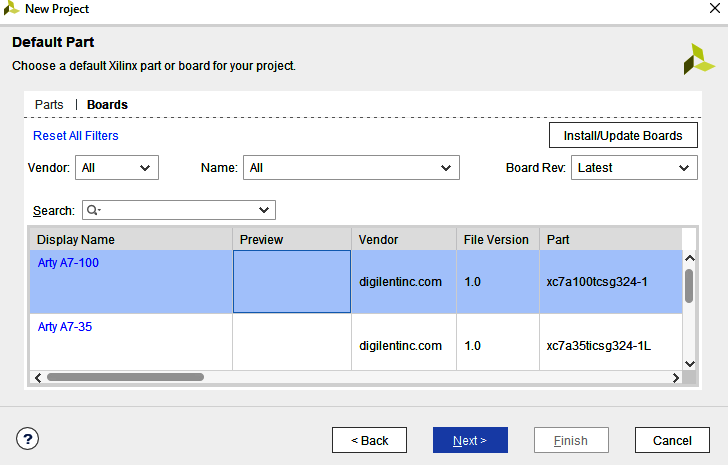

- En la Parte predeterminada cuadro de diálogo, haga clic en Tableros pestaña y escribe Arty en la Búsqueda campo. Dependiendo del tipo de tabla que tengas (o si aún no tienes una), selecciona Arty A7-100 o Arty A7-35 y haga clic en Siguiente :

Figura 4.10 - Cuadro de diálogo Pieza predeterminada

- En el Resumen de proyecto nuevo cuadro de diálogo, haga clic en Finalizar .

Ahora hemos creado un proyecto vacío. En la siguiente sección, crearemos archivos fuente VHDL que contienen el diseño del circuito lógico para este proyecto.

Creación de archivos fuente VHDL

Los siguientes pasos describen el proceso de creación de archivos fuente VHDL, ingresando el código fuente y compilando el diseño FPGA:

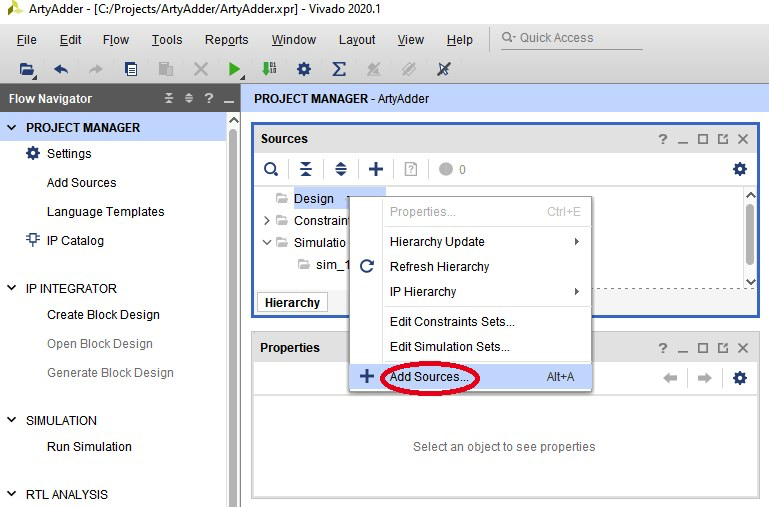

- En Fuentes subventana, haga clic con el botón derecho en Fuentes de diseño y seleccione Agregar fuentes… :

Figura 4.11 - Agregar fuentes… selección de menú

- En Agregar fuentes cuadro de diálogo, asegúrese de Agregar o crear fuentes de diseño está seleccionado, luego haga clic en Siguiente .

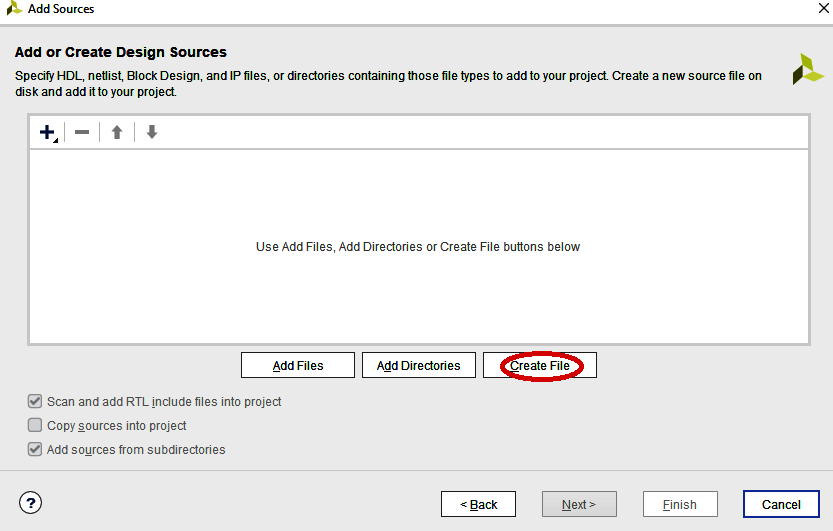

- En Agregar o crear fuentes de diseño cuadro de diálogo, haga clic en Crear archivo :

Figura 4.12 - Cuadro de diálogo Agregar o crear fuentes de diseño

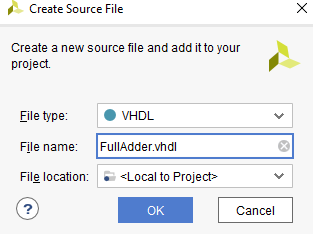

- Introduzca el nombre de archivo FullAdder.vhdl y haga clic en Aceptar . :

Figura 4.13 - Cuadro de diálogo Crear archivo de origen

- Repite los dos pasos anteriores para crear otro archivo llamado Adder4.vhdl, luego haz clic en Finalizar . en Agregar o crear fuentes de diseño diálogo.

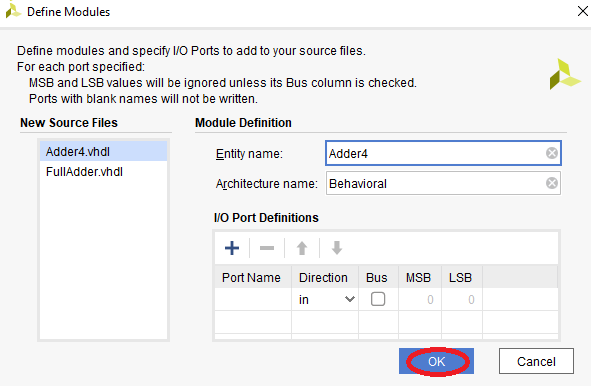

- Definir módulos El cuadro de diálogo aparecerá a continuación. No ingresaremos nada aquí. Haga clic en Aceptar . para cerrar esto Se le preguntará si está seguro de que desea utilizar estos valores. Haga clic en Sí . :

Figura 4.14 - Cuadro de diálogo Definir módulos

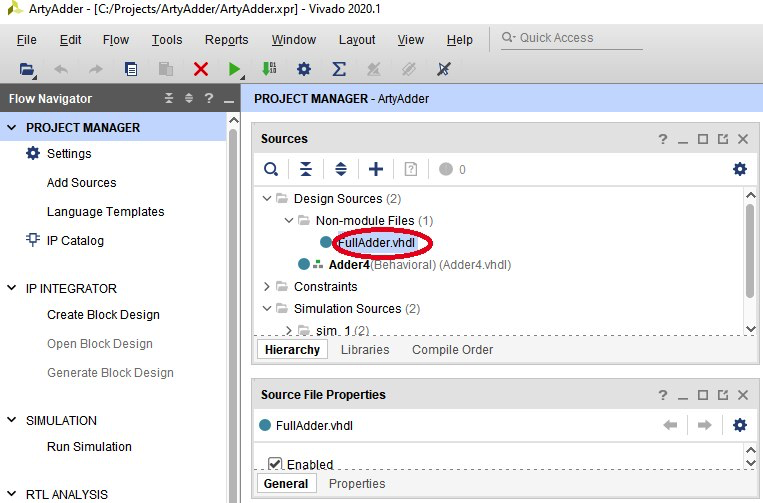

- Expanda los archivos que no son del módulo en Fuentes de diseño y luego haga doble clic en FullAdder.vhdl. Se abrirá una ventana del editor mostrando el archivo FullAdder.vhdl vacío:

Figura 4.15 - Archivo fuente recién creado

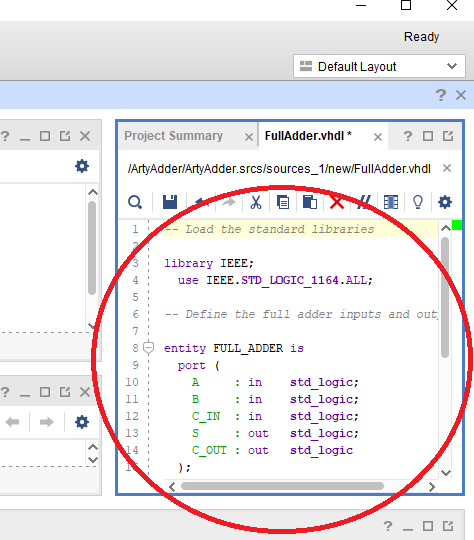

- Ingrese el siguiente código VHDL en la ventana del editor FullAdder.vhdl:

- Cargue la biblioteca de bibliotecas estándar IEEE; use IEEE.STD_LOGIC_1164.ALL; - Defina las entradas y salidas del sumador completo; FULL_ADDER es el puerto (A:en std_logic; B:en std_logic; C_IN:en std_logic; S:out std_logic; C_OUT:out std_logic); entidad final FULL_ADDER; - Definir el comportamiento de la arquitectura complementaria completa BEHAVIORAL de FULL_ADDER isbegin S <=(A XOR B) XOR C_IN; C_OUT <=(A AND B) OR ((A XOR B) AND C_IN); arquitectura final BEHAVIORAL;

Este es el mismo código sumador completo de un solo bit que examinamos en los lenguajes de diseño de hardware sección del Capítulo 1, Arquitectura de sistemas integrados de alto rendimiento . Figura 4.16 muestra el código en la ventana del editor Vivado:

Figura 4.16 - Código fuente de FullAdder.vhdl

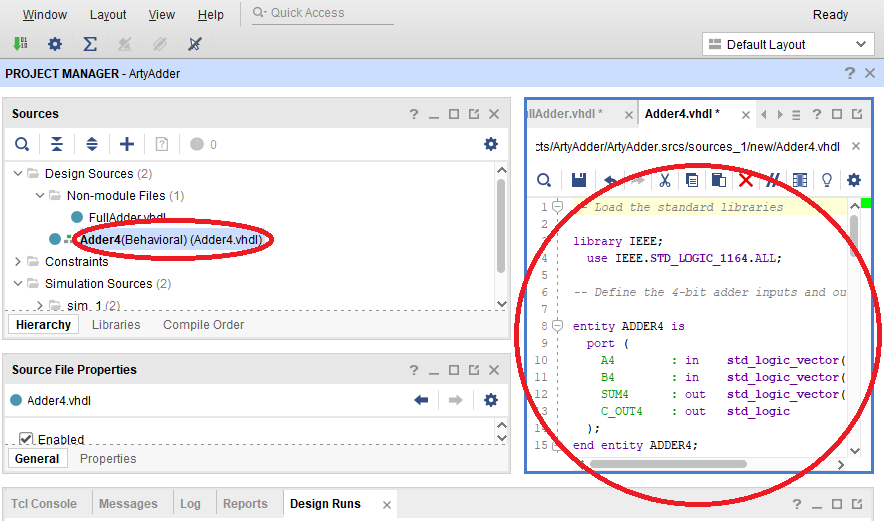

- De la misma manera, haga doble clic en Adder4 (Behavioural) (Adder4.vhdl) en Fuentes de diseño . Elimina los contenidos rellenados automáticamente de Adder4.vhdl ventana del editor e introduzca el siguiente código en Adder4.vhdl editor:

- Cargue la biblioteca de bibliotecas estándar IEEE; use IEEE.STD_LOGIC_1164.ALL; - Defina las entradas de sumador de 4 bits y la salida ADDER4 es el puerto (A4:en std_logic_vector (3 downto 0); B4:en std_logic_vector (3 downto 0); SUM4:out std_logic_vector (3 downto 0) ); C_OUT4:out std_logic); entidad final ADDER4; - Definir el comportamiento de la arquitectura de adición de 4 bits. std_logic; C_IN:en std_logic; S:fuera std_logic; C_OUT:fuera std_logic); componente final; - Definir las señales utilizadas internamente en la señal de sumador de 4 bits c0, c1, c2:std_logic; begin - La entrada de acarreo al primer sumador se establece en 0 FULL_ADDER0:FULL_ADDER mapa de puertos (A => A4 (0), B => B4 (0), C_IN => '0', S => SUM4 (0), C_OUT => c0); FULL_ADDER1:mapa de puertos FULL_ADDER (A => A4 (1), B => B4 (1), C_IN => c0, S => SUM4 (1), C_OUT => c1); FULL_ADDER2:mapa de puertos FULL_ADDER (A => A4 (2), B => B4 (2), C_IN => c1, S => SUM4 (2), C_OUT => c2); FULL_ADDER3:mapa de puertos FULL_ADDER (A => A4 (3), B => B4 (3), C_IN => c2, S => SUM4 (3), C_OUT => C_OUT4); arquitectura final BEHAVIORAL;

Este código instancia cuatro copias del sumador completo de un solo bit. El acarreo en el sumador menos significativo se establece en cero y el acarreo de cada sumador ondula al siguiente sumador más significativo. El resultado de sumar dos números de 4 bits es un resultado de 4 bits y un acarreo de un solo bit:

Figura 4.17 - Código fuente de Adder4.vhdl

El siguiente artículo mostrará cómo probar el diseño e implementar nuestro diseño para la placa Arty.

Reproducido con permiso de Packt Publishing. Copyright © 2021 Packt Publishing

Jim Ledin es el director ejecutivo de Ledin Engineering, Inc. Jim es un experto en diseño, desarrollo y pruebas de software y hardware integrados. También tiene experiencia en evaluación de ciberseguridad de sistemas integrados y pruebas de penetración. Tiene un B.S. Licenciado en ingeniería aeroespacial de la Universidad Estatal de Iowa y un M.S. Licenciatura en ingeniería eléctrica e informática del Instituto de Tecnología de Georgia. Jim es un ingeniero eléctrico profesional registrado en California, un profesional certificado en seguridad del sistema de información (CISSP), un hacker ético certificado (CEH) y un probador de penetración certificado (CPT).

Jim Ledin es el director ejecutivo de Ledin Engineering, Inc. Jim es un experto en diseño, desarrollo y pruebas de software y hardware integrados. También tiene experiencia en evaluación de ciberseguridad de sistemas integrados y pruebas de penetración. Tiene un B.S. Licenciado en ingeniería aeroespacial de la Universidad Estatal de Iowa y un M.S. Licenciatura en ingeniería eléctrica e informática del Instituto de Tecnología de Georgia. Jim es un ingeniero eléctrico profesional registrado en California, un profesional certificado en seguridad del sistema de información (CISSP), un hacker ético certificado (CEH) y un probador de penetración certificado (CPT). Contenidos relacionados:

- Diseño integrado con FPGA:recursos de hardware

- Diseño integrado con FPGA:lenguajes de implementación

- Diseño integrado con FPGA:proceso de desarrollo

- Las herramientas de código abierto ayudan a simplificar la programación FPGA

- Implementación de algoritmos de punto flotante en FPGA o ASIC

- Aprovechamiento de FPGA para el aprendizaje profundo

- Las herramientas de software migran el código de la GPU a FPGA para aplicaciones de inteligencia artificial

- Los FPGA desplazan a los ASIC en el ADAS basado en la visión de Subaru Eyesight

Para obtener más información sobre Embedded, suscríbase al boletín informativo semanal por correo electrónico de Embedded.

Incrustado

- Fabricación de aditivos líquidos:construcción de objetos 3D con líquido

- Qué es el diseño de sistemas integrados:pasos en el proceso de diseño

- Convertir macrodatos en datos inteligentes con IA incorporada

- Creación de interconexiones de alto rendimiento con varias generaciones de PCIe

- Arrow Electronics lanza el concurso europeo de desarrolladores FPGA

- El kit de diseño mide la presión arterial con un sensor óptico

- FPGA de grado de defensa debuta con acceso anticipado

- Creación de robots con Raspberry Pi y Python

- Construyendo un segway con Raspberry Pi

- GoPiGo v2 con Windows IoT

- Todo con aditivo