Creación de interconexiones de alto rendimiento con varias generaciones de PCIe

PCI Express y el hambre de ancho de banda

Como medio para conectar procesadores de host personalizados, integrados y de computación a periféricos de "punto final", como puertos Ethernet, puertos USB, tarjetas de video y dispositivos de almacenamiento, PCI Express® (PCIe®) se ha convertido en la interconexión de alto rendimiento de referencia. Al aprovechar la comunicación en serie de alta velocidad, PCIe ofrece una conectividad punto a punto eficiente y, al aumentar el número de canales y la velocidad de señalización, el ancho de banda de la interfaz escalable.

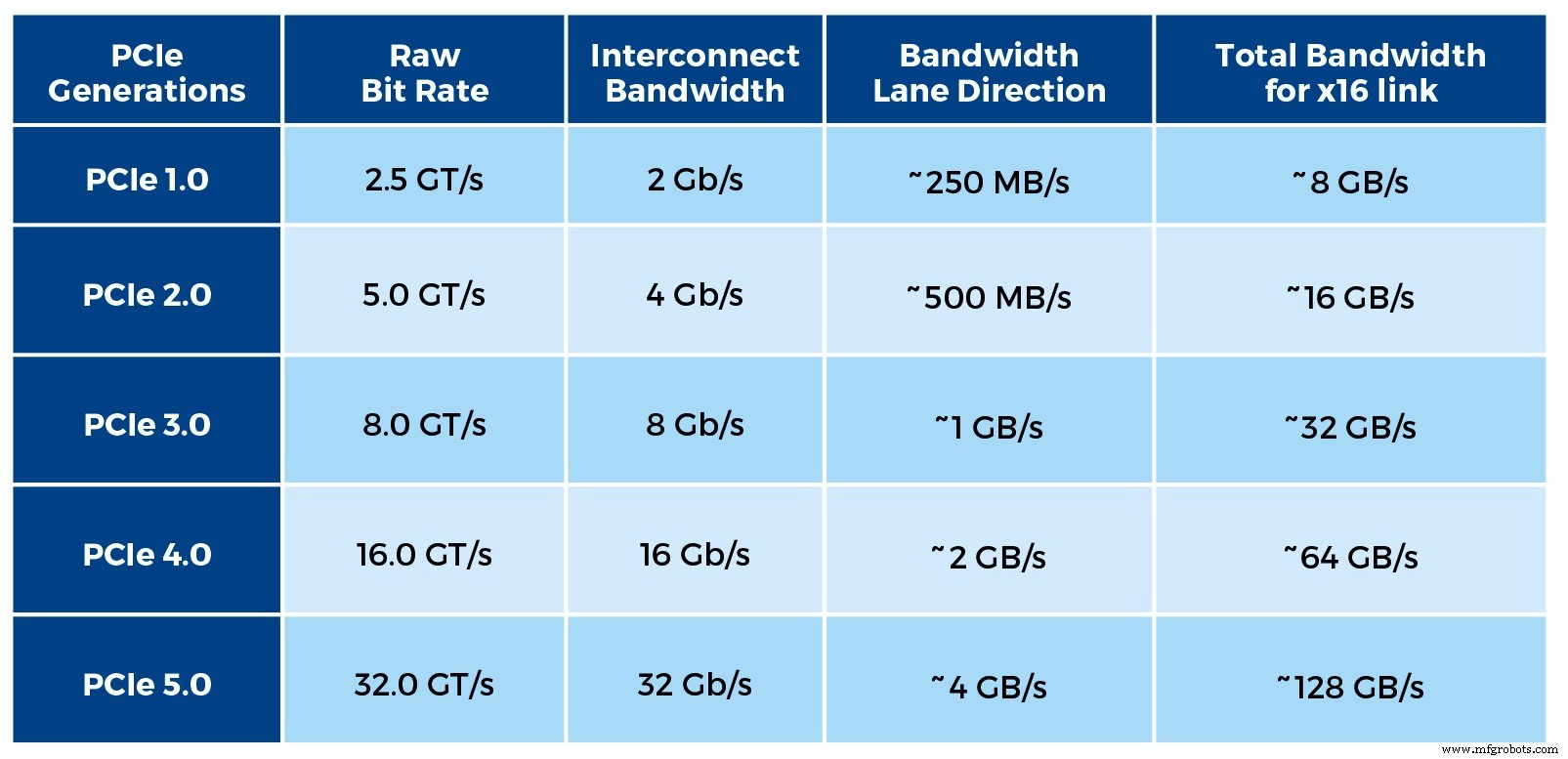

La especificación PCIe 1.0 se publicó en 2002, operando a 2.5 giga-transferencias por segundo (GT / s) dando un ancho de banda de interfaz x16 total de 8GByte / s. El ancho de banda se duplicó posteriormente en 2006 con la llegada de las especificaciones PCIe 2.0 de segunda generación y nuevamente en 2010 cuando PCIe 3.0 aumentó el ancho de banda a 32 GByte / s para satisfacer las crecientes demandas impuestas por las principales aplicaciones contemporáneas, incluidas PC de alta gama, juegos, informática empresarial y redes.

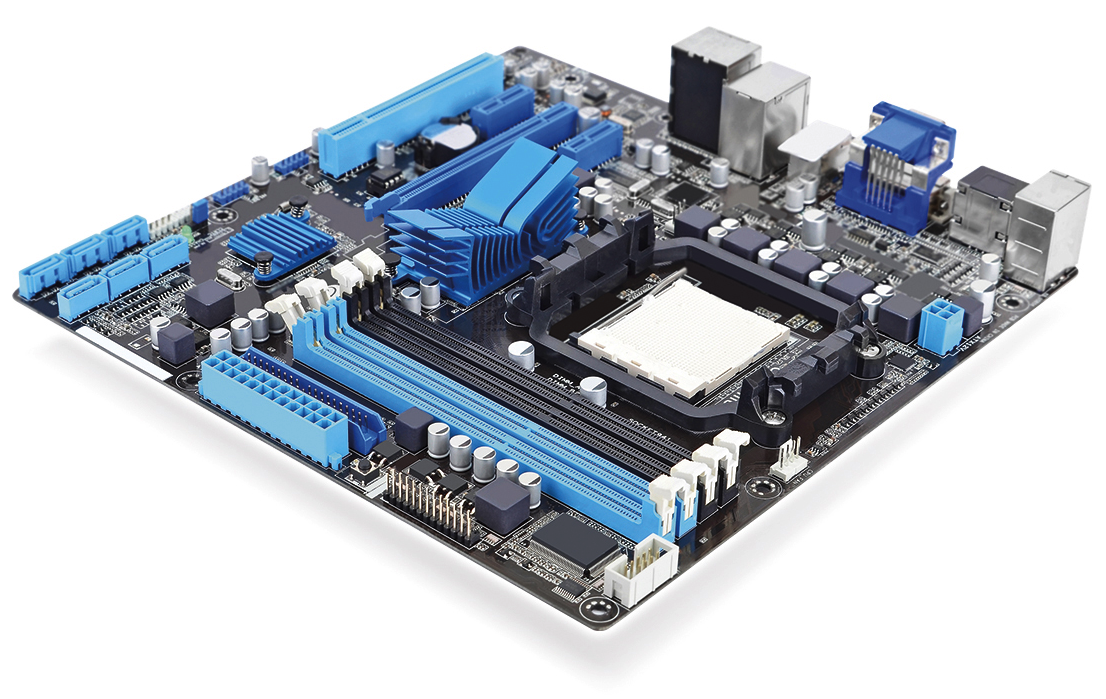

PCI Express se ha convertido en la interconexión de alto rendimiento de referencia para una amplia gama de diseños de sistemas.

(Fuente:Diodes Inc.)

Más recientemente, la rápida difusión de servicios basados en la nube, como las redes sociales y la transmisión de video, ha introducido requisitos nuevos y más exigentes para la conectividad de alta velocidad dentro de los centros de datos a gran escala.

Ahora, a medida que la era de IoT se afianza, los sensores en red instalados en ciudades e infraestructuras inteligentes, fábricas inteligentes y otros activos industriales, edificios comerciales y residenciales y dispositivos portátiles para seguimiento médico y de fitness están configurados para generar grandes cantidades de datos para que los centros de datos de hiperescala capturar, almacenar, procesar y analizar. Estas fuerzas están impulsando la demanda de las próximas generaciones de PCIe para conectar de manera eficiente los servidores del centro de datos a Ethernet de alta velocidad, almacenamiento conectado a la red y aceleradores de inteligencia artificial.

Los autos conectados aumentarán aún más la carga de datos, agregando presión en tiempo real, para permitir niveles más altos de conducción autónoma y, en última instancia, vehículos totalmente autónomos. Detrás de los centros de datos, el entrenamiento de redes neuronales para la inferencia de IA es una tarea intensiva en computación que expone de manera aguda los cuellos de botella en las comunicaciones periféricas.

Ahora que estos diversos factores entran en juego, es el momento adecuado para que PCIe vuelva a avanzar. PCIe 4.0, anunciado en 2017, fue seguido rápidamente con la publicación de PCIe 5.0 en 2019. La Figura 1 muestra las velocidades agregadas que ofrece cada versión de PCIe.

Figura 1:Velocidades agregadas ofrecidas por las versiones PCIe (Fuente:Diodes Inc.)

Se espera que PCIe 5.0 se utilice ampliamente a medida que los centros de datos líderes hagan la transición de Ethernet de 100 Gb a la última especificación de 400 Gb. En la práctica, los aumentos en el ancho de banda PCIe se han mantenido más o menos a la par con los avances en las velocidades de Ethernet, lo que idealmente mantiene un equilibrio entre los dos estándares para ayudar a evitar cuellos de botella en el rendimiento.

Los estándares PCI "heredados" se mantienen vigentes

A medida que los productos PCIe 5.0 comienzan a ingresar al mercado, y con el reciente anuncio del Grupo de Interés Especial de PCI (PCI-SIG) de que el trabajo ha comenzado en la próxima generación, PCIe 6.0 para completarse en 2021, PCIe es el protocolo de elección para el rendimiento. -Comunicaciones periféricas hambrientas, en el futuro previsible.

Al mismo tiempo, la compatibilidad con versiones anteriores es una fortaleza clave del linaje PCIe. Debido a que no existe una fecha de vencimiento para las especificaciones de PCIe, varias generaciones pueden coexistir en el mercado e incluso en la misma aplicación. Esto es una ventaja para los diseñadores de sistemas:mientras que surgen nuevas generaciones sucesivas de PCIe para abordar los requisitos cada vez más hambrientos de ancho de banda, las iteraciones anteriores continúan brindando valor en una gran cantidad de escenarios, como computación personal, juegos y algunas aplicaciones de redes y computación empresarial.

Resolver desafíos de implementación

La compatibilidad con versiones anteriores entre las diversas generaciones de PCIe permite que los sistemas se beneficien de velocidades de transferencia más altas a medida que se dispone de nuevo silicio, con cambios mínimos de diseño. Por otro lado, el aumento de la velocidad de la señal ejerce una presión adicional sobre los márgenes de la señal y puede aumentar la complejidad del diseño. Además, existe una clara necesidad de soluciones que permitan el puenteo desde y hacia PCIe, no solo entre interfaces heredadas, sino también entre otras interfaces como puertos USB o gráficos.

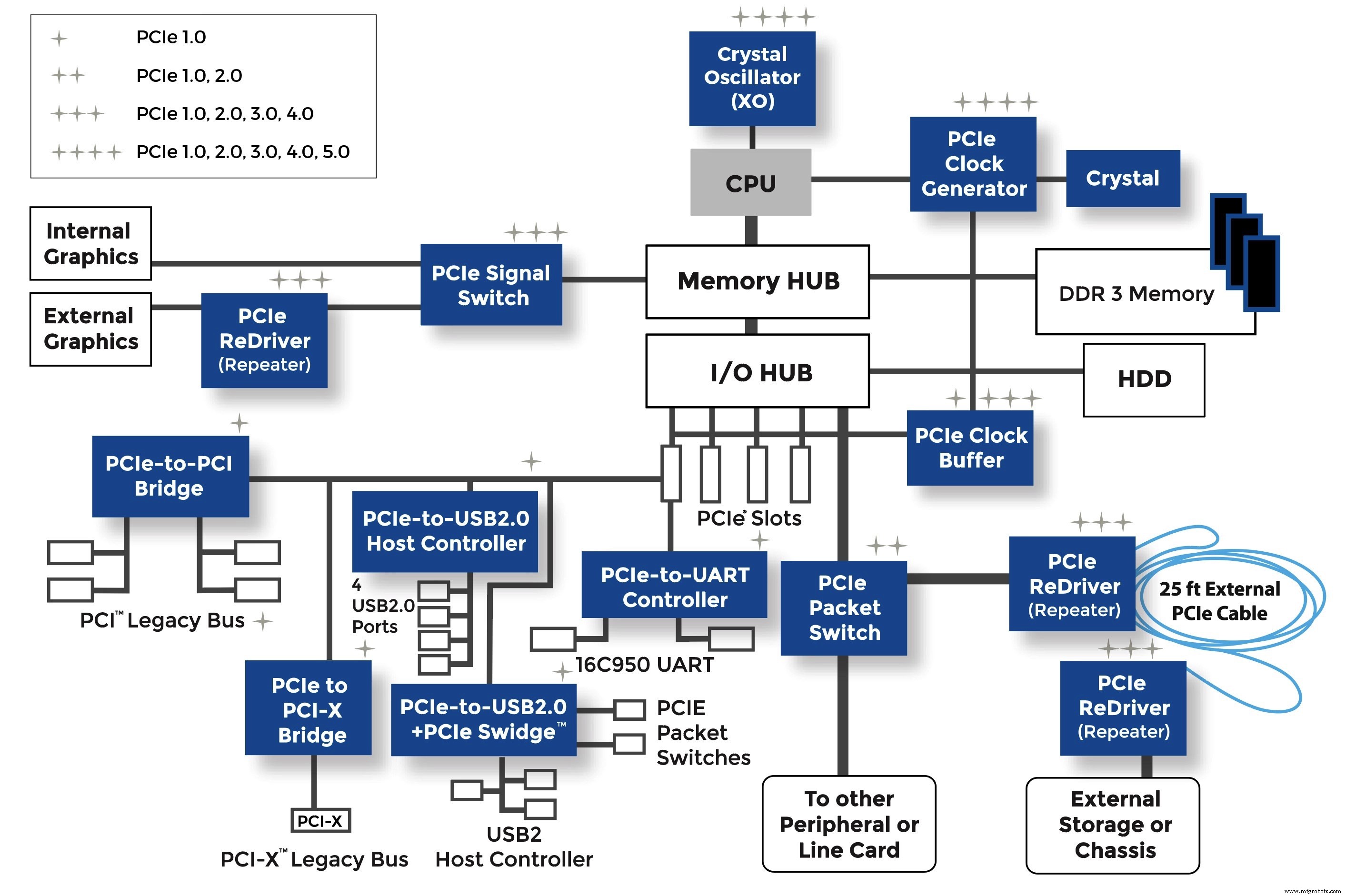

Para manejar estos desafíos, los diseñadores necesitan acceso a dispositivos que admitan varias generaciones de PCIe, como generadores de reloj, búferes de reloj, controladores, conmutadores / puentes de paquetes, chips ReDriver ™ y multiplexores de alta velocidad que se muestran en la figura 2.

haz clic para ampliar la imagen

Figura 2:Un ejemplo de las soluciones PCIe disponibles de Diodes Inc. (Fuente:Diodes Inc.)

Los chips ReDriver pueden proporcionar una solución rentable y conveniente para aumentar la integridad de la señal en sistemas de alta velocidad. Usando técnicas como ecualización y pre-énfasis, con un controlador de salida que introduce una latencia mínima, el ReDriver compensa las pérdidas en la línea de transmisión para restaurar el margen de la señal y minimizar la fluctuación para asegurar una baja tasa de error de bit en el receptor. En comparación con un temporizador, que integra funciones adicionales que incluyen reloj y recuperación de datos, un ReDriver presenta un retardo bajo y es relativamente económico y fácil de implementar. La Figura 2 muestra cómo se puede usar un PCIe ReDriver cuando se requiere que las señales se transmitan a través de una pista de PCB más larga, como a una tarjeta gráfica externa o mediante un cable a un almacenamiento externo. Estos ReDrivers son totalmente compatibles con versiones anteriores y son compatibles con todas las generaciones anteriores de PCIe.

Los puentes y conmutadores satisfacen los requisitos de interfaz entre dispositivos de punto final y host de varios tipos. Un puente de paquetes proporcionará típicamente una interfaz entre dos capas en el modelo de referencia OSI, o entre dos protocolos. La Figura 2 también muestra cómo se puede usar un puente para conectarse entre PCIe y estándares PCI heredados, incluido PCI-X, o puertos USB o una interfaz de bus UART. Los conmutadores de paquetes son dispositivos multipuerto / multilane que generalmente se utilizan para expandir un único complejo raíz a varios puertos con múltiples carriles para acceder a otros sistemas de pares, como un periférico o una tarjeta de línea.

Además de los conmutadores y puentes de paquetes individuales con varias configuraciones de puertos y capacidades de traducción, las funcionalidades de un conmutador de paquetes PCIe y un puente PCIe a USB2.0 se combinan en dispositivos como el conmutador PCI Express-to-USB 2.0 de Diodes Incorporated PI7C9X442SL '. Este dispositivo multifuncional puede desplegarse desde un puerto ascendente PCIe x1 a dos puertos descendentes x1 y cuatro puertos USB 2.0, y permite que el procesador host del sistema acceda a múltiples dispositivos PCIe y USB simultáneamente.

Empresas como Diodes Inc. pueden ofrecer una cartera de multiplexores / demultiplexores de señal PCIe 1.0, PCIe 2.0 o PCIe 3.0 bidireccionales pasivos para conectar un solo carril PCIe a varios carriles para la expansión del ancho de banda para gráficos o computación. Estos dispositivos también se pueden utilizar para habilitar conexiones desde una única interfaz multiprotocolo.

Los búferes de reloj normalmente pueden tomar una única señal de referencia como entrada y producir múltiples salidas para una distribución más amplia alrededor de una PCB. Los circuitos integrados de búfer de reloj están disponibles en una variedad de configuraciones y Diodes ofrece un diseño PLL patentado que garantiza que la fluctuación se mantenga dentro de los requisitos de PCIe. Los generadores de reloj pueden generar una señal de reloj a una frecuencia específica con una fluctuación de salida muy baja, lo que los hace adecuados para PCIe y otros relojes del sistema. Los diseñadores pueden encontrar una amplia gama de dispositivos adecuados, como los generadores de reloj y búfer de diodos 1.8V PI6CG18xxx y 1.5V PI6CG15xxx PCIe 4.0 en configuraciones de 2, 4 y 8 canales, que cumplen con todas las generaciones anteriores de PCIe. Al integrar terminaciones en el chip, estos dispositivos ahorran cuatro resistencias externas por salida, recortando hasta 32 componentes de la lista de materiales.

Conclusión

PCIe es la interconexión de alto rendimiento para aplicaciones que van desde la computación integrada y de escritorio hasta la conectividad del centro de datos de alto ancho de banda y la capacitación en redes neuronales. Los diseñadores pueden aprovechar la larga vida útil de los estándares PCIe anteriores, con compatibilidad retroactiva entre las especificaciones heredadas y de generación posterior, para satisfacer los diversos requisitos del sistema de manera rentable. Con acceso a una cartera de dispositivos que contiene funciones como puentes, búferes, ReDrivers, conmutadores y circuitos integrados de mux / demux, los diseñadores pueden ofrecer soluciones eficientes para aplicaciones exigentes.

Incrustado

- Fabricación de aditivos líquidos:construcción de objetos 3D con líquido

- Creación de aplicaciones híbridas de blockchain / nube con Ethereum y Google

- Creación de aplicaciones móviles sin servidor con React Native y AWS

- TECHWAY:plataforma Kintex-7 FPGA PCIe para aumentar el rendimiento de la velocidad de datos con 12 enlaces HSS

- Creación de robots con Raspberry Pi y Python

- Construyendo un segway con Raspberry Pi

- Nexam suministrará a Diab Nexamite que mejora las propiedades para la espuma de PET de alto rendimiento

- Compuestos de resina de ingeniería de alto rendimiento con contenido reciclado

- Cómo puede ayudar IoT con el big data de HVAC:Parte 2

- Construyendo el futuro de la experiencia del empleado con automatización inteligente

- Combinación de IA y robótica con múltiples sistemas de inspección