Comprender la tasa de error del código ADC

A medida que la frecuencia de muestreo de los convertidores de analógico a digital (ADC) de alta velocidad ha aumentado, también lo ha hecho el problema de los errores de código, también conocidos como códigos brillantes, en los datos de salida del ADC. Un error de código se define como un error en el código de salida de un ADC que excede un umbral definido. El umbral se define más comúnmente como el nivel en el que un error excede la amplitud esperada del ruido del ADC, de modo que el error se puede identificar fácilmente en presencia de ruido.

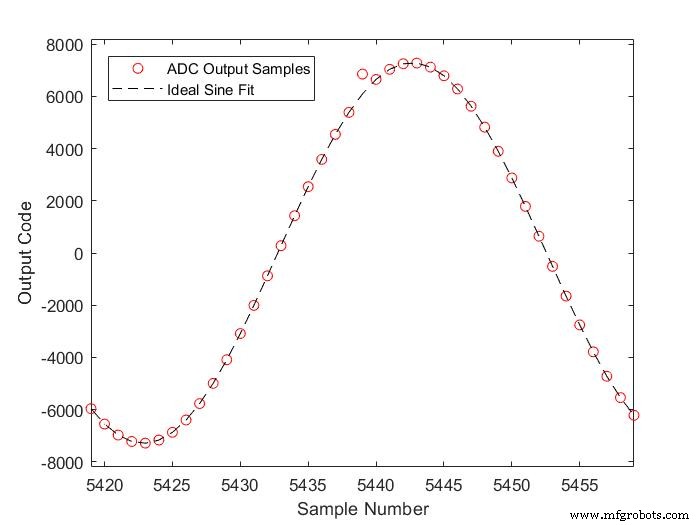

Otra forma de explicar esta definición del umbral de error es que la amplitud del error ocurre con una probabilidad que excede la probabilidad esperada de esa amplitud dado el supuesto ruido distribuido gaussiano del ADC. Figura 1 muestra un error de código de ejemplo encontrado en las muestras de salida de un ADC. La muestra errónea es claramente visible cuando se compara con el ajuste de onda sinusoidal ideal y supera con creces el ruido de las otras muestras en la gráfica.

Fig. 1:Ejemplo de una salida de ADC con un error de código.

La tasa de error de código (CER) de un ADC, también llamada tasa de error de palabra (WER) o tasa de error de metaestabilidad, se define como el número promedio de errores por muestra y se mide contando el número promedio de muestras entre errores consecutivos. Por lo general, se define como un orden de magnitud, como 10 –12 errores / muestra. El tiempo medio entre errores, por tanto, depende de la frecuencia de muestreo del convertidor. El CER medido es preciso solo cuando el ADC está funcionando a la frecuencia de muestreo a la que se midió el CER. En general, reducir la frecuencia de muestreo puede mejorar el CER en órdenes de magnitud.

Veamos de dónde provienen los errores de código para ver por qué la frecuencia de muestreo es un factor importante.

¿Qué hace que un ADC brille?

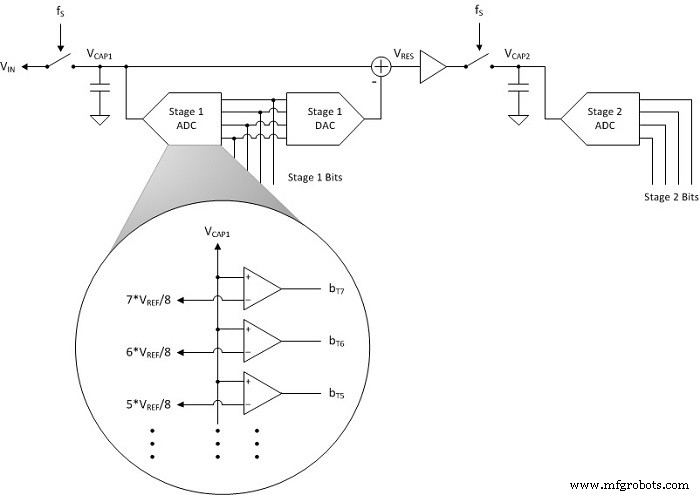

Una arquitectura de ADC de varios pasos, como un ADC flash canalizado o un ADC de registro de aproximación sucesiva (SAR), convierte el voltaje muestreado en bits digitales en etapas, y cada etapa consecutiva se basa en el resultado de la etapa anterior. Considere un ADC flash de alta velocidad con canalización básica, como se muestra en la Fig. 2 . Este ADC simplificado muestra dos etapas de conversión en las que cada etapa sucesiva produce un código digital que estima con más precisión la señal de entrada.

El funcionamiento del ADC mostrado es el siguiente:

-

La primera etapa muestrea el voltaje de entrada y convierte de manera aproximada la señal de entrada analógica en un código digital usando el ADC de la primera etapa. El ADC flash en esta etapa funciona comparando el voltaje muestreado con las referencias de voltaje estático, generadas a partir del voltaje de referencia principal del ADC (V REF ), utilizando comparadores de alta velocidad. La salida de los comparadores flash es una muestra digital codificada por termómetro que representa el voltaje de entrada.

-

El código del termómetro convertido se envía directamente al DAC de primera etapa. Este DAC emite el voltaje analógico, que corresponde a la muestra convertida de forma aproximada.

-

Restar la salida del DAC de primera etapa del voltaje de entrada original da como resultado el voltaje de error de cuantificación o voltaje residual (V RES ). Luego, el residuo se amplifica y se vuelve a muestrear (canalizar) para la segunda etapa.

-

El ADC de segunda etapa cuantifica V RES para obtener una estimación más precisa (de mayor resolución) del voltaje de entrada analógica original.

Fig. 2:Ejemplo de un diagrama de bloques de arquitectura ADC flash canalizado.

El V RES El proceso de creación introduce un ciclo de decisión de alta velocidad. Dentro de un período de reloj de muestreo, el ADC de primera etapa debe convertir el voltaje muestreado en un código digital. El código digital debe salir del DAC de la primera etapa, restarlo del voltaje de entrada original y volver a muestrearlo en la segunda etapa. El ciclo de decisión de alta velocidad introduce errores de código porque el comparador en el ADC flash tiene un tiempo de establecimiento que es una función de la diferencia entre el voltaje muestreado y V REF .

Más simplemente, un comparador tarda más en asentarse cuando el voltaje de entrada (V CAP1 ) está cerca del voltaje de referencia (como 7 * V REF / 8) del comparador. Teóricamente, si V CAP1 está infinitesimalmente cerca del voltaje de referencia del comparador, el comparador nunca se asentará porque estará operando en su región lineal.

El ruido evitará que esto ocurra realmente, pero si el comparador tarda demasiado en asentarse, entonces el DAC de primera etapa puede usar el código digital incorrecto para generar el voltaje analógico cuantificado. El resultado es un V RES que no coincide con el código de salida digital real del ADC de la primera etapa. El ADC de segunda etapa luego convierte el V RES incorrecto , que da como resultado un error de código.

¿Qué afecta a CER?

Ahora debería tener suficientes detalles para poder sacar algunas conclusiones sobre lo que afecta al CER. El CER depende claramente de la frecuencia de muestreo. Una frecuencia de muestreo más rápida reduce el tiempo en el que el bucle de decisiones tiene que tomar una decisión. Menos tiempo para tomar una decisión da como resultado aumentos exponenciales en la probabilidad de que el comparador no se haya asentado a tiempo.

–Matt Guibord es ingeniero de sistemas en convertidores de alta velocidad en Texas Instruments.

Incrustado

- Comentarios de C++

- C - Manejo de errores

- Comprensión del fresado CNC

- Comprender la fundición a presión

- Comprensión de los sensores

- Comprender la automatización de la prensa

- Entendiendo el hierro forjado

- Comprender la fundición centrífuga

- Comprender la fundición a presión

- Comprender el casting de inversión

- Entendiendo la soldadura de pernos