Simplificación de cadenas de señales de adquisición de datos de CA y CC

Los fenómenos de muestreo en los convertidores de analógico a digital (ADC) inducen los problemas de aliasing y contragolpe capacitivo, y para resolver estos problemas, los diseñadores utilizan filtros y amplificadores impulsores que presentan sus propios desafíos. Esto hace que lograr un rendimiento de CC y CA de precisión en áreas de aplicación de ancho de banda medio sea un desafío y los diseñadores terminan intercambiando los objetivos del sistema para lograrlo.

Este artículo describe los ADC sigma-delta (∑-Δ) de tiempo continuo que resuelven de manera inherente y espectacular los problemas de muestreo mediante la simplificación de las cadenas de señales. Eliminan la necesidad de filtros y búferes de suavizado y resuelven los errores de compensación de la cadena de señales y los problemas de deriva asociados con los componentes adicionales. Estos beneficios reducen el tamaño de la solución, facilitan el diseño de la solución y mejoran la coincidencia de fases y la latencia general del sistema. Este artículo también hace una comparación con convertidores de tiempo discreto y destaca los beneficios del sistema, así como las limitaciones del uso de ADC sigma-delta de tiempo continuo.

Conceptos básicos de muestreo

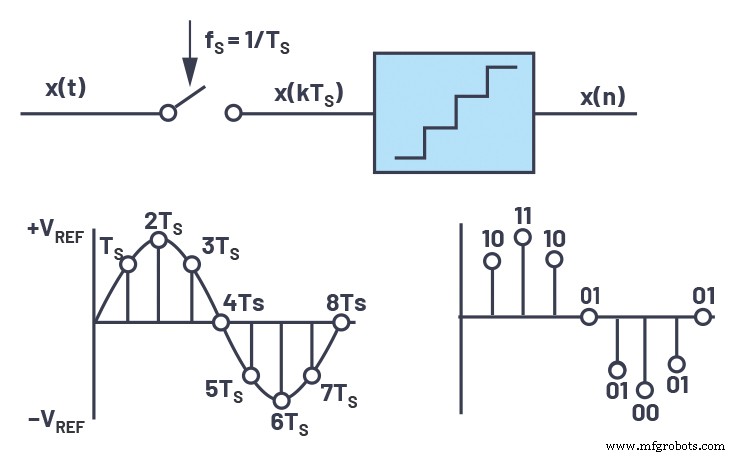

La digitalización de datos involucra los dos procesos fundamentales de muestreo y cuantificación, como se muestra en la Figura 1. El muestreo es el primer paso en el que una señal analógica variable en tiempo continuo x (t) se convierte en una señal en tiempo discreto x (n) usando muestreo frecuencia fS. El resultado está separado uniformemente por un período de 1 / TS (fS =1 / TS).

haz clic para ampliar la imagen

Figura 1. Muestreo de datos. (Fuente:Analog Devices)

El segundo paso es la cuantificación, que aproxima el valor de estas muestras de tiempo discreto a uno de los valores finitos posibles y se representa en código digital, como se muestra en la Figura 1. Esta cuantificación a un conjunto finito de valores conduce a un error en la digitalización llamado ruido de cuantificación.

El proceso de muestreo también da como resultado un aliasing, en el que vemos el repliegue de las señales de entrada y sus armónicos alrededor de la frecuencia de reloj de muestreo y retención. El criterio de Nyquist requiere que la frecuencia de muestreo sea al menos el doble de la frecuencia más alta contenida en la señal. Si la frecuencia de muestreo es menos del doble de la frecuencia máxima de la señal analógica, se producirá un fenómeno conocido como aliasing.

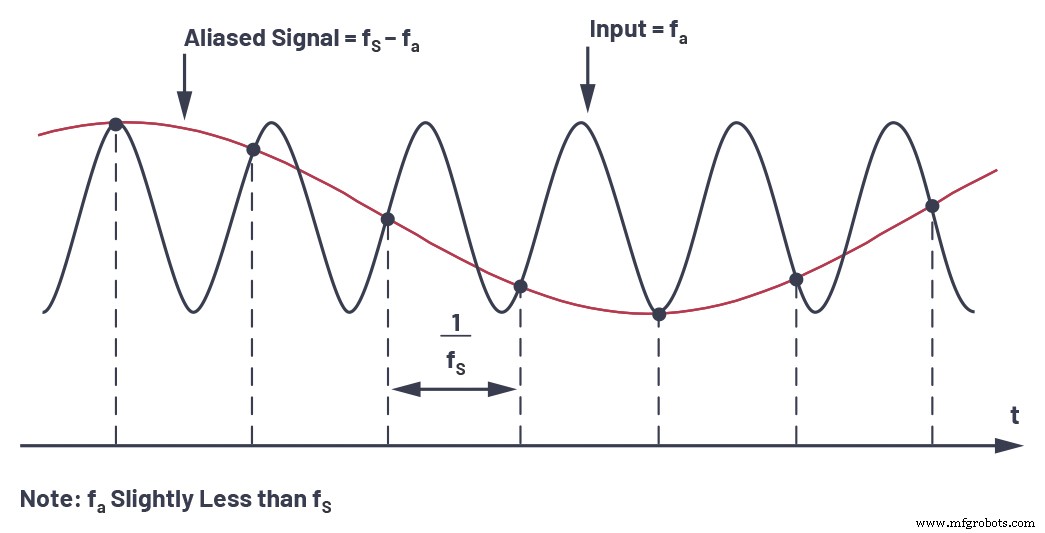

Para comprender las implicaciones del aliasing tanto en el dominio del tiempo como en el de la frecuencia, primero considere el caso de una representación en el dominio del tiempo de una onda sinusoidal de un solo tono muestreada como se muestra en la Figura 2. En este ejemplo, la frecuencia de muestreo, fS, no es al menos 2fa, pero solo un poco más que la frecuencia de entrada analógica, fa, por lo que no cumple con el criterio de Nyquist. Observe que el patrón de las muestras reales produce una onda sinusoidal con alias a una frecuencia más baja igual a fS - fa.

haz clic para ampliar la imagen

Figura 2. Aliasing:representación en el dominio del tiempo. (Fuente:Analog Devices)

haz clic para ampliar la imagen

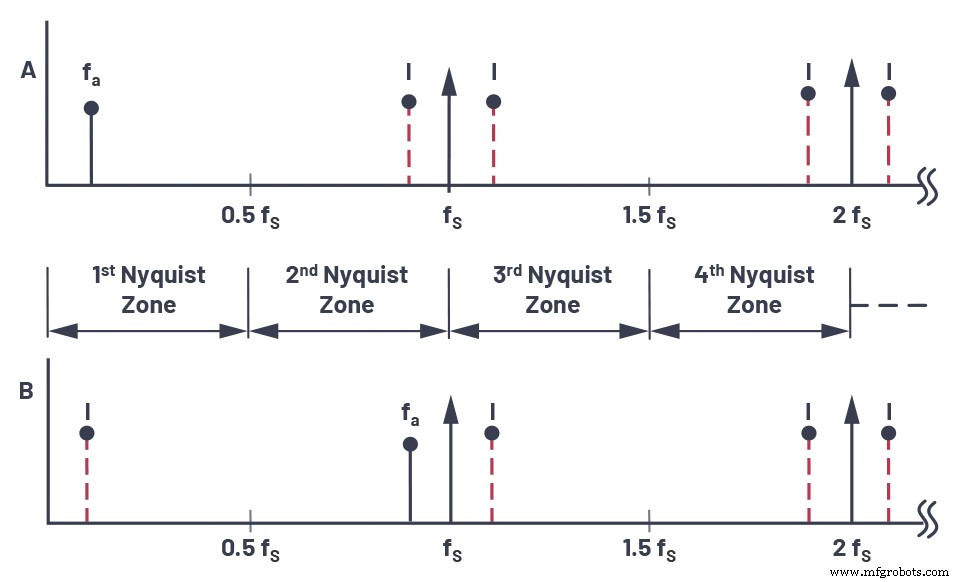

Figura 3. Aliasing:representación en el dominio de la frecuencia. (Fuente:Analog Devices)

La representación correspondiente en el dominio de frecuencia de este escenario se muestra en la Figura 3.

El ancho de banda de Nyquist se define como el espectro de frecuencia de cc a fS / 2. El espectro de frecuencia se divide en un número infinito de zonas de Nyquist, cada una de las cuales tiene un ancho igual a 0,5 fS. En la práctica, el muestreador ideal se reemplaza por un ADC seguido de un procesador FFT. El procesador FFT solo proporciona una salida de CC a fS / 2; es decir, las señales o alias que aparecen en la primera zona de Nyquist.

Considere el caso de una onda sinusoidal de frecuencia única fa muestreada a una frecuencia fS por un muestreador de impulsos ideal (consulte la Figura 1). Suponga también que fS> 2fa. La salida del dominio de frecuencia del muestreador muestra alias, o imágenes, de la señal original alrededor de cada múltiplo de fS; es decir, a frecuencias iguales a | ± KfS ± fa |, K =1, 2, 3, 4, etc.

Ahora considere el caso de una señal que está fuera de la primera zona de Nyquist en la Figura 3. La frecuencia de la señal es solo un poco menor que la frecuencia de muestreo, correspondiente a la condición que se muestra en la representación del dominio del tiempo en la Figura 2. Note que aunque el la señal está fuera de la primera zona de Nyquist, su imagen (o alias), fS - fa, cae dentro. Volviendo a la Figura 3, está claro que si aparece una señal no deseada en cualquiera de las frecuencias de imagen de fa, también ocurrirá en fa, produciendo así una componente de frecuencia falsa en la primera zona de Nyquist.

Combatir desafíos para lograr un rendimiento de precisión

Para aplicaciones de alto rendimiento, los diseñadores de sistemas deben combatir el ruido de cuantificación, el aliasing y los problemas de muestreo de entrada de condensadores conmutados que resultan del proceso de muestreo. Ambos tipos de ADC de precisión, es decir, registros de aproximación sucesivos (SAR) y ADC sigma-delta, disponibles en la industria, están diseñados utilizando técnicas de muestreo basadas en capacitores conmutados.

Ruido de cuantificación

En un ADC Nyquist ideal, el tamaño LSB del ADC determinará el ruido de cuantificación que se agrega a la entrada, mientras se realiza la conversión de analógico a digital. Este ruido de cuantificación se extiende por el ancho de banda de fS / 2. Para combatir el ruido de cuantificación, la primera técnica es el sobremuestreo, que consiste en muestrear la señal de entrada a una velocidad mucho más alta que la frecuencia de Nyquist para aumentar la relación señal-ruido (SNR) y la resolución (ENOB). En el sobremuestreo, la frecuencia de muestreo se elige N veces la frecuencia de Nyquist (2 × fIN) y, como resultado, el mismo ruido de cuantificación tiene que extenderse ahora sobre N veces la frecuencia de Nyquist. Esto también relaja los requisitos del filtro de suavizado. La relación de sobremuestreo (OSR) se define como fS / 2fIN, donde fIN es la señal BW de interés. Como pauta general, el sobremuestreo del ADC en un factor de cuatro proporciona un bit adicional de resolución o un aumento de 6 dB en el rango dinámico. El aumento de la relación de sobremuestreo da como resultado una reducción general del ruido y la mejora del rango dinámico (DR) debido al sobremuestreo es ΔDR =10log10 OSR en dB.

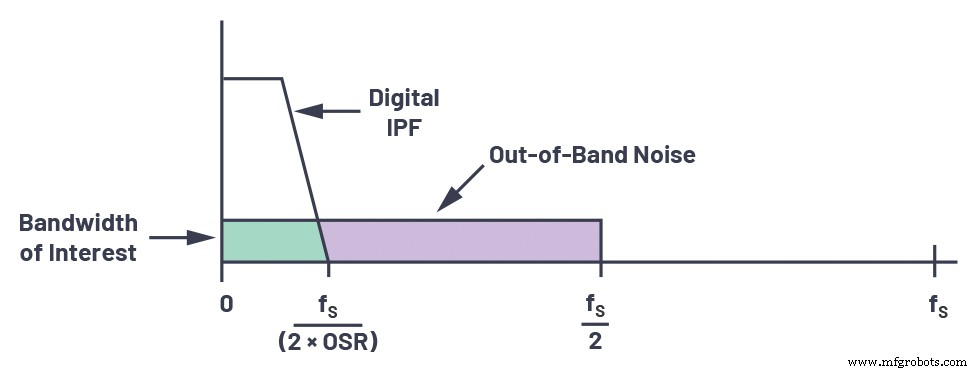

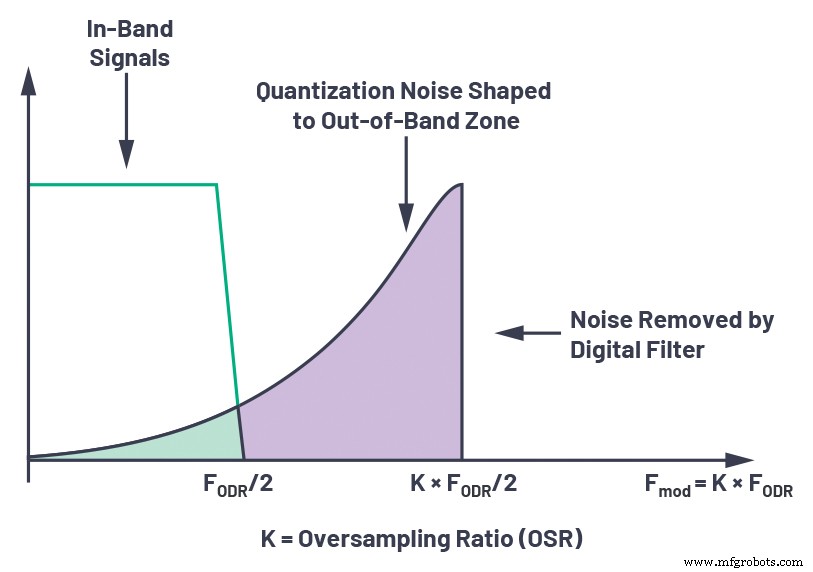

El sobremuestreo se utiliza e implementa de forma inherente junto con un filtro digital integrado y una función de diezmado. El modulador de sobremuestreo básico en el ADC sigma-delta da forma al ruido de cuantificación de tal manera que la mayor parte ocurre fuera del ancho de banda de interés, lo que da como resultado un rango dinámico general aumentado a bajas frecuencias, como se muestra en la Figura 4. El filtro de paso bajo digital (LPF ) luego elimina el ruido de cuantificación fuera del ancho de banda de interés, y el decimador reduce la tasa de datos de salida a la tasa de Nyquist.

haz clic para ampliar la imagen

Figura 4. Un ejemplo de sobremuestreo. (Fuente:Analog Devices)

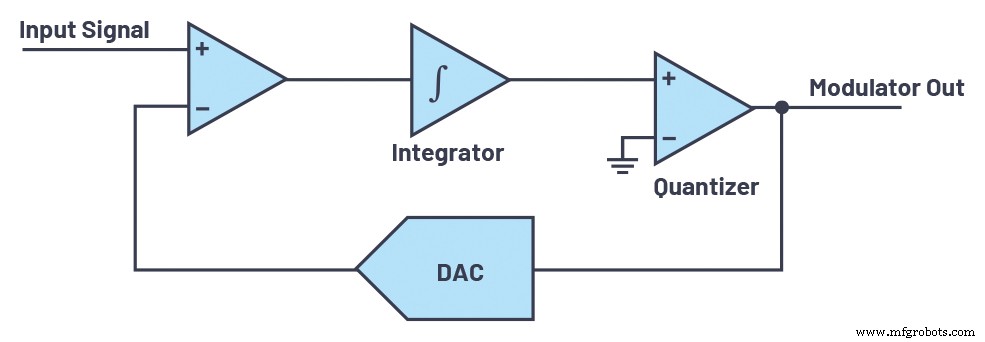

El modelado de ruido es la otra técnica para reducir el ruido de cuantificación. En los ADC sigma-delta, se utiliza un cuantificador de baja resolución (de uno a cinco bits) dentro de un bucle después del filtro de bucle. Se utiliza un DAC como retroalimentación para restar la señal cuantificada de la entrada, como se muestra en la Figura 5.

haz clic para ampliar la imagen

Figura 5. Conformación del ruido. (Fuente:Analog Devices)

El integrador seguirá sumando el error de cuantificación que da como resultado la conformación del ruido de cuantificación a frecuencias más altas, que luego se pueden filtrar utilizando un filtro digital. La Figura 6 ilustra la densidad espectral de potencia (PSD) de la salida x [n] de un ADC sigma-delta típico. La pendiente de formación de ruido depende del orden del filtro de bucle H (z) (ver Figura 11) y es (20 × n) dB / década, donde n es el orden del filtro de bucle. El ADC sigma-delta logra una alta resolución en banda mediante una combinación de modelado de ruido y sobremuestreo. El ancho de banda dentro de banda es igual a fODR / 2 (ODR significa velocidad de datos de salida). Se puede obtener una resolución más alta aumentando el orden del filtro de bucle o aumentando la relación de sobremuestreo.

haz clic para ampliar la imagen

Figura 6. Gráfico de sobremuestreo y modelado de ruido. (Fuente:Analog Devices)

Alias

Para combatir el aliasing en aplicaciones de alto rendimiento, se utilizan filtros de antialiasing de orden superior para evitar cualquier cantidad de repliegue. Un filtro antialiasing es un filtro de paso bajo que limita la banda de la señal de entrada y asegura que no haya ningún componente de frecuencia en la señal más allá del ancho de banda de interés que pueda replegarse. El rendimiento del filtro dependerá de qué tan cerca esté la señal fuera de banda de fS / 2 y la cantidad de atenuación requerida.

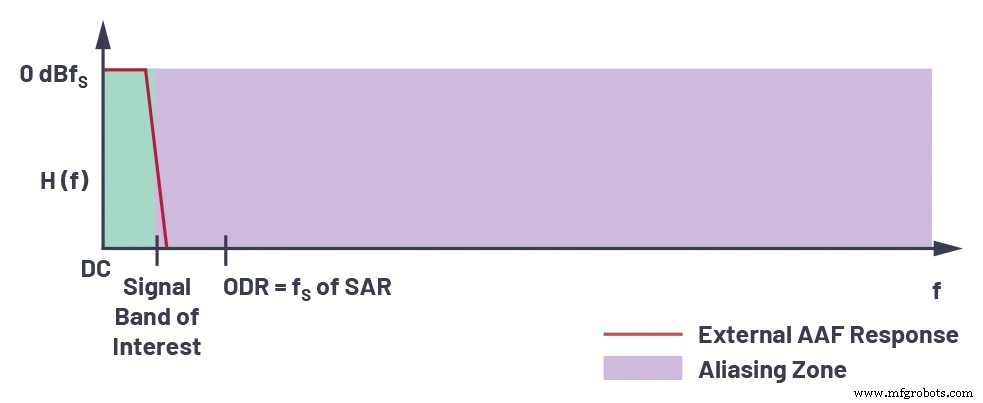

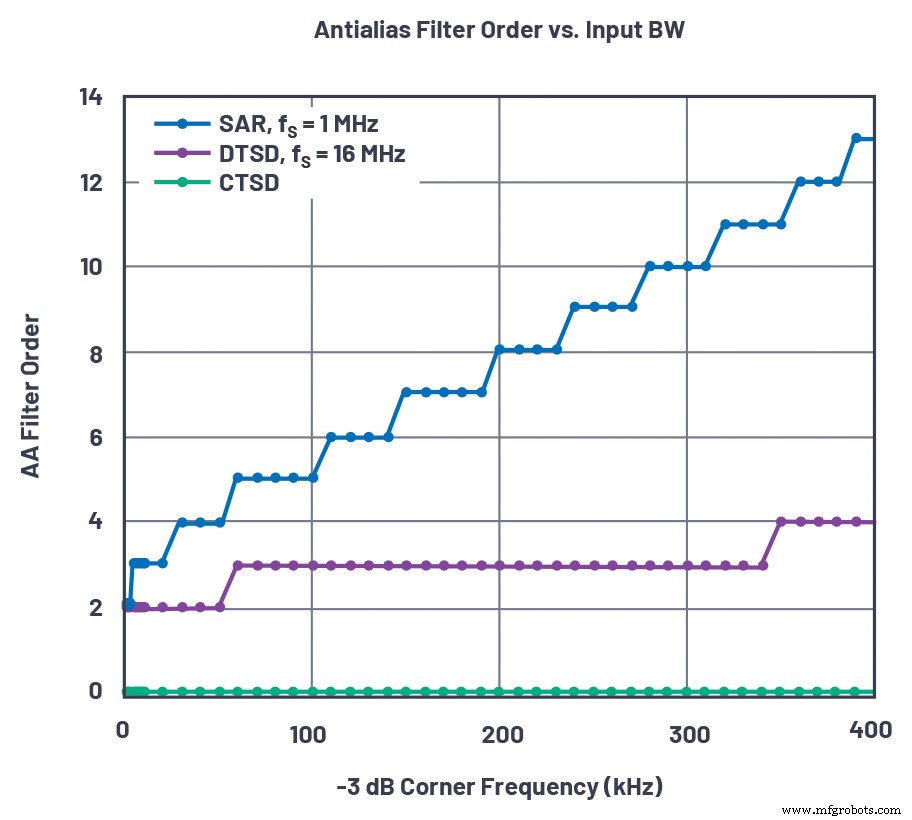

Para los ADC de SAR, la brecha entre la señal de entrada BW y la frecuencia de muestreo no es enorme, por lo que necesitamos un filtro de orden superior que requiera un diseño de filtro de orden superior complejo con más potencia y más distorsión. Por ejemplo, si un SAR de velocidad de muestreo de 200 kSPS tiene un BW de entrada de 100 kHz, el filtro antialiasing deberá rechazar una señal de entrada de> 100 kHz para asegurarse de que no haya aliasing. Esto requiere un filtro de orden muy alto. La Figura 7 muestra la demanda de la curva pronunciada.

haz clic para ampliar la imagen

Figura 7. Requisito de alias. (Fuente:Analog Devices)

Si se elige una velocidad de muestreo de 400 kSPS para relajar el orden del filtro, el rechazo es necesario para una frecuencia de entrada> 300 kHz. El aumento de la velocidad de muestreo aumentará la potencia, y para el doble de velocidad, la potencia también se duplicará. Un sobremuestreo adicional a costa de energía relajará aún más el requisito del filtro antialiasing, ya que la frecuencia de muestreo es mucho más alta que el BW de entrada.

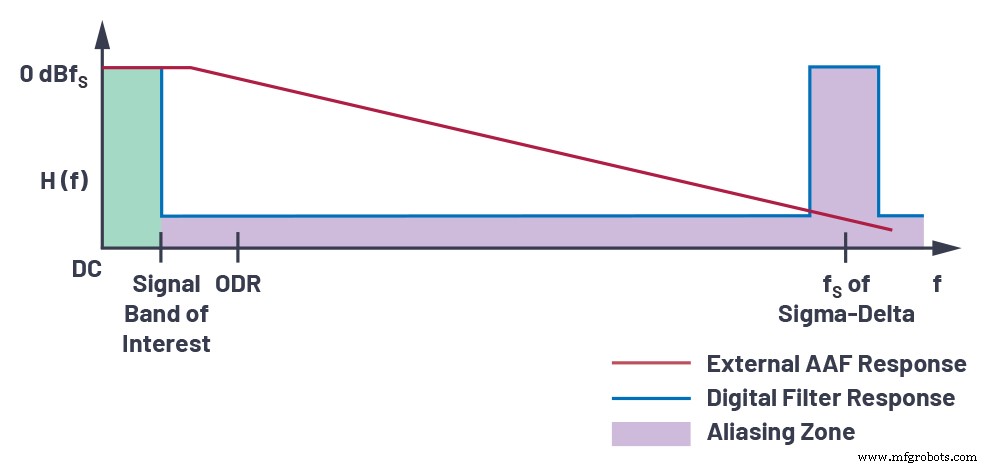

En los ADC sigma-delta, la entrada se sobremuestrea a un OSR mucho más alto, por lo que el requisito del filtro antialiasing se relaja ya que la frecuencia de muestreo es mucho más alta que el BW de entrada, como se muestra en la Figura 8.

haz clic para ampliar la imagen

Figura 8. Requisito de filtro antialiasing en sigma-delta. (Fuente:Analog Devices)

La Figura 9 da una idea de la complejidad de AAF para las arquitecturas SAR y sigma-delta de tiempo discreto (DTSD). Si tomamos un ancho de banda de entrada de –3 dB de 100 kHz para lograr una atenuación de 102 dB a la frecuencia de muestreo fS, se necesitará un filtro antialiasing de segundo orden para un ADC DTSD mientras que obtener la misma atenuación en fS requerirá un filtro de quinto orden usando un SAR ADC.

Para un ADC sigma-delta de tiempo continuo (CTSD), la atenuación es inherente, por lo que no necesitamos ningún filtro antialiasing.

haz clic para ampliar la imagen

Figura 9. Requisito de filtro AAF para varias arquitecturas. (Fuente:Analog Devices)

Estos filtros pueden ser un problema para los diseñadores de sistemas, y tienen que optimizarlos para la caída que proporcionan en la banda de interés y proporcionar el mayor rechazo posible. También agregan muchos otros errores como compensación, ganancia, error de fase y ruido al sistema, reduciendo así su rendimiento.

Además, los ADC de alto rendimiento son de naturaleza diferencial, por lo que necesitamos el doble de componentes pasivos. Para obtener una mejor coincidencia de fase en aplicaciones multicanal, todos los componentes de la cadena de señal deben coincidir bien. Como resultado, se requieren componentes con una tolerancia más estricta.

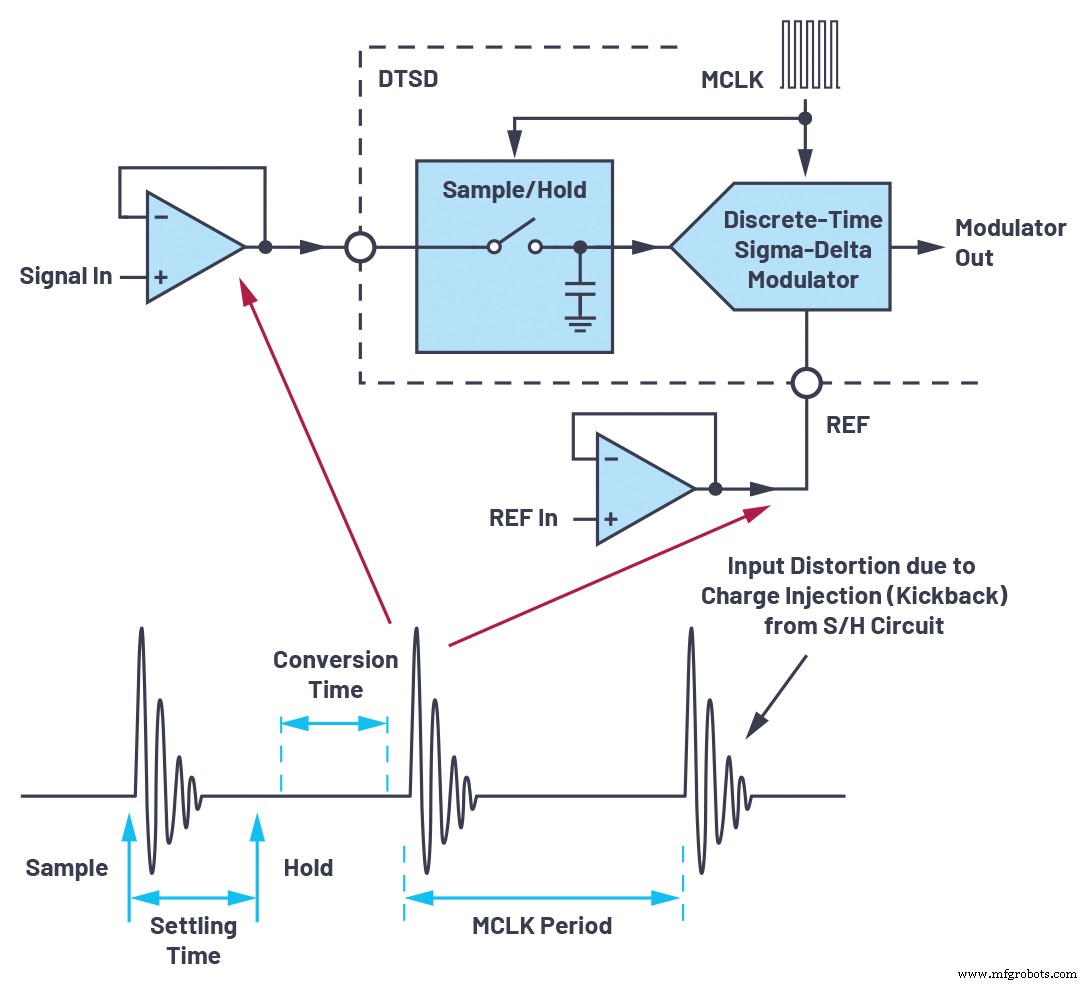

Entrada de condensador conmutada

El muestreo de entrada de condensador conmutado se basa en el tiempo de establecimiento de la entrada muestreada en un condensador, lo que crea una demanda de corriente transitoria de carga / descarga cuando el interruptor de muestreo se enciende / apaga. Esto se llama retroceso en la entrada y requiere un amplificador de excitación de entrada que pueda soportar estas corrientes transitorias. Además, se requiere que la entrada se establezca al final del tiempo de muestreo y la precisión de la entrada muestreada determina el rendimiento del ADC, lo que implica que el amplificador de conducción debe establecerse rápidamente después del evento de contragolpe. Esto lleva a la necesidad de un controlador de gran ancho de banda que pueda soportar un asentamiento rápido y absorber el retroceso de la operación del capacitor conmutado. En las entradas de condensadores conmutados, siempre que el muestreo está activado, el controlador tiene que suministrar inmediatamente la carga para el condensador de retención. Este aumento repentino de la corriente solo se puede proporcionar a tiempo si el controlador tiene suficientes capacidades de ancho de banda. Debido a los parásitos del interruptor, habrá un contragolpe sobre el conductor en el momento del muestreo. Si el retroceso no se estabiliza antes del siguiente muestreo, resultará en un error al muestrear, corrompiendo así la entrada de ADC.

haz clic para ampliar la imagen

Figura 10. Muestreo de retroceso. (Fuente:Analog Devices)

La Figura 10 muestra el retroceso en el DTSD ADC. Si, por ejemplo, la frecuencia de muestreo es de 24 MHz, la señal de datos debe establecerse dentro de los 41 ns. Dado que la referencia también es una entrada de condensador conmutado, también se necesita un búfer de gran ancho de banda en el pin de entrada de referencia. Estos búferes de referencia y señal de entrada aumentan el ruido y reducen el rendimiento general de la cadena de señal. Además, los componentes de distorsión del controlador de la señal de entrada (alrededor de la frecuencia S&H) aumentan aún más los requisitos de suavizado. Además, con las entradas de condensador conmutadas, los cambios en la velocidad de muestreo darán como resultado una corriente de entrada variable. Esto podría resultar en el reajuste del sistema para reducir el error de ganancia generado en el controlador o en la etapa anterior mientras se conduce el ADC.

ADC Sigma-Delta de tiempo continuo

Un ADC CTSD es una arquitectura ADC sigma-delta alternativa que aprovecha principios como sobremuestreo y modelado de ruido, pero que tiene un medio alternativo para implementar la operación de muestreo que ofrece beneficios significativos al sistema.

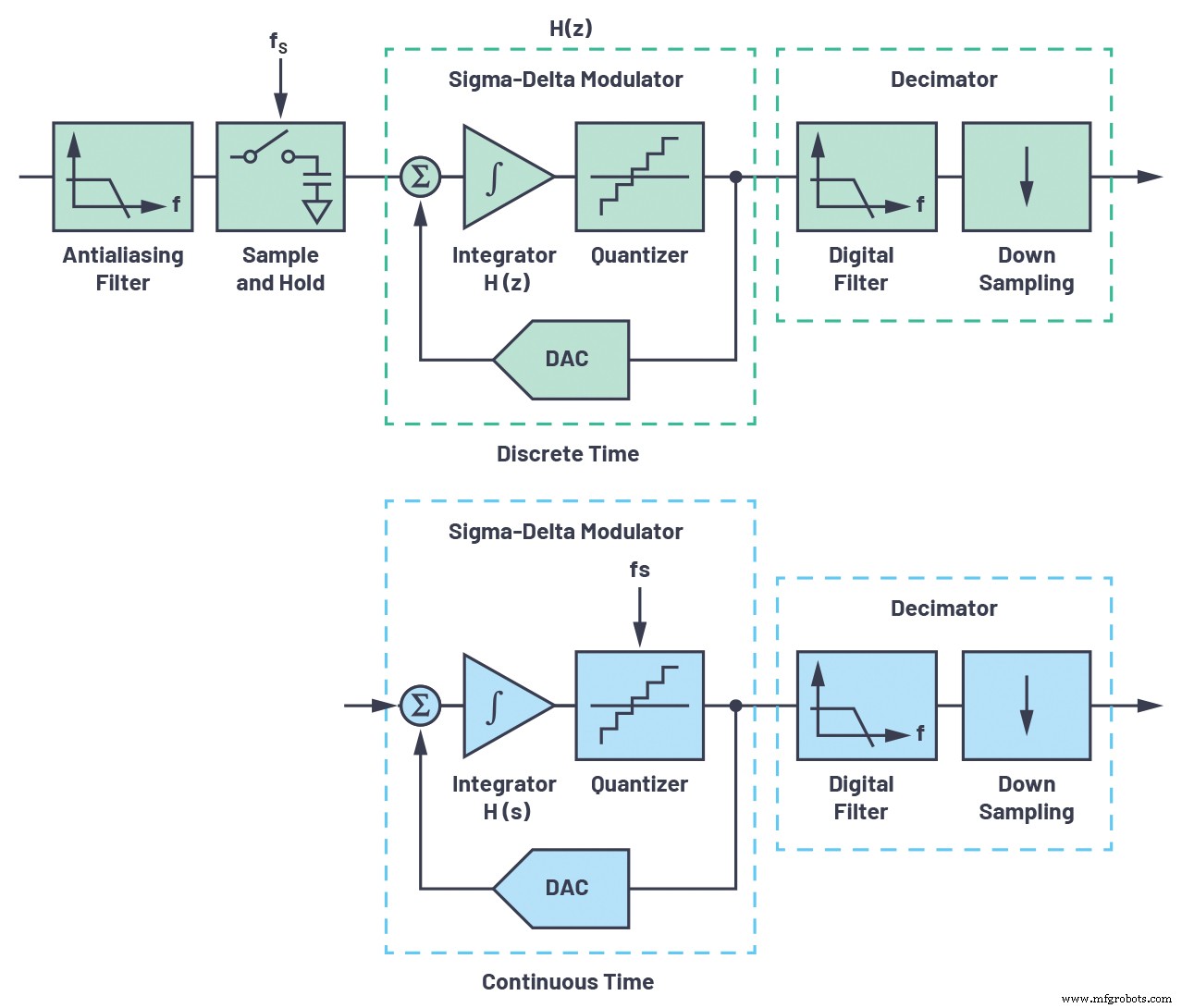

La Figura 11 muestra una comparación de una arquitectura DTSD y una arquitectura CTSD. Como vemos en la arquitectura DTSD, la entrada se muestrea antes del bucle. El filtro de bucle H (z) es discreto en el tiempo y se implementa mediante integradores de condensadores conmutados. El DAC de retroalimentación también se basa en condensadores conmutados. Como hay muestreo en la entrada, lo que resultará en un problema de alias de f S , se requiere un filtro antialiasing adicional en la entrada antes de muestrearla.

haz clic para ampliar la imagen

Figura 11. Esquemas de bloques modulares en tiempo discreto y tiempo continuo. (Fuente:Analog Devices)

CTSD no tiene muestreador en la entrada. Más bien, se muestrea en el cuantificador dentro del bucle. El filtro de bucle ahora es de tiempo continuo utilizando integradores de tiempo continuo, y también lo es el DAC de retroalimentación. Similar a la cuantificación que se forma, el aliasing debido al muestreo también se forma. Esto da como resultado un ADC casi sin muestreo, lo que crea una clase propia.

La frecuencia de muestreo del CTSD es fija, a diferencia del DTSD, donde la frecuencia de muestreo del modulador se puede escalar fácilmente. Además, se sabe que los ADC CTSD son menos tolerantes a la fluctuación que los equivalentes de condensadores conmutados. Los osciladores de cristal o CMOS disponibles en el mercado proporcionan relojes de baja fluctuación a los ADC de forma local, lo que ayuda a evitar la transmisión de una frecuencia de baja fluctuación a través del aislamiento y reduce la EMC.

Los dos beneficios principales de CTSD son el rechazo de alias inherente y las entradas resistivas para señales y referencia.

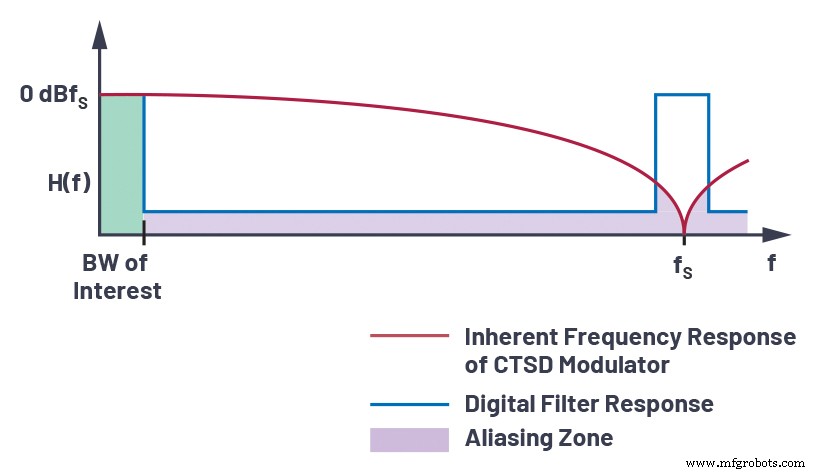

Antialiasing inherente

Mover el cuantificador dentro del bucle da como resultado un rechazo de alias inherente. Como se muestra en la Figura 12, la señal de entrada pasa a través del filtro de bucle antes de ser muestreada y el error de repliegue (alias), que se introduce en el cuantificador, también ve este filtro. La señal y el error de alias verán la misma función de transferencia de ruido que el bucle sigma-delta, y ambos tendrán una forma de ruido similar al ruido de cuantificación en arquitecturas sigma-delta. Por lo tanto, la respuesta de frecuencia del bucle CTSD rechaza naturalmente las señales de entrada alrededor de múltiplos enteros de la frecuencia de muestreo, actuando como un filtro antialiasing.

haz clic para ampliar la imagen

Figura 12. Respuesta de frecuencia de un modulador CTSD. (Fuente:Analog Devices)

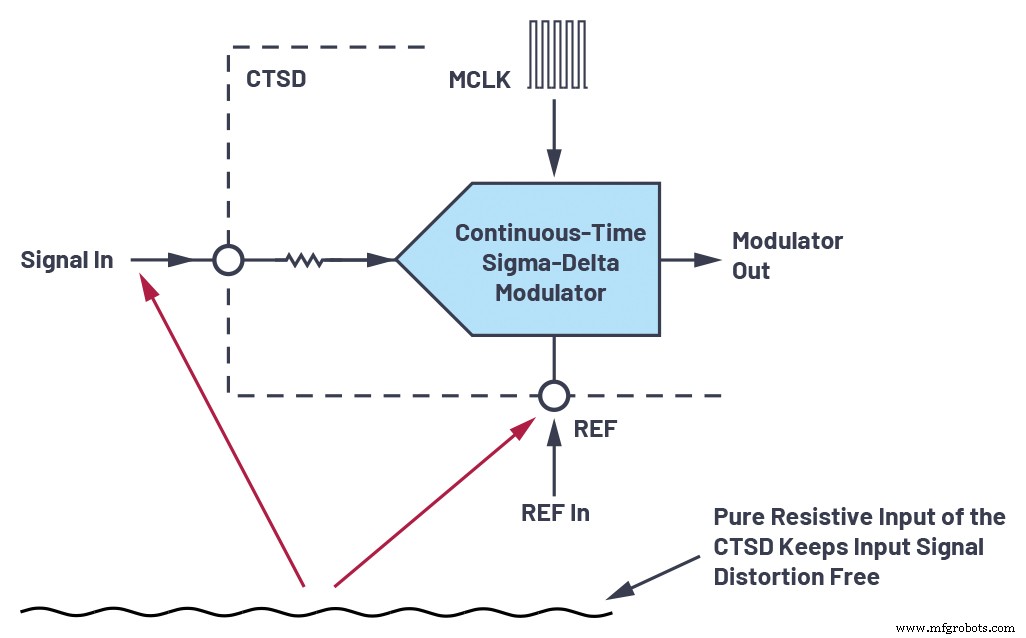

Entrada resistiva

Tener entradas resistivas en las entradas de señal y referencia hace que sea más fácil de manejar que las configuraciones de muestreo y retención. Con entradas resistivas constantes, no hay retroceso y el controlador se puede quitar por completo. La entrada está libre de distorsiones, como se muestra en la Figura 13. Y dado que la resistencia de entrada es constante, también se elimina el reajuste del sistema para errores de ganancia.

haz clic para ampliar la imagen

Figura 13. Ajuste de entrada para CTSD. (Fuente:Analog Devices)

Las entradas analógicas pueden ser bipolares aunque el ADC tenga alimentación unipolar. Esto puede eliminar la necesidad de cambiar de nivel desde un extremo frontal bipolar al ADC. El rendimiento de CC del ADC puede no ser el mismo, ya que la resistencia de entrada ahora tiene una corriente dependiente del modo común de entrada, así como la corriente de entrada.

La carga de referencia también es resistiva, lo que reduce el retroceso de conmutación, por lo que no se requiere un búfer de referencia separado. La resistencia para un filtro de paso bajo se puede hacer en el chip para que pueda seguir junto con la carga resistiva en el chip (ya que podrían ser del mismo material), para reducir la deriva de temperatura del error de ganancia.

La arquitectura CTSD no es nueva, pero las megatendencias en los mercados industriales y de instrumentación exigen un rendimiento de precisión de CC y CA con anchos de banda más altos. Además, los clientes prefieren un diseño de plataforma única que se adapte a la mayoría de sus soluciones para reducir su tiempo de comercialización.

La arquitectura CTSD ha sido la opción elegida en un amplio conjunto de aplicaciones que van desde audio de alto rendimiento hasta la interfaz de RF de los teléfonos celulares debido a una serie de ventajas sobre otros tipos de ADC. Los beneficios incluyen una mayor facilidad para la integración y un bajo consumo de energía, pero también, y posiblemente más importante, porque el uso de un CTSD resuelve una serie de problemas importantes a nivel del sistema. Debido a una serie de deficiencias tecnológicas, el uso de CTSD se ha limitado anteriormente a la frecuencia de audio / ancho de banda relativos y un rango dinámico más bajo. Por lo tanto, los convertidores de velocidad Nyquist de alto rendimiento, como los ADC de aproximación sucesiva y los convertidores DTSD sobremuestreados, han sido la solución principal para aplicaciones de precisión, alto rendimiento / ancho de banda medio.

Sin embargo, los avances tecnológicos recientes han permitido superar muchas limitaciones. Por ejemplo, el AD7134 de Analog Devices admite ADC de ancho de banda de CC a 400 kHz de alta precisión basado en CTSD que logra especificaciones de rendimiento sustancialmente más altas, al tiempo que proporciona precisión de CC y, a su vez, permite la solución para una serie de problemas importantes a nivel de sistema en alta aplicaciones de instrumentación de rendimiento. El AD7134 también integra un convertidor de frecuencia de muestreo asíncrono (ASRC) que proporciona datos a velocidades de datos variables derivadas de la velocidad de muestreo fija de CTSD. La tasa de datos de salida puede ser independiente de la frecuencia de muestreo del modulador y puede permitir el uso exitoso de ADC CTSD para diferentes rendimientos granulares. La flexibilidad para cambiar la tasa de datos de salida a nivel granular también permite a los usuarios utilizar un muestreo coherente.

El rechazo de alias inherente elimina la necesidad de un filtro de suavizado, lo que da como resultado menos componentes y un tamaño de solución más pequeño. Más importante aún, los problemas de rendimiento que vienen junto con un filtro de suavizado como caída, errores como compensación, ganancia y error de fase y ruido en el sistema ya no están presentes. Un filtro antialiasing también aumenta significativamente la latencia general en la cadena de señal dependiendo del rechazo necesario. La eliminación del filtro elimina este retraso por completo, lo que permite una conversión de precisión en aplicaciones de bucle de control digital ruidosas.

Sin filtro antialiasing a nivel del sistema, la coincidencia de fases en sistemas multicanal se puede mejorar enormemente. Esto es especialmente útil en aplicaciones que exigen un bajo desajuste de canal a canal, como monitoreo de vibraciones, mediciones de potencia, módulos de adquisición de datos y sonar. Debido a su acción de filtrado inherente, los ADC CTSD también son inmunes a cualquier tipo de interferencia a nivel del sistema, así como desde el propio IC. En DTSD ADC y SAR ADC, se debe tener cuidado de que haya menos interferencia cuando el ADC esté muestreando. Además, habría inmunidad a la interferencia en las líneas de suministro de energía debido a la acción de filtrado inherente. Con entradas analógicas resistivas constantes y entradas de referencia, el requisito del controlador también se puede eliminar por completo. Nuevamente, esto aborda problemas de rendimiento como errores como compensación, ganancia, error de fase y ruido en el sistema que ya no existen.

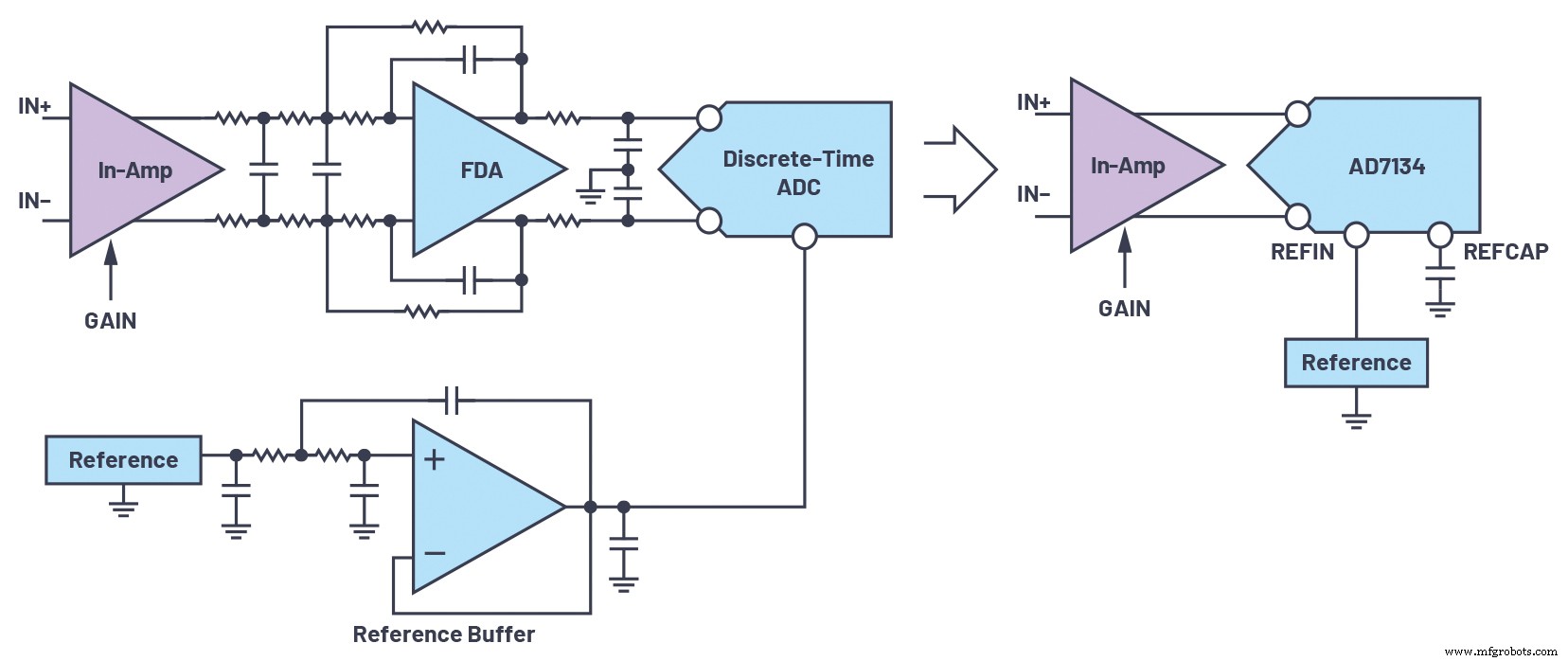

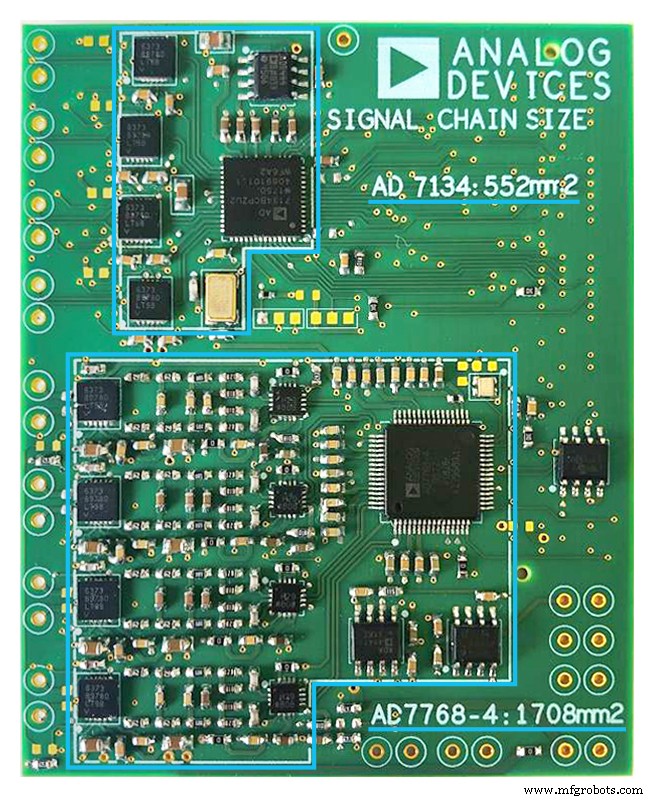

La lucha por lograr el rendimiento de precisión es mínima ya que la cantidad de elementos diseñados se reduce significativamente. Esto da como resultado un tiempo de diseño más rápido, un tiempo de comercialización más rápido para los clientes, una administración más sencilla de la lista de materiales y una mayor confiabilidad. La eliminación de un filtro de suavizado, un controlador y un búfer de referencia reducirá significativamente el área de la placa del sistema. Se puede utilizar un amplificador de instrumentación para controlar directamente el ADC. Por ejemplo, con el AD7134, como es un ADC de entrada diferencial únicamente, se puede utilizar como controlador un amplificador de entrada diferencial como el LTC6373. La comparación en la Figura 14 muestra la cadena de señal para una cadena de señal basada en tiempo discreto y una cadena de señal basada en tiempo continuo. Nuestro experimento muestra un ahorro de área del 70% en comparación con una cadena de señal equivalente basada en tiempo discreto, lo que la convierte en una excelente opción para aplicaciones multicanal de alta densidad.

En conclusión, este enfoque ofrece una reducción significativa del tamaño del sistema, simplifica el diseño de la cadena de señales, hace que el sistema sea más robusto y reduce el tiempo total de comercialización con un diseño sencillo sin intercambiar los parámetros de rendimiento exigidos por las aplicaciones de instrumentación de precisión.

haz clic para ampliar la imagen

Figura 14. Comparación de la cadena de señales basada en tiempo discreto (izquierda) y basada en tiempo continuo (derecha). (Fuente:Analog Devices)

haz clic para ampliar la imagen

Figura 15. Comparación de tamaño de la cadena de señales en tiempo discreto y en tiempo continuo. (Fuente:Analog Devices)

Referencias

Kester, Walt. "MT-002:Qué significa el criterio de Nyquist para el diseño de su sistema de datos muestreados". Analog Devices, Inc., 2009.

Pavan, Shanti. “Rechazo de alias de moduladores Δ∑ de tiempo continuo con DAC de retroalimentación de capacitor conmutado”. Transacciones IEEE en circuitos y sistemas I:artículos regulares , Vol. 58, No. 2, febrero de 2011.

Schreier, Richard y Gabor C. Temes. Comprensión de los convertidores de datos Delta-Sigma. John Wiley and Sons, 2005.

Agradecimientos

El autor desea agradecer a Abhilasha Kawle, Avinash Gutta y Roberto Maurino por su apoyo en este artículo.

Incrustado

- Términos y conceptos de la memoria digital

- Variables de C# y tipos de datos (primitivos)

- Conversión de tipos de Python y conversión de tipos

- Semáforos:servicios públicos y estructuras de datos

- Grupos de indicadores de eventos:servicios públicos y estructuras de datos

- Apacer:Lanzamiento de las tarjetas CV110-SD y CV110-MSD en todo el mundo

- Swissbit:soluciones de seguridad basadas en hardware para proteger datos y dispositivos

- Hiperconvergencia y almacenamiento secundario:Parte 2

- Construyendo una IA responsable y confiable

- Blockchain y cadenas de suministro:liberando el potencial

- El significado de los tejidos de datos y cómo benefician a las cadenas de suministro