Cómo detener la simulación en un banco de pruebas VHDL

¿Cómo se detiene el simulador VHDL cuando se completa la simulación? Hay varias maneras de hacer eso. En este artículo, examinaremos las formas más comunes de finalizar una ejecución exitosa del banco de pruebas.

El código VHDL que se presenta aquí es universal y debería funcionar en cualquier simulador VHDL compatible. Para los métodos que involucran Tcl, enumeraré los comandos para los simuladores ModelSim y Vivado.

Puede descargar un proyecto de ejemplo con los cuatro bancos de pruebas diferentes de este artículo si tiene instalado ModelSim. ¡Ingrese su dirección de correo electrónico en el siguiente formulario para recibir el archivo Zip!

Uso de finalizar procedimiento

El VHDL terminar El procedimiento es mi forma favorita de detener un banco de pruebas VHDL que se completa sin errores. Debe importar "finalizar" desde el paquete STD.ENV, y debe compilar el banco de pruebas en VHDL-2008 o posterior para usarlo.

El siguiente código finaliza la simulación cuando llegamos a la última línea del proceso del secuenciador del banco de pruebas.

use std.env.finish; ... SEQUENCER_PROC : process begin -- Replace this line with your testbench logic wait until stop_condition; report "Calling 'finish'"; finish; end process;

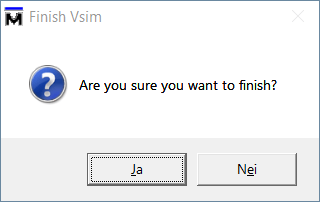

Tenga en cuenta que finalizar sale de la simulación por defecto. Si está ejecutando ModelSim en la versión GUI, aparecerá una ventana emergente que dice "¿Está seguro de que desea terminar?". Si hace clic en Sí, ModelSim se cerrará.

Probablemente eso no sea lo que quieres. Afortunadamente, podemos evitar este comportamiento agregando la opción "-onfinish stop" al comando vsim, como se muestra a continuación. Al hacerlo, el terminar El procedimiento se comportará de la misma manera que el stop procedimiento que discutiremos en la siguiente sección de este artículo.

vsim -onfinish stop work.using_finish_tb

Una ventaja de usar finish es que puede usar el comportamiento predeterminado al simular en modo por lotes. Si está utilizando secuencias de comandos para iniciar la simulación, desea devolver el control a la secuencia de comandos de llamada después de que finalice la simulación.

El siguiente ejemplo muestra un banco de pruebas usando el finalizar procedimiento iniciado en el modo por lotes de ModelSim en Linux. Una vez que se completa el banco de pruebas, el simulador se cierra y, en la última línea, regresamos al shell de Linux.

jonas@ubuntu:~/stop_tb$ vsim -c -do 'vsim work.using_finish_tb; run -all' Reading pref.tcl # 10.5b # vsim work.using_finish_tb # vsim work.using_finish_tb # Start time: 22:58:31 on Jun 21,2020 # Loading std.standard # Loading std.env(body) # Loading work.using_finish_tb(sim) # run -all # ** Note: Calling 'finish' # Time: 1 ms Iteration: 0 Instance: /using_finish_tb # End time: 22:58:31 on Jun 21,2020, Elapsed time: 0:00:00 # Errors: 0, Warnings: 8 jonas@ubuntu:~/stop_tb$

El VHDL terminar El procedimiento se define en el paquete ENV estándar. Como podemos ver en el código a continuación, viene en dos sabores sobrecargados. Está la versión sin ningún parámetro, que es la que siempre uso, y hay otra que toma un estado entero como entrada constante.

procedure FINISH (STATUS: INTEGER); procedure FINISH;

Se podría pensar que el número entero de estado se convierte en el código de salida cuando se llama desde un shell de Linux, pero ese no es el caso, al menos no con ModelSim. El problema de usar este código de estado es que lo que hace depende del simulador. La redacción en el estándar VHDL-2008 es "el valor del parámetro STATUS puede usarse de una manera definida por el simulador de host “.

Sin embargo, puede controlar el valor del código de salida de Linux en ModelSim usando el comando Tcl exit -code <value> , pero esa es otra historia.

Uso de la stop procedimiento

El VHDL detener procedimiento hace que la simulación se detenga. Eso puede ser útil si desea examinar los valores de la señal manualmente o incluso continuar con la simulación más tarde. El simulador lo trata como un punto de interrupción.

El siguiente ejemplo muestra cómo importar y usar el stop procedimiento.

use std.env.stop; ... SEQUENCER_PROC : process begin -- Replace this line with your testbench logic wait until stop_condition; report "Calling 'stop'"; stop; end process;

Un problema con el uso de stop en configuraciones basadas en scripts es que no sale de la simulación. En lugar de devolver el control a la persona que llama, ModelSim abre un shell de comando Tcl, lo que hace que el script de llamada se cuelgue indefinidamente.

La siguiente lista muestra el resultado de ejecutar el banco de pruebas que usa el detener procedimiento en modo por lotes. Después de que se detiene la simulación, todavía estamos en ModelSim. Para salir del shell Tcl, tendríamos que teclear “exit”.

jonas@ubuntu:~/stop_tb$ vsim -c -do 'vsim work.using_stop_tb; run -all' Reading pref.tcl # 10.5b # vsim work.using_stop_tb # vsim work.using_stop_tb # Start time: 22:58:56 on Jun 21,2020 # Loading std.standard # Loading std.env(body) # Loading work.using_stop_tb(sim) # run -all # ** Note: Calling 'stop' # Time: 1 ms Iteration: 0 Instance: /using_stop_tb # Break in Process SEQUENCER_PROC at ~/stop_tb/src/using_stop_tb.vhd line 23 # Stopped at ~/stop_tb/src/using_stop_tb.vhd line 23 VSIM 3>

Al igual que el acabado procedimiento, detener requiere VHDL-2008 o posterior. Como se muestra a continuación, existe una versión sobrecargada del procedimiento. Toma un valor de estado entero, pero el comportamiento varía entre los simuladores.

procedure STOP (STATUS: INTEGER); procedure STOP;

Uso de la afirmación palabra clave

Una forma universal y segura de detener un banco de pruebas VHDL es crear una falla de aserción. Esa fue la primera forma en que alguien me enseñó a finalizar la simulación cuando estaba aprendiendo VHDL en la universidad.

No se necesitan importaciones adicionales y funciona en todas las versiones de VHDL. Solo asegúrese de usar el nivel de gravedad fallo , como se muestra en el siguiente ejemplo.

SEQUENCER_PROC : process begin -- Replace this line with your testbench logic wait until stop_condition; assert false report "Test: OK" severity failure; end process;

¿Y por qué odio esta forma de detener una simulación exitosa?

En primer lugar, parece extraño y confuso ver la impresión del ejemplo anterior:

# ** Failure: Test: OK

Dice que es un "fallo", pero la prueba es "OK" al mismo tiempo. Eso es porque afirmar se supone que la declaración indica una condición de error y no la finalización exitosa de la simulación.

El otro problema molesto que se me ocurre es que se vuelve difícil averiguar mediante programación si la simulación fue exitosa.

La mayoría de los profesionales de VHDL inician las simulaciones desde un script en algún momento, por ejemplo, como parte de un esquema de prueba de regresión más amplio. Si el banco de pruebas también se detiene en una falla de aserción cuando no hay nada malo, no podemos usar eso como un marcador para determinar la salud del módulo VHDL.

Uso de Tcl

El último método para detener la simulación que voy a cubrir es usar Tcl en combinación con VHDL. En lugar de detener el banco de pruebas desde el archivo VHDL, configuramos una señal VHDL regular cuando es hora de detenerse. Y de antemano, configuramos el simulador para escuchar un cambio en esta señal de disparo.

Lee también:

Por qué necesitas aprender Tcl

Mire el ejemplo a continuación, que establece una señal llamada stop_condition cuando todos los casos de prueba se hayan completado.

signal stop_condition : boolean;

begin

-- Replace this line with your DUT instantiation

stop_condition <= not stop_condition after 1 ms;

SEQUENCER_PROC : process

begin

-- Put your testbench logic here

-- Pause this process forever after all tests are done

wait;

end process;

Puede poner en reposo cualquier proceso de banco de pruebas que haya hecho su trabajo con una sola espera declaración antes del finalizar proceso etiqueta. Eso evitará que se reinicie. El código Tcl para detener realmente la simulación difiere entre simuladores.

En ModelSim

Lo que queremos es detener el banco de pruebas cuando stop_condition La señal VHDL se vuelve verdadera . Podemos hacerlo configurando una devolución de llamada en Tcl antes de ejecutar el banco de pruebas VHDL.

De acuerdo con el Manual de referencia de comandos de ModelSim, podemos lograrlo usando Tcl when dominio. En el código Tcl a continuación, registramos dicha devolución de llamada y luego iniciamos el simulador usando run -all .

when {stop_condition} {

stop

echo "Test: OK"

}

run -all

Tenga en cuenta que el código entre llaves no se ejecutará hasta que ocurra la devolución de llamada. Cuando el código VHDL cambia la stop_condition señal a verdadero , el simulador hará una pausa y ejecutará las dos líneas. En el ejemplo, detenemos la simulación e imprimimos "Test:OK" en la consola. También podría tener una salida de Tcl comando allí, que cerraría el simulador, al igual que el VHDL finalizar procedimiento.

# vsim # Start time: 22:31:11 on Jun 22,2020 # Loading std.standard # Loading work.using_tcl_tb(sim) # Test: OK # Simulation stop requested.

La lista anterior muestra el resultado impreso en la consola ModelSim cuando se completa el banco de pruebas Tcl / VHDL. Si quieres probarlo en tu computadora, utiliza el siguiente formulario para descargar el proyecto ModelSim con todos los ejemplos de este artículo.

En Vivo

De acuerdo con la Guía de referencia de comandos Tcl de Vivado Design Suite, podemos registrar una devolución de llamada Tcl usando add_condition dominio. El siguiente código muestra el equivalente de Xilinx para la versión de ModelSim discutida anteriormente.

set sim_fileset sim_1

launch_simulation -simset [get_filesets $sim_fileset]

add_condition -notrace stop_condition {

stop

puts "Test: OK"

}

run all

El -no-trace switch evita que las líneas de código en la función de devolución de llamada se reproduzcan en el terminal mientras se ejecutan. Prefiero no tener el desorden adicional en la consola.

La siguiente lista muestra un extracto de la simulación que se ejecuta en la consola del simulador Vivado.

launch_simulation: ...

add_condition -notrace stop_condition {

stop

puts "Test: OK"

}

condition8

run all

Test: OK

Reflexiones finales

Como ha visto, hay muchas formas de terminar una simulación VHDL. Sin embargo, el único que uso es el VHDL-2008 finish procedimiento.

Todos los simuladores son compatibles con VHDL-2008 por ahora, y no necesita compilar el código RTL en 2008, solo el banco de pruebas. El finalizar El procedimiento es el método más portátil y le permite detener el simulador cuando se ejecuta en modo GUI, o salir cuando se ejecuta en modo por lotes. Exactamente el comportamiento que deseo la mayor parte del tiempo.

Pero hay ventajas en los métodos Tcl que están fuera del alcance de este artículo. Cuando haya pausado el simulador en la devolución de llamada de Tcl, puede hacer mucho más que simplemente detener el simulador y salir. Puede examinar las señales VHDL e incluso manipularlas usando Tcl, mientras está en la devolución de llamada. Eso es verificación usando Tcl.

VHDL

- Cómo crear una lista de cadenas en VHDL

- Cómo crear un banco de pruebas controlado por Tcl para un módulo de bloqueo de código VHDL

- Cómo crear un controlador PWM en VHDL

- Cómo generar números aleatorios en VHDL

- Banco de pruebas interactivo usando Tcl

- Cómo crear un banco de pruebas de autocomprobación

- Cómo crear una lista enlazada en VHDL

- Cómo usar un procedimiento en un proceso en VHDL

- Cómo usar una función impura en VHDL

- Cómo usar una función en VHDL

- Cómo detener el óxido