Flujo de diseño ASIC

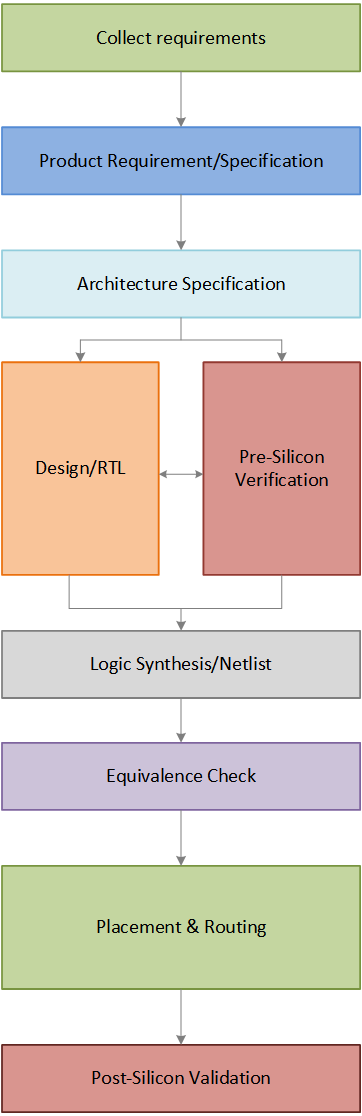

Un flujo de diseño típico sigue una estructura que se muestra a continuación y se puede dividir en varios pasos. Algunas de estas fases ocurren en paralelo y otras secuencialmente. Echaremos un vistazo a cómo se ve un ciclo de diseño de proyecto típico en la industria actual.

Requisitos

Un cliente de una empresa de semiconductores suele ser otra empresa que planea utilizar el chip en sus sistemas o productos finales. Por lo tanto, los requisitos del cliente también juegan un papel importante a la hora de decidir cómo debe diseñarse el chip. Naturalmente, el primer paso sería recopilar los requisitos, estimar el valor de mercado del producto final y evaluar la cantidad de recursos necesarios para realizar el proyecto.

Especificaciones

El siguiente paso sería recopilar "especificaciones" que describan de manera abstracta la funcionalidad, la interfaz y la arquitectura general del chip que se diseñará. Esto puede ser algo así como:

- Requiere poder computacional para ejecutar algoritmos de imágenes para admitir la realidad virtual

- Requiere dos procesadores ARM A53 con interconexión coherente y debe funcionar a 600 MHz

- Requiere interfaces USB 3.0, Bluetooth y PCIe de segunda generación

- Debe admitir una pantalla de 1920 x 1080 píxeles con el controlador adecuado

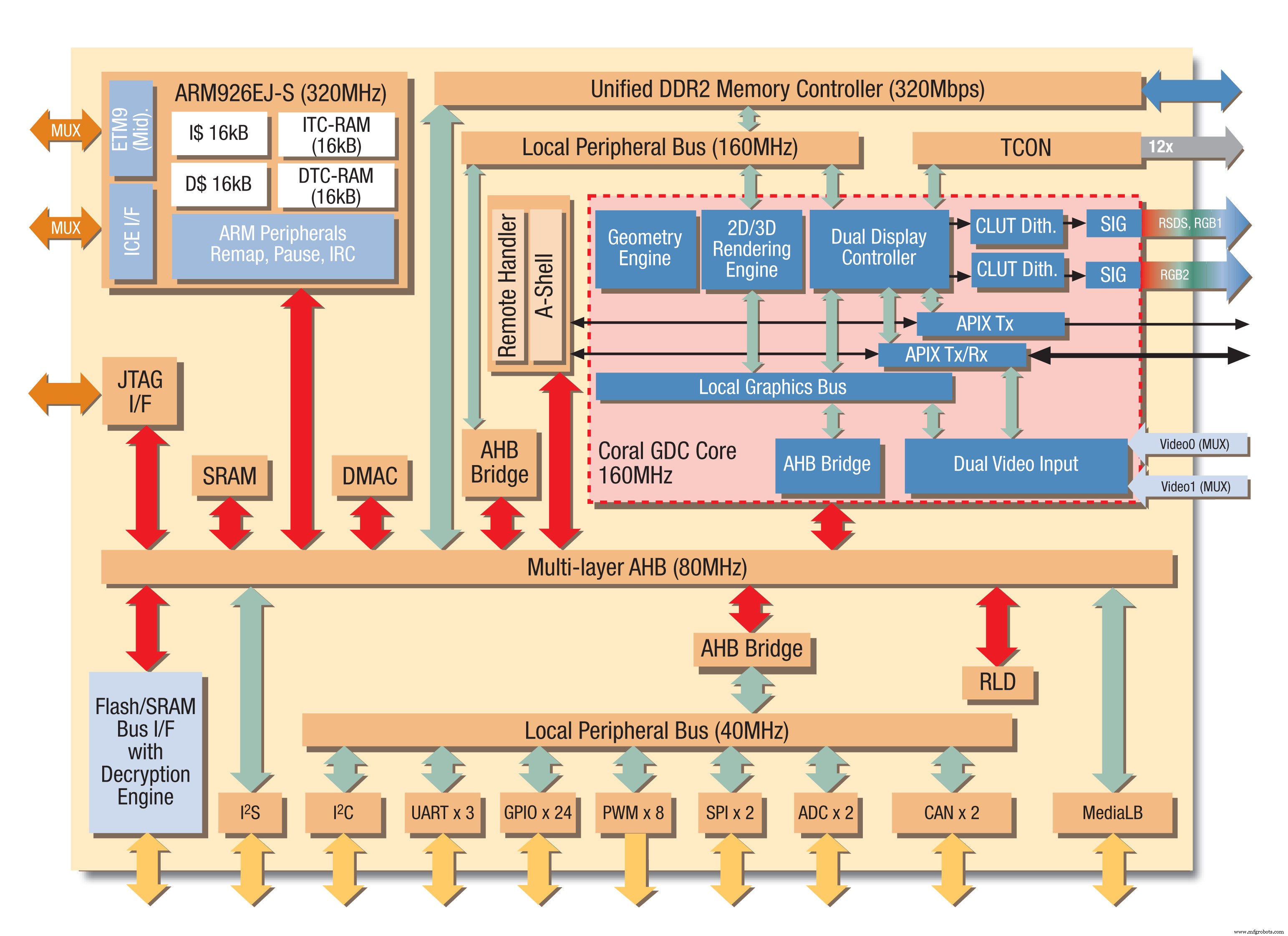

Arquitectura

Ahora, los arquitectos presentan una vista a nivel de sistema de cómo debería funcionar el chip. Ellos decidirán qué otros componentes se requieren, qué frecuencias de reloj deben ejecutar y cómo alcanzar los requisitos de potencia y rendimiento. También deciden cómo deben fluir los datos dentro del chip. Un ejemplo sería el flujo de datos cuando un procesador obtiene datos de imágenes de la RAM del sistema y los ejecuta. Mientras tanto, el motor gráfico ejecutará los datos posprocesados del lote anterior volcados en otra parte de la memoria y así sucesivamente.

Diseño Digital

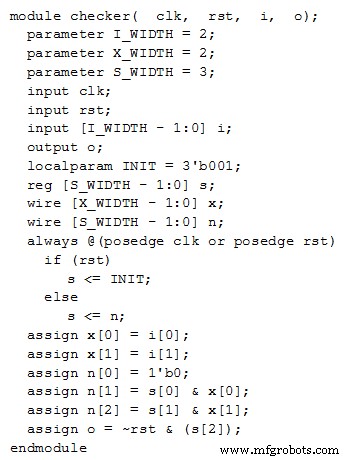

Debido a la naturaleza compleja de los chips modernos, no es posible construir algo desde cero y, en muchos casos, se reutilizarán muchos componentes. Digamos que la empresa X requiere un módulo FlexCAN para interactuar con otros módulos en un automóvil. Pueden comprar el diseño FlexCAN de otra empresa para ahorrar tiempo y esfuerzo o gastar recursos para construir uno por su cuenta. Además, no es práctico diseñar un sistema de este tipo a partir de bloques de construcción básicos como flip-flops y transistores CMOS. En su lugar, se desarrolla una descripción del comportamiento para analizar el diseño en términos de funcionalidad, rendimiento y otros problemas de alto nivel utilizando un lenguaje de descripción de hardware como Verilog o VHDL. Esto generalmente lo hace un diseñador digital y es similar a un programador de computadoras de alto nivel equipado con habilidades en electrónica digital.

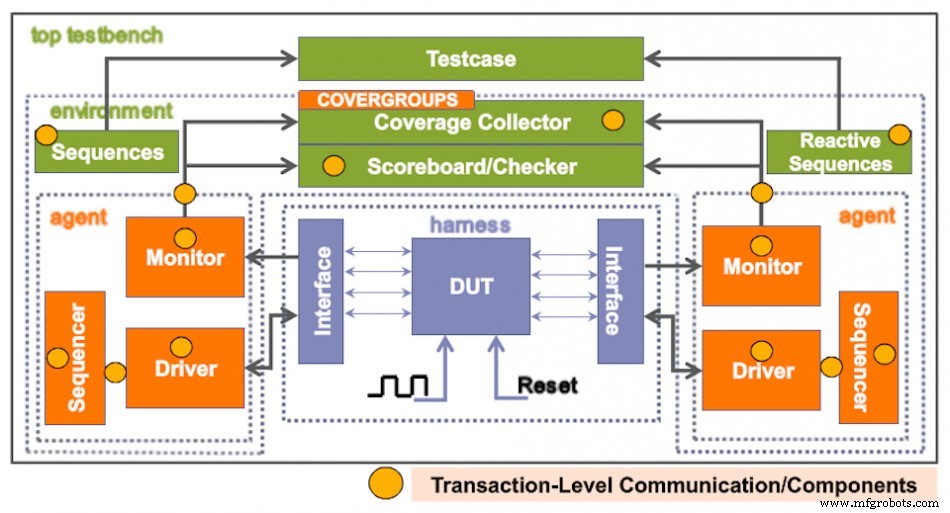

Verificación

Una vez que el diseño RTL está listo, debe verificarse su corrección funcional. Por ejemplo, se espera que un procesador DSP emita transacciones de bus para obtener instrucciones de la memoria, pero ¿cómo sabemos que esto sucederá como se esperaba? Por lo tanto, se requiere verificación funcional en este punto, que se realiza con la ayuda de simuladores EDA que tienen la capacidad de modelar el diseño y aplicarle diferentes estímulos. Este es el trabajo de un ingeniero de verificación previa al silicio.

Para ahorrar tiempo y llegar al cierre funcional, los equipos de diseño y verificación operan en paralelo donde los diseñadores "lanzan" una versión RTL y el equipo de verificación desarrolla un entorno de banco de pruebas y casos de prueba para probar la funcionalidad de esa versión RTL. Si alguna de estas pruebas falla, podría indicar un problema con el diseño y se generará un "error" en ese elemento de diseño. Este error deberá corregirse en la próxima versión del lanzamiento de RTL del equipo de diseño. Este proceso continúa hasta que haya un buen nivel de confianza en la corrección funcional del diseño.

Síntesis Lógica

Ahora que estamos satisfechos con el diseño, es hora de convertirlo en un esquema de hardware con elementos reales como puertas combinacionales y flip-flops. Este paso se llama síntesis. Las herramientas de síntesis lógica permiten la conversión de la descripción RTL en HDL a una lista de conexiones a nivel de puerta. Esta netlist no es más que una descripción del circuito en términos de puertas y conexiones entre ellas. Podría ser algo como:

and_2_0 u_and2_0 ( .in_a (_net_112),

.in_b (_net_56),

.out (_net_222));

ff_lt u_ff_lt_122 (.d (_net_222),

.clk (_net_11),

.q (_net_76));

Las herramientas de síntesis lógica aseguran que la lista de conexiones cumpla con las especificaciones de tiempo, área y potencia. Por lo general, tienen acceso a diferentes procesos de nodos de tecnología y bibliotecas de elementos digitales y pueden realizar cálculos inteligentes para cumplir con todos estos criterios diferentes. Estas bibliotecas se obtienen de fábricas de semiconductores que proporcionan características de datos para diferentes componentes, como tiempos de subida/bajada para flip-flops, tiempo de entrada-salida para puertas combinacionales, etc.

Equivalencia lógica

Luego, se verifica la equivalencia lógica de la lista de conexiones a nivel de puerta con el RTL y, a veces, se realiza una "verificación de nivel de puerta" donde se verifican ciertos elementos una vez más, la diferencia es que esta vez está a nivel de puerta y está en un nivel más bajo. de abstracción Los tiempos de simulación tienden a ser más lentos debido a la gran cantidad de elementos involucrados en el diseño en esta etapa junto con la información de retraso anotada.

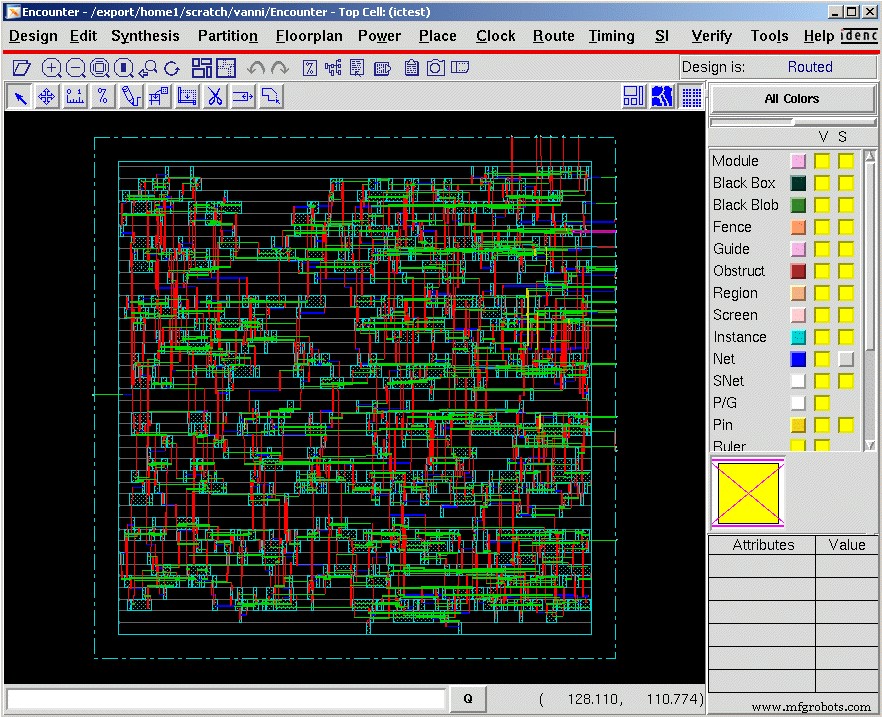

Ubicación y enrutamiento

Luego, la lista de conexiones se ingresa en el flujo de diseño físico, donde el lugar y la ruta automáticos (APR o PnR) se realizan con la ayuda de las herramientas EDA. Un buen ejemplo de tales herramientas es Cadence Encounter y Synopsys IC Compiler. Esto seleccionará y colocará celdas estándar en filas, definirá mapas de bolas para entrada-salida, creará diferentes capas de metal y colocará búferes para cumplir con el tiempo. Una vez que se realiza este proceso, se genera un diseño y generalmente se envía para la fabricación. Esta etapa generalmente la maneja el equipo de diseño físico que conoce bien el nodo de tecnología y los detalles de implementación física.

Validación

No termina aquí. La misma empresa de semiconductores fabricará un chip de muestra o lo enviará a una fundición de terceros como TSMC o Global Foundries. Esta muestra ahora pasa por un proceso de validación posterior al silicio donde otro equipo de ingenieros ejecuta diferentes patrones en un probador. Es mucho más difícil depurar en la validación posterior al silicio que en la verificación previa al silicio simplemente porque el nivel de visibilidad de los nodos internos de un chip se reduce drásticamente. Además, un millón de ciclos de reloj habrían terminado en un segundo y rastrear la hora exacta del error llevará mucho tiempo. Si se encuentran problemas reales o errores de diseño en esta etapa, se deberán corregir en RTL, volver a verificar y se deberán realizar todos los pasos que siguen.

Aunque hay varios pasos en el flujo de diseño, gran parte de la actividad de diseño suele concentrarse en la optimización y verificación de la descripción RTL del circuito. Es importante tener en cuenta que, aunque las herramientas EDA están disponibles para automatizar los procesos, el uso inadecuado conducirá a diseños ineficientes y, por lo tanto, el diseñador debe tomar decisiones conscientes durante el proceso de diseño.

Verilog

- Tutorial de Verilog

- Capas de abstracción de diseño

- Cuatro aspectos principales de un buen diseño de panel de control

- Conceptos básicos de diseño de armarios de control en máquinas, automatización e industria

- Conceptos básicos de diseño del panel de control

- Respuestas breves a grandes preguntas sobre el diseño de PCB

- Métodos para fortalecer la capacidad antiinterferencias en el diseño de PCB

- Cómo vencer las interferencias en el diseño de PCB

- Tres consideraciones de diseño que garantizan la compatibilidad electromagnética de la PCB de la computadora portátil

- ¿Qué es el diseño arquitectónico?

- Pregunte a Atlas Copco:¿Cuándo debo desarrollar un perfil de caudal?