Avanzando hacia 7nm

Esta es la cuarta de una serie de cuatro partes sobre artículos destacados de IBM en IEDM 2016.

La reunión anual internacional de dispositivos electrónicos es "el foro preeminente del mundo para informar sobre los avances tecnológicos en las áreas de tecnología, diseño, fabricación, física y modelado de semiconductores y dispositivos electrónicos". Así que los investigadores de IBM trajeron su termómetro de sonda de barrido, su espaciador de aire para un chip de 10 nanómetros, su chip de 7 nm, y para no dejarse superar por el silicio, también trajeron sus nanotubos de carbono. Estos documentos y presentaciones de IBMers y muchos socios participarán en la conferencia de esta semana en San Francisco.

IEDM presenta cuatro artículos de IBM como algunos de los mejores ejemplos de la conferencia de esta reinvención de la computación:extensión de la Ley de Moore, construcción de nuevas arquitecturas y uso de nuevos materiales para ir más allá. Aquí hay un vistazo más de cerca a estos artículos y a los científicos detrás del trabajo. La última entrega de la serie destaca el artículo "Una tecnología FinFET de 7 nm con patrones EUV y canales de alta movilidad de doble tensión", de Ruilong Xie, miembro senior del personal técnico de GlobalFoundries y miembros del equipo de IBM en el Albany Nanotech Center. .

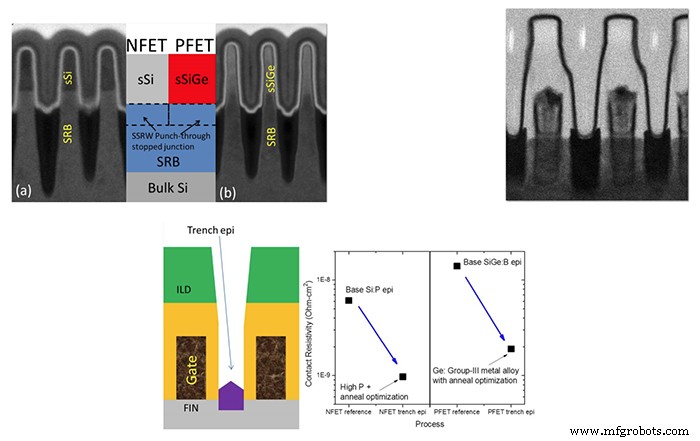

En julio pasado, IBM y sus socios de la Alianza anunciaron que habían desarrollado los primeros chips de prueba de nodos de 7 nm del mundo. El gran avance se produjo mediante la aplicación de la litografía ultravioleta extrema (EUV), una técnica que utiliza la luz para grabar patrones en otros materiales, y el uso de silicio germanio (SiGe) como material de canal en el transistor.

Del silicio al silicio germanio

El documento IEDM del equipo muestra que “la tecnología FinFET basada en SiGe demostró una mejora del rendimiento con las reglas básicas de la tecnología de 10 nm (estándares de la industria), proporcionando soluciones elegantes hacia una opción de tecnología CMOS viable. Una de esas elegantes soluciones es su capacidad para dispositivos de bajo consumo y alto rendimiento en el mismo chip, sin perder rendimiento o variabilidad en un tipo de dispositivo sobre el otro ”, como se explica en Innovación de materiales a 7 nm .

Además, SiGe amplía los límites del escalado de chips al cambiar la forma en que la corriente pasa a través del canal de un transistor. Resulta que al agregar átomos de germanio más grandes a un cristal hecho de átomos de silicio más pequeños, el cristal desarrolla un desajuste de red, lo que genera tensión en el canal del transistor. Esta deformación hace posible mover más corriente a través del canal a voltajes más bajos. Entonces, al usar SiGe como material de canal en combinación con innovaciones en resistencia parásita y reducción de capacitancia, el equipo pudo trazar una hoja de ruta hacia un chip de 7 nm, mientras se mantiene un equilibrio entre potencia y rendimiento, un rendimiento a potencia constante que, como se presentó en IEDM ¡40 por ciento mejor que un chip de 10 nm!

Longitudes de onda de luz extremadamente pequeñas

La luz que se utiliza, con sólo una longitud de onda de 13,5 nm, es mucho más corta que la luz de longitud de onda estándar actual de 193 nm, lo que la hace capaz de grabar 20 mil millones de transistores de 7 nm en un chip. Pero antes de que el equipo pueda poner tantos interruptores en un chip, necesitan hacer que la tecnología que hay detrás, usando una longitud de onda tan corta, sea un proceso consistente, controlado y repetible.

Para hacer chips usando litografía, una oblea se expone a un patrón de luz de la misma manera que todos los negativos fotográficos no digitales se imprimen en papel de contacto:se sostiene sobre la oblea y la luz pasa a través de una máscara (el 'negativo') . El tamaño de las líneas y los cables que se pueden imprimir con esta técnica reflejan no solo el tamaño de las líneas de la máscara, sino también la longitud de onda de la luz que se está utilizando. Hoy en día, con luz de 193 nm, una oblea puede exponerse varias veces si el patrón necesario es más pequeño que el que 193 nm puede entregar por sí solo.

Por lo tanto, al igual que la impresión en madera japonesa, se coloca un patrón tras otro en la parte superior de la oblea para obtener una viruta más intrincada y más pequeña. Esta técnica de múltiples patrones, sin embargo, causa degradación; lo que puede no ser un problema tan crítico para los chips en dispositivos producidos en masa como los teléfonos inteligentes, pero es un obstáculo importante para las supercomputadoras y sistemas especializados que requieren una confiabilidad muy alta. Y, si bien es técnicamente posible fabricar chips de 7 nm de esta manera, es una gran razón por la que IBM ha decidido explorar cómo fabricar chips de 7 nm utilizando tecnología EUV.

Con EUV de 13,5 nm, solo se necesita un patrón de alta fidelidad para imprimir un solo patrón en un chip de 7 nm. El desafío para EUV es cómo madurar la tecnología para que esté lista para la producción. Al igual que IBM System 360, construido en 1964, condujo a las máquinas más pequeñas y más rápidas de la actualidad a través del refinamiento, el escalado y el esfuerzo de ingeniería, EUV tendrá que madurar de manera similar.

Considere esto:para generar luz de 13.5 nm, el dispositivo EUV libera una gota de estaño fundido en el vacío (para obtener una forma esférica) que luego es golpeada con un láser de dióxido de carbono que la aplana y la mueve a un ángulo específico. La lata, que sigue cayendo, se golpea y se vaporiza con otro láser de dióxido de carbono más potente para liberar una luz de 13,5 nm, que luego se captura y se enfoca en una oblea utilizando espejos especializados.

Si bien el proceso para utilizar esta luz de 13,5 nm es complicado, el trabajo de los equipos está demostrando que es posible hacer un chip de 7 nm con EUV y que proporciona resultados de alta calidad. Lo que debería significar que se pueden fabricar chips especializados de alta confiabilidad para futuros sistemas de alto rendimiento para satisfacer las demandas de las supercomputadoras y sistemas de próxima generación.

Lea la primera parte:Mapeo de puntos calientes

Lea la segunda parte:Otro tipo de chip con nanotubos de carbono

Lea la tercera parte:Separadores de aire para chips de 10 nm

Nanomateriales

- 5 beneficios de usar bisagras de plástico

- C # usando

- Sensor de movimiento con Raspberry Pi

- Tecnología de semiconductores avanzada, un nanómetro a la vez

- Sensor de corazón-pulmón en miniatura en un chip

- 3 ventajas de usar una fresadora

- Ventajas del uso de aleaciones

- ¿Qué son los transportadores de virutas?

- Introducción a los transportadores de virutas

- ¿Qué es un transportador de chips magnéticos?

- Uso de una fresadora como torno