Comprensión de la habilitación de DSP mediante el MCU cruzado i.MX RT500 de NXP

Obtenga información sobre programas de subprocesos múltiples, desarrollo de aplicaciones con el sistema operativo en tiempo real XOS, uso compartido de recursos con semáforos y cómo la familia i.MX RT500 de NXP de los microcontroladores ayudan a los ingenieros a diseñar dispositivos inteligentes habilitados para DSP.

Los dispositivos de consumo inteligentes de hoy en día requieren componentes capaces de procesar grandes cantidades de datos para satisfacer las demandas de diversas aplicaciones de procesamiento de señales y seguridad. Estos componentes (incluidos los microcontroladores) deben poder procesar esos datos de manera rápida y eficiente, lo que requiere procesadores de señales digitales altamente optimizados.

Este artículo presenta algunas características del procesador de audio Cadence® Tensilica® Fusion F1, un coprocesador designado que ayuda a la CPU principal del MCU i.MX RT500 a realizar cálculos de procesamiento de señales.

Conceptos básicos de programas de subprocesos múltiples

A primera vista, el hardware de procesamiento moderno crea la ilusión de que ejecuta muchos subprocesos simultáneamente. En realidad, un solo núcleo de CPU se encarga de un solo hilo a la vez. Cuando el número de subprocesos excede el número de núcleos de CPU disponibles, se necesita un sistema operativo para programar los subprocesos.

El sistema operativo necesita realizar un seguimiento de todos los subprocesos iniciados y su estado, y asigna ranuras de tiempo de CPU a cada subproceso para que varias aplicaciones puedan ejecutarse de manera eficiente y aparentemente en paralelo.

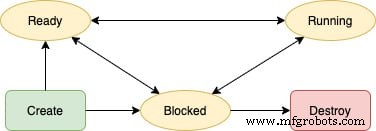

Figura 1. Los diferentes estados de un hilo

El programador del sistema operativo mantiene una cola para los subprocesos que están listos para ejecutarse, una cola para bloquear los subprocesos y necesita almacenar información sobre los subprocesos que se están ejecutando actualmente para lograr la distribución justa del tiempo de la CPU:

- Los subprocesos en la cola lista actualmente están esperando que el sistema operativo los programe en la CPU. Por lo general, el programador del sistema operativo conoce diferentes niveles de prioridad, que considera al elegir el próximo subproceso que se ejecutará en la CPU.

- Los subprocesos de bloqueo esperan a que suceda un evento externo, por ejemplo, una interrupción de un pin o una operación de archivo. Programar estos subprocesos significaría que la CPU desperdicia energía de procesamiento esperando que finalice una operación externa. Una vez que finaliza la operación de bloqueo, el hilo de espera asociado vuelve al final de la cola lista.

- Los subprocesos que se están ejecutando actualmente pueden realizar una operación de bloqueo o el sistema operativo puede programar un subproceso diferente de acuerdo con su estrategia de programación. En ese caso, el programador moverá el subproceso que se está ejecutando actualmente a la lista de subprocesos bloqueados o al final de la cola lista, respectivamente.

Los desarrolladores de sistemas operativos pueden optar por implementar una o muchas estrategias de programación diferentes según los requisitos exactos. Además de la programación, la sincronización y la comunicación entre diferentes subprocesos son otros aspectos esenciales de los sistemas de subprocesos múltiples.

Condiciones y eventos en XOS

Las condiciones dentro de XOS RTOS (sistema operativo en tiempo real) permiten a los desarrolladores instruir a un hilo para que se bloquee hasta que una condición específica se convierta en verdadera. El sistema evalúa cada condición utilizando una función de condición definida por los desarrolladores de la aplicación. XOS realiza una evaluación cada vez que otro hilo señala el objeto de condición o cuando un controlador de interrupciones activa uno.

Los eventos dentro de XOS, por otro lado, representan un grupo de bits que los desarrolladores pueden utilizar para sincronizar diferentes subprocesos o subprocesos e interrumpir controladores. XOS permite que varios subprocesos esperen eventos y los señalen al mismo tiempo.

Interrupciones en XOS

XOS ofrece un amplio conjunto de funciones para manejar interrupciones y excepciones que ocurren durante el tiempo de ejecución. Los mecanismos de interrupción dentro de XOS ofrecen a los programadores la flexibilidad de instalar manejadores personalizados mientras aseguran que el despacho de interrupciones funcione lo más rápido posible dentro del sistema. El XOS también admite el manejo de interrupciones anidado, lo que significa que el sistema operativo pausa el controlador de interrupciones actual si se produce una interrupción de mayor prioridad. Una vez que el sistema termina de manejar la interrupción de alta prioridad, automáticamente reanuda el servicio de las interrupciones de baja prioridad.

Los subprocesos también pueden tener servicios relacionados con el tiempo, como retrasos programados y devoluciones de llamada periódicas con temporizador en XOS. El coprocesador DSP admite hasta tres temporizadores internos que los programadores pueden configurar según sea necesario.

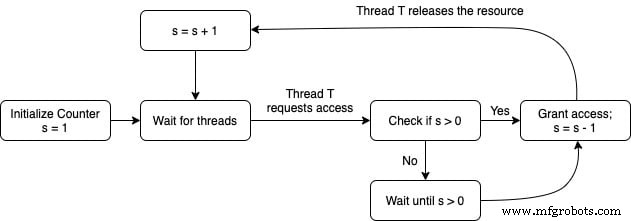

Comprensión de los semáforos

En la programación de subprocesos múltiples, los semáforos proporcionan un medio para controlar y coordinar el acceso a un recurso compartido. Los semáforos ayudan a evitar problemas de secciones críticas en sistemas concurrentes al sincronizar diferentes subprocesos. Los semáforos son una construcción simple que realiza un seguimiento de un contador interno con un valor inicial predeterminado que los programadores pueden establecer libremente en el código fuente. Existen diferentes implementaciones, pero el contador generalmente representa cuántos subprocesos aún pueden acceder a un recurso compartido.

Siempre que un hilo quiera acceder al recurso compartido, el sistema verifica si el contador asociado es mayor que cero. Si es así, el sistema operativo otorga acceso al recurso y disminuye el contador interno del semáforo. Si un subproceso no puede acceder al recurso en el momento dado, el subproceso cambia a un estado de bloqueo y espera hasta que reciba acceso al recurso. Siempre que un hilo libera el recurso, el sistema operativo aumenta el contador de semáforo y un nuevo hilo puede entrar en la sección crítica.

Figura 2. Un diagrama de flujo que ilustra cómo funcionan los semáforos

Descripción general de la MCU i.MX RT500 y el DSP

i.MX RT500 es una familia de microcontroladores de doble núcleo basados en un potente núcleo Arm® Cortex®-M33 con una velocidad de reloj de hasta 275 MHz y soporte para hasta cinco megabytes de SRAM.

El MCU i.MX RT500 ofrece funciones de protección como Arm TrustZone y una unidad de protección de memoria (MPU) incorporada con soporte para hasta ocho regiones. El coprocesador criptográfico CASPER permite la aceleración del hardware para impulsar varias funciones necesarias para los algoritmos criptográficos asimétricos. Un conjunto de funciones de ahorro de energía permite a los diseñadores adaptar el consumo de energía del i.MX RT500 a los requisitos de su aplicación.

Varios aceleradores de hardware dedicados ayudan a la CPU principal a realizar cálculos DSP. Un DSP de audio Cadence® Tensilica® Fusion F1 adicional, una GPU 2D con aceleración de gráficos vectoriales y varias interfaces de pantalla hacen que el i.MX RT500 sea adecuado para varias aplicaciones integradas seguras y de bajo consumo. Los casos de uso típicos incluyen aplicaciones HMI, dispositivos IoT, dispositivos para escuchar, asistentes personales activados por voz y otros dispositivos de consumo similares.

Una mirada al DSP de audio

El i.MX RT500 contiene varios coprocesadores especiales que pueden ayudar a aligerar la carga en los núcleos de la CPU al realizar cálculos matemáticamente complejos y dejar los núcleos de procesamiento libres para realizar otras tareas. Uno de esos procesadores dedicados es el DSP de fusión, que incluye un procesador de audio Cadence® Tensilica® Fusion F1 y una unidad de punto flotante de hardware.

Este motor de procesamiento de audio funciona a frecuencias de hasta 200 MHz y está diseñado para habilitar dispositivos activados por voz siempre activos, como asistentes virtuales. Además, el DSP de audio combina varios módulos para tareas típicas de preprocesamiento y posprocesamiento utilizando numerosos códecs de audio.

El DSP y los núcleos de la CPU principal pueden comunicarse entre sí a través de varios medios. Los desarrolladores pueden usar la SRAM completa cuando trabajan con el DSP de fusión, a menos que la RAM esté protegida y ciertas partes estén marcadas para acceso solo seguro.

Programación con DSP en mente

Los DSP de Tensilica admiten varios sistemas operativos en tiempo real (RTOS), incluidos FreeRTOS ™, Zephyr ™, Linux® y XOS. Cadence desarrolló el kernel integrado XOS como un diseño de referencia con los procesadores Tensilica en mente.

Las características ligeras del kernel XOS incluyen un programador de tareas, cambio de contexto adaptativo, mecanismos de sincronización, administración de interrupciones y excepciones y administración de recursos críticos. El código fuente del kernel está escrito principalmente en C estándar y no es específico para procesadores Xtensa y DSP.

Cumplimiento de los requisitos de dispositivos de consumo inteligente

La familia de MCU cruzados i.MX RT500 tiene varias características diseñadas para inspirar a los dispositivos de consumo inteligentes del mañana. Los diferentes coprocesadores ayudan a los principales núcleos de procesamiento de la MCU a realizar cálculos matemáticamente complejos para aplicaciones de seguridad y procesamiento de señales. Uno de esos coprocesadores es el DSP de audio Cadence® Tensilica® Fusion F1 altamente optimizado, que permite dispositivos activados por voz siempre activos, como asistentes virtuales. Los programadores pueden utilizar XOS y Xplorer IDE para diseñar aplicaciones para el procesador Cadence dedicado.

La nota de aplicación AN13159 contiene más detalles, una lista de funciones API compatibles y ejemplos de condiciones y eventos en XOS, y el sitio web de NXP ofrece más información sobre las capacidades y aplicaciones de i.MX RT500. También proporciona diferentes materiales de capacitación, como notas de la aplicación, videos y seminarios web bajo demanda.

Los artículos de la industria son una forma de contenido que permite a los socios de la industria compartir noticias, mensajes y tecnología útiles con los lectores de All About Circuits de una manera que el contenido editorial no es adecuado. Todos los artículos de la industria están sujetos a estrictas pautas editoriales con la intención de ofrecer a los lectores noticias útiles, experiencia técnica o historias. Los puntos de vista y las opiniones expresados en los artículos de la industria son los del socio y no necesariamente los de All About Circuits o sus redactores.

Incrustado

- C # usando

- El dispositivo híbrido fusiona las arquitecturas DSP y MCU

- Cuando un DSP supera a un acelerador de hardware

- Decisiones, decisiones:¿Acelerador de hardware o DSP?

- Medición del nivel de fluido sin contacto utilizando un chip reflectómetro

- Uso de etiquetas RFID para supervisar la seguridad del hogar

- Los conjuntos de chips de radar de imágenes 4D mejoran la identificación de objetos

- Determinismo de la fase de encendido:uso de la sincronización multichip

- Bluetooth MCU mejora la seguridad de IoT

- La MCU inalámbrica presenta una arquitectura de doble núcleo

- Directrices para el manejo de DSP utilizando