Sincronización y distribución de restablecimiento asincrónico:desafíos y soluciones

La falta de coordinación entre los reinicios asíncronos y los relojes lógicos síncronos conduce a fallas intermitentes en el encendido. En esta serie de artículos, discutimos los requisitos y desafíos del reinicio asincrónico y exploramos soluciones avanzadas para diseños ASIC vs FPGA.

Los restablecimientos asíncronos se emplean tradicionalmente en los diseños de VLSI para llevar los circuitos síncronos a un estado conocido después del encendido. La operación de liberación de reinicio asíncrono debe coordinarse con la señal de reloj lógico síncrono para eliminar fallas de sincronización debido a una posible contención entre el reinicio y el reloj. La falta de tal coordinación conduce a fallas intermitentes en el encendido. El problema se agrava cuando se consideran diseños grandes de dominios de reloj múltiple. Además de los problemas de sincronización, la distribución de un reinicio asincrónico a millones de flip-flops es un desafío, ya que requiere técnicas similares a CTS (Clock Tree Synthesis) y requiere un área y recursos de enrutamiento similares.

Se revisan los requisitos y desafíos del restablecimiento asincrónico, centrándose en los problemas de sincronización y distribución. Se discuten los inconvenientes de las soluciones clásicas para restablecer la sincronización (restablecer la sincronización de la fuente del árbol) y la distribución (restablecer la síntesis del árbol). Se presentan soluciones avanzadas para una convergencia de temporización más rápida y sencilla y una distribución y sincronización de reinicio más fiables. Se detallan diferentes enfoques para diseños ASIC versus FPGA.

La Parte 1 (este artículo) describe los problemas relacionados con los restablecimientos asincrónicos y describe los enfoques para resolver esos problemas. La parte 2 analiza soluciones adicionales para el reinicio asincrónico correcto en ASIC y FPGA. En la Parte 3 se analizan algunos casos especiales útiles.

1. Desafíos de restablecimiento asincrónico

Normalmente se incluye una función de reinicio en los diseños de VLSI digitales para llevar la lógica a un estado conocido. El reinicio se requiere principalmente para la lógica de control y puede eliminarse de la lógica de la ruta de datos, reduciendo el área lógica. El reinicio puede ser sincrónico o asincrónico en relación con la señal del reloj.

El reinicio sincrónico requiere un reloj activo, incurre en cierta latencia relacionada con el ciclo del reloj y puede afectar la sincronización de las rutas de datos. Por otro lado, los reinicios síncronos son deterministas y no incurren en metaestabilidad.

El reinicio asíncrono no requiere un reloj activo para llevar los flip-flops a un estado conocido, tiene una latencia más baja que un reinicio síncrono y puede explotar los pines de entrada especiales del flip-flop que no afectan la sincronización de la ruta de datos. Sin embargo, los restablecimientos asincrónicos tienen varios inconvenientes:

-

Pueden causar metaestabilidad en flip-flops, lo que lleva a un comportamiento no determinista.

-

Los restablecimientos asincrónicos deben ser accesibles directamente para habilitar DFT.

-

Los restablecimientos asincrónicos pueden generar problemas de confiabilidad en aplicaciones rad-hard, siendo susceptibles a fenómenos transitorios de evento único (SET) [1].

Dejando de lado la discusión sobre qué tipo de reinicio es mejor [2], en este artículo nos enfocamos en los problemas y soluciones relacionados con los reinicios asincrónicos. Algunas de las técnicas presentadas en este documento son aplicables tanto a restablecimientos asíncronos como síncronos.

Los restablecimientos asincrónicos se emplean ampliamente en diseños digitales. Los controladores típicos de restablecimientos asíncronos son puertos externos, según el estado de la fuente de alimentación (circuitos RC, dispositivos de vigilancia), botones de restablecimiento manual y maestros externos, como microprocesadores.

En muchos casos, los restablecimientos asíncronos se pueden reemplazar por síncronos, pero hay algunas situaciones en las que la funcionalidad de restablecimiento asíncrono es obligatoria. Un ejemplo es un diseño síncrono que no tiene un reloj activo al encenderse (el reloj es inestable o está bloqueado para reducir la energía), pero requiere un cierto estado conocido para sus interfaces externas. Otro ejemplo es el diseño de baja potencia que se requiere para minimizar la energía durante el proceso de encendido, sin relojes activos.

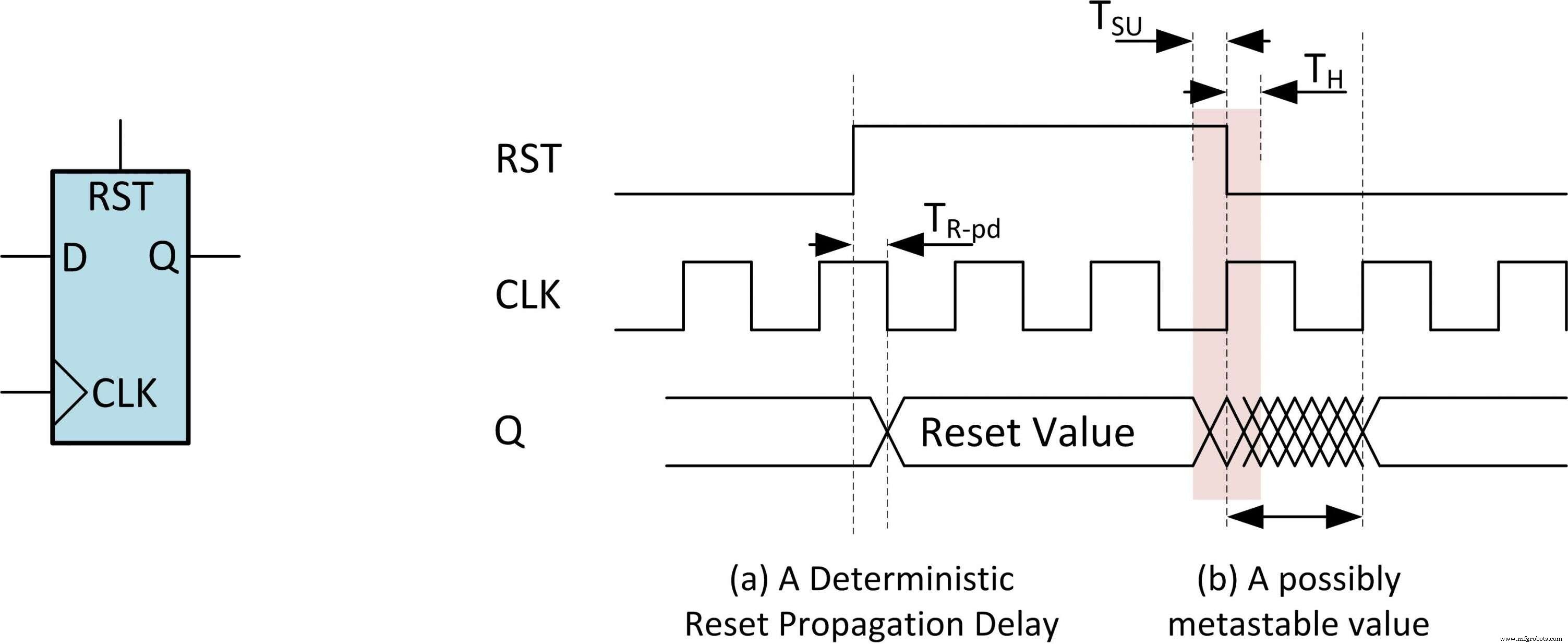

El empleo del reinicio asincrónico no es sencillo. Aunque el tiempo relativo entre el reloj y el reinicio se puede ignorar durante la afirmación de reinicio, la liberación de reinicio debe sincronizarse con el reloj. Evitar la sincronización del borde de liberación de reinicio puede conducir a la metaestabilidad. Con referencia a la Figura 1, se muestra un restablecimiento asincrónico alto activo. La afirmación de reinicio (a) afecta la salida Q del flip-flop dentro de un tiempo limitado determinísticamente (retardo de propagación, T R-pd ) e independientemente de la señal de reloj CLK. Durante la liberación de reinicio (b), las condiciones de configuración y tiempo de espera deben cumplirse para el puerto RST en relación con el puerto de reloj CLK. Una violación de las condiciones de configuración y retención para el puerto RST (también conocido como tiempo de recuperación y eliminación de reinicio) puede hacer que el flip-flop se vuelva metaestable, provocando fallas en el diseño debido al cambio a un estado desconocido. Tenga en cuenta que esta situación es similar a la violación de las condiciones de configuración y retención para el puerto de datos flip-flop, D.

haz clic para ampliar la imagen

Figura 1:Aserción y liberación de restablecimiento asincrónico alto activo. (a) Una afirmación de reinicio asincrónica (b) Una liberación de reinicio asincrónica con violación de tiempo. (Fuente:vSync Circuits)

Incrustado

- Actualizaciones inalámbricas:cinco desafíos y soluciones típicos

- Principales tendencias y desafíos de PCB

- Anvo-Systems y Mouser firman un acuerdo de distribución

- Swissbit:soluciones de seguridad basadas en hardware para proteger datos y dispositivos

- Rutronik y AP Memory firman un acuerdo de distribución global

- Tendencias de IIoT y desafíos a seguir

- Monitoreo del desempeño:desafíos, soluciones y beneficios

- Seguridad IoT Industrial:Desafíos y Soluciones

- Desafíos de la fabricación de automóviles y soluciones de IoT

- Los 5 principales desafíos logísticos y soluciones para la industria manufacturera

- Desafíos del diseño de PCB de alta velocidad en la integridad de la señal y sus soluciones