Variables - Ejemplo de VHDL

Las variables en VHDL actúan de manera similar a las variables en C. Su valor es válido en la ubicación exacta del código donde se modifica la variable. Por tanto, si una señal utiliza el valor de la variable antes la asignación, tendrá el antiguo valor de la variable. Si una señal usa el valor de la variable después la asignación tendrá el nuevo valor de la variable.

Reglas de variables:

- Las variables solo se pueden usar dentro de los procesos

- Cualquier variable que se cree en un proceso no se puede usar en otro proceso

- Las variables deben definirse después de la palabra clave proceso pero antes de la palabra clave begin

- Las variables se asignan mediante := símbolo de asignación

- Las variables que se asignan inmediatamente toman el valor de la asignación

Lo más importante que hay que entender es que las variables toman inmediatamente el valor de su asignación. Aquí hay un ejemplo que muestra una forma útil de usar variables:almacenar datos para uso temporal . Utiliza una declaración de caso y el operador de concatenación ampersand (&).

VAR_CASE : process (i_clk)

variable v_Choices : std_logic_vector(1 downto 0);

begin

v_Choices := i_select_1 & i_select_2; -- concatenation

case v_Choices is

when "00" =>

o_data <= "0001";

when "01" =>

o_data <= "0010";

-- ETC

En el ejemplo anterior, concatenamos las dos señales para que pudieran usarse en la declaración del caso. La variable v_Choices estuvo inmediatamente disponible para su uso tan pronto como se asignó. Veamos otro ejemplo. El siguiente ejemplo es más completo y demuestra cómo las variables toman inmediatamente el valor de su asignación. Las señales r_Var_Copy1 y r_Var_Copy2 parecen ser las mismas, pero r_Var_Copy2 nunca puede llegar a 5 antes de que se reinicie.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity variable_ex is

port (

i_clk : in std_logic;

o_done : out std_logic

);

end variable_ex;

architecture rtl of variable_ex is

signal r_Done : std_logic := '0';

signal r_Var_Copy1 : natural range 0 to 5 := 0;

signal r_Var_Copy2 : natural range 0 to 5 := 0;

begin

EX_VAR : process (i_clk)

variable v_Count : natural range 0 to 5 := 0;

begin

if rising_edge(i_clk) then

v_Count := v_Count + 1;

r_Var_Copy1 <= v_Count;

if v_Count = 5 then

r_Done <= '1';

v_Count := 0;

else

r_Done <= '0';

end if;

r_Var_Copy2 <= v_Count;

end if;

end process EX_VAR;

o_done <= r_Done;

end rtl;

Para simular nuestro diseño, necesitamos crear un banco de pruebas. Además, las variables pueden ser un poco difíciles de mostrar en la simulación. Si está utilizando Modelsim, lea más sobre cómo ver sus variables en la ventana de forma de onda de Modelsim.

Banco de prueba:

library ieee;

use ieee.std_logic_1164.all;

entity variable_ex_tb is

end variable_ex_tb;

architecture behave of variable_ex_tb is

component variable_ex

port (

i_clk : in std_logic;

o_done : out std_logic

);

end component variable_ex;

constant c_CLK_PERIOD : time := 10 ns;

signal r_CLK : std_logic := '0';

signal w_DONE : std_logic;

begin

UUT : variable_ex

port map (

i_clk => r_CLK,

o_done => w_DONE

);

r_CLK <= not r_CLK after c_CLK_PERIOD/2;

end behave;

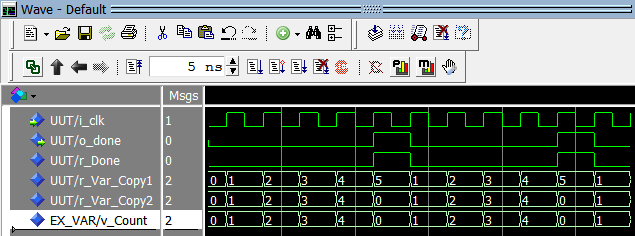

Variables Ejemplo de forma de onda del banco de pruebas

Variables Ejemplo de forma de onda del banco de pruebas El ejemplo anterior demuestra cómo las variables actúan de manera diferente a las señales. Las señales r_Var_Copy1 y r_Var_Copy2 parecen ser las mismas, pero r_Var_Copy2 nunca puede llegar a 5 antes de que se reinicie.

VHDL

- Declaración de procedimiento:ejemplo de VHDL

- Registros:ejemplo de VHDL

- Opciones de análisis

- Variables de C# y tipos de datos (primitivos)

- Variables, literales y constantes de C++

- C Variables, constantes y literales

- Clase de almacenamiento C

- Cadenas en C:cómo declarar variable, inicializar, imprimir, ejemplo

- Java - Tipos de variables

- C - Variables

- Alcance variable en C++