Tutorial - Introducción a VHDL

VHDL es un acrónimo horrible. Significa V HSIC H hardware D escripción L idioma Un acrónimo dentro de un acrónimo, impresionante! VHSIC significa V ery H alta S orinar yo C integrado circuito Por lo tanto, VHDL expandido es V Circuito integrado de alta velocidad H hardware D escripción L idioma UPH eso es un bocado. VHDL es uno de los dos lenguajes utilizados por la educación y las empresas para diseñar FPGA y ASIC. Primero podría beneficiarse de una introducción a los FPGA y ASIC si no está familiarizado con estas fascinantes piezas de circuitos. VHDL y Verilog son los dos lenguajes que usan los diseñadores digitales para describir sus circuitos, y son diferentes por diseño a los lenguajes de software tradicionales como C y Java.

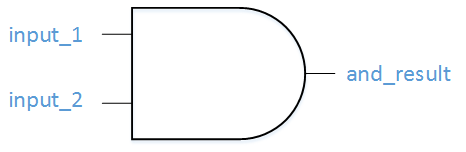

Para el siguiente ejemplo, crearemos un archivo VHDL que describe una puerta Y. Como repaso, un And Gate simple tiene dos entradas y una salida. La salida es igual a 1 solo cuando ambas entradas son iguales a 1. A continuación se muestra una imagen de la puerta And que describiremos con VHDL.

Una puerta Y

Una puerta Y ¡Hagámoslo! La unidad fundamental de VHDL se denomina señal. . Por ahora, supongamos que una señal puede ser un 0 o un 1 (en realidad, hay otras posibilidades, pero llegaremos a eso). Aquí hay algo de lógica VHDL básica:

signal and_gate : std_logic; and_gate <= input_1 and input_2;

La primera línea de código define una señal de tipo std_logic y se llama and_gate. Std_logic es el tipo que se usa más comúnmente para definir señales, pero hay otros sobre los que aprenderá. Este código generará una puerta AND con una sola salida (and_gate) y 2 entradas (input_1 y input_2). La palabra clave "y" está reservada en VHDL. El operador <=se conoce como operador de asignación. Cuando analices verbalmente el código anterior, puedes decir en voz alta:"La señal y_gate OBTIENE input_1 y ed con input_2".

Ahora puede que se esté preguntando de dónde vienen input_1 y input_2. Bueno, como su nombre lo indica, son entradas de este archivo, por lo que debe informar a las herramientas sobre ellas. Las entradas y salidas de un archivo se definen en una entidad . Una entidad contiene un puerto que define todas las entradas y salidas de un archivo. Creemos una entidad simple:

entity example_and is

port (

input_1 : in std_logic;

input_2 : in std_logic;

and_result : out std_logic

);

end example_and;

Esta es su entidad básica. Define una entidad llamada example_and y 3 señales, 2 entradas y 1 salida, todas de tipo std_logic. Se necesita otra palabra clave de VHDL para completar esto y es arquitectura. . Una arquitectura se utiliza para describir la funcionalidad de una entidad en particular. Piense en ello como un trabajo de tesis:la entidad es la tabla de contenido y la arquitectura es el contenido. Creemos una arquitectura para esta entidad:

architecture rtl of example_and is signal and_gate : std_logic; begin and_gate <= input_1 and input_2; and_result <= and_gate; end rtl;

El código anterior define una arquitectura llamada rtl de entidad example_and. Todas las señales que utiliza la arquitectura deben definirse entre las palabras clave "es" y "comenzar". La lógica de la arquitectura real se encuentra entre las palabras clave "comienzo" y "final". Ya casi ha terminado con este archivo. Una última cosa que debe decirle a las herramientas es qué biblioteca usar. Una biblioteca define cómo se comportan ciertas palabras clave en su archivo. Por ahora, dé por sentado que necesita tener estas 2 líneas en la parte superior de su archivo:

library ieee; use ieee.std_logic_1164.all;

¡Felicidades! Ha creado su primer archivo VHDL. Puede ver el archivo completo aquí:

library ieee;

use ieee.std_logic_1164.all;

entity example_and is

port (

input_1 : in std_logic;

input_2 : in std_logic;

and_result : out std_logic

);

end example_and;

architecture rtl of example_and is

signal and_gate : std_logic;

begin

and_gate <= input_1 and input_2;

and_result <= and_gate;

end rtl;

¿Parece que tuviste que escribir mucho código solo para crear una puerta estúpida? En primer lugar, y las puertas no son estúpidas. En segundo lugar, tienes razón; VHDL es un lenguaje muy detallado. Acostúmbrese al hecho de que hacer algo que era muy fácil en el software le llevará mucho más tiempo en un HDL como Verilog o VHDL. ¡Pero solo pídale a algún tipo de software que intente generar una imagen en un monitor VGA que muestre el Juego de la vida de Conway y observe cómo su cabeza da vueltas con asombro! Por cierto, ese video se crea con VHDL y un FPGA. ¡Podrás hacerlo muy pronto!

VHDL

- Registros:ejemplo de VHDL

- Variables - Ejemplo de VHDL

- Introducción a la estereolitografía (SLA)

- Introducción a la aleación de titanio

- Introducción a los circuitos de CC

- Introducción a los circuitos de CA

- Introducción a SPICE

- Tutorial C

- Tutorial de Verilog

- Introducción a los armónicos:Parte 1

- Introducción a SINUMERIK 808D:tutorial en vídeo torneado, parte 1