Las herramientas de software migran el código de la GPU a FPGA para aplicaciones de inteligencia artificial

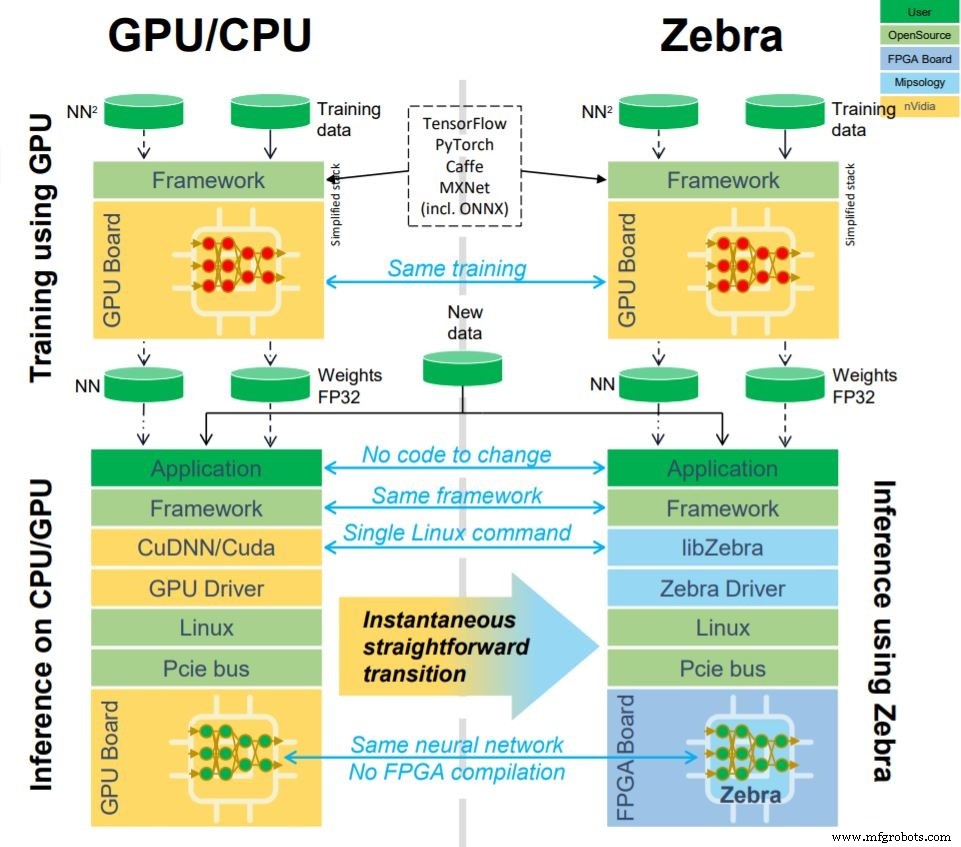

La startup de software de IA, Mipsology, está trabajando con Xilinx para permitir que las FPGA reemplacen a las GPU en las aplicaciones de aceleración de IA utilizando solo un comando adicional. El software de "esfuerzo cero" de Mipsology, Zebra, convierte el código de la GPU para que se ejecute en el motor de cómputo AI de Mipsology en una FPGA sin ningún cambio de código ni necesidad de reentrenamiento.

Xilinx anunció hoy que enviará a Zebra la última versión de sus tarjetas Alveo U50 para el centro de datos. Zebra ya admite la aceleración de inferencias en otras placas Xilinx, incluidas Alveo U200 y Alveo U250.

La última versión de la tarjeta aceleradora de centro de datos Alveo U50 de Xilinx ahora viene con el software Zebra de Mipsology para la conversión del código AI de la GPU para que se ejecute en FPGA (Imagen:Xilinx)

“El nivel de aceleración que Zebra aporta a nuestras tarjetas Alveo avergüenza a los aceleradores de CPU y GPU”, dijo Ramine Roane, vicepresidente de marketing de Xilinx. “Combinado con Zebra, Alveo U50 satisface las necesidades de flexibilidad y rendimiento de las cargas de trabajo de IA y ofrece ventajas de rendimiento de alto rendimiento y baja latencia para cualquier implementación”.

Plug-and-play

Históricamente, los FPGA se consideraban notoriamente difíciles de programar para los no especialistas, pero Mipsology quiere convertir los FPGA en una solución plug-and-play que sea tan fácil de usar como una CPU o GPU. La idea es facilitar al máximo el cambio de otros tipos de aceleración a FPGA.

“La mejor manera de ver [Mipsology] es que hacemos el software que va encima de los FPGA para hacerlos transparentes de la misma manera que Nvidia hizo Cuda CuDNN para hacer que la GPU sea completamente transparente para los usuarios de IA”, dijo el CEO de Mipsology, Ludovic Larzul. , en una entrevista con EE Times .

Fundamentalmente, esto puede ser realizado por no expertos, sin experiencia profunda en IA o habilidades FPGA, ya que no se necesita reentrenamiento de modelos para la transición.

"La facilidad de uso es muy importante, porque cuando miras los proyectos de IA de las personas, a menudo no tienen acceso al equipo de IA que diseña la red neuronal", dijo Larzul. “Por lo general, si alguien pone en marcha un sistema de robots o un sistema de videovigilancia ... tienen otros equipos u otras partes que desarrollan las redes neuronales y los capacitan. Y una vez que obtienen [el modelo capacitado], no quieren cambiarlo porque no tienen la experiencia ".

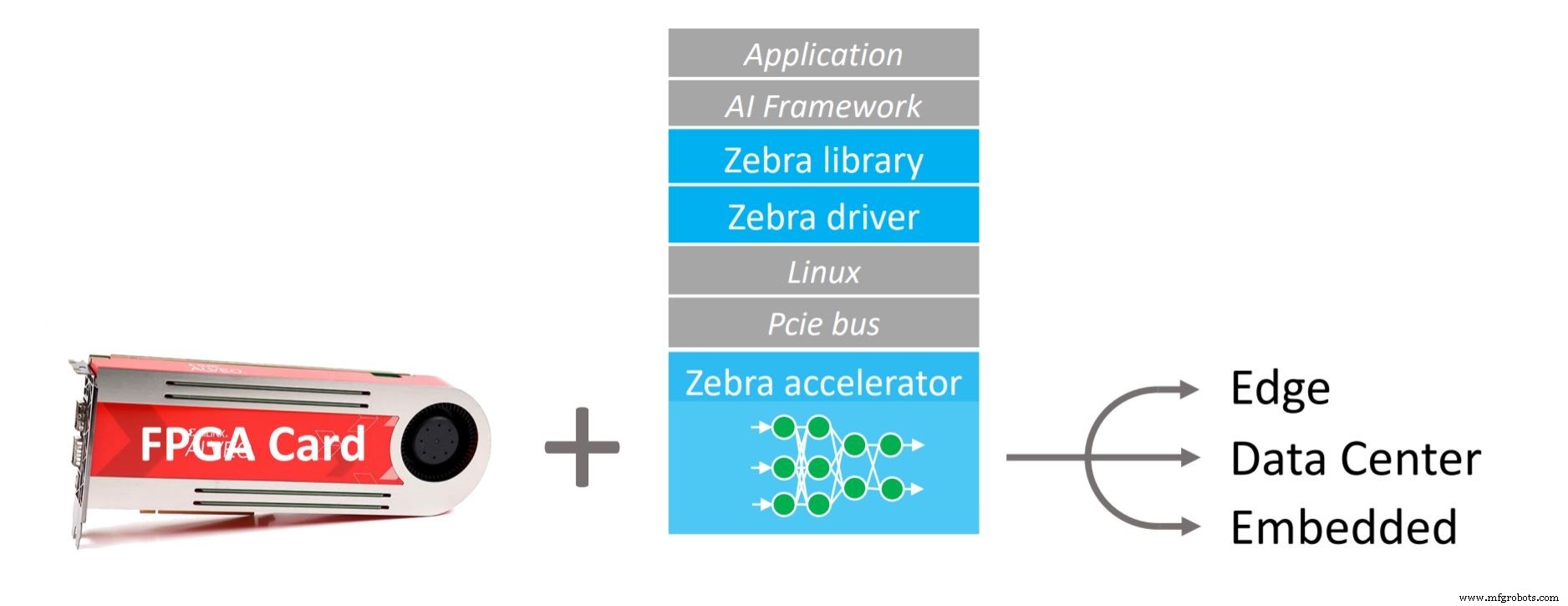

Pila de Zebra. La tecnología es aplicable en centros de datos, aplicaciones de borde e integradas (Imagen:Mipsology)

Versus Vitis

¿Por qué Xilinx admitiría software de terceros cuando ya tiene una solución integral destinada a hacer que los FPGA sean accesibles tanto para los científicos de datos como para los desarrolladores de software (es decir, Vitis)?

“El tono en una oración es:lo estamos haciendo mejor”, dijo Larzul. “Otra oración sería:la nuestra funciona”.

Mipsology no usa ninguna parte de Vitis ni se vincula con él de ninguna manera, ni usa XDNN, el motor acelerador de redes neuronales de Xilinx. Mipsology tiene su propio motor de cómputo dentro de Zebra, que admite los modelos de redes neuronales convolucionales (CNN) existentes de los clientes, a diferencia de XDNN, que según Larzul tiene soporte para muchas demostraciones, pero es menos adecuado para redes neuronales personalizadas. Esto, dijo, hizo que poner en funcionamiento redes personalizadas con XDNN fuera "doloroso". Si bien XDNN puede competir en aplicaciones donde no existe una amenaza de las GPU, Zebra está diseñado para permitir que las FPGA se enfrenten directamente a las GPU en función del rendimiento, el costo y la facilidad de uso.

Pila de Zebra en detalle. El objetivo es hacer que las FPGA sean un cambio más simple de las GPU o CPU para la aceleración de la IA al ocultar el hardware tanto como sea posible (Imagen:Mipsology)

La motivación de la mayoría de los clientes para cambiar las soluciones de GPU es el costo, dijo Larzul.

“Quieren reducir el costo del hardware, pero no quieren tener que rediseñar la red neuronal”, dijo. "Hay un costo no recurrente [que se evita] porque podemos reemplazar las GPU de manera transparente y no hay reentrenamiento o modificación de la red neuronal".

Los FPGA también ofrecen confiabilidad, en parte porque son menos agresivos con los bienes raíces de silicio y, a menudo, funcionan más fríos que otros tipos de aceleradores, incluidas las GPU, según Larzul. Esto es especialmente importante en el centro de datos donde los costos de mantenimiento a largo plazo son significativos.

“El costo total de propiedad no es solo el precio de la placa”, dijo Larzul. "También existe el precio de asegurarse de que el sistema esté en funcionamiento".

Zebra también tiene como objetivo hacer que los FPGA compitan en rendimiento. Si bien los FPGA generalmente ofrecen menos TOPS (tera operaciones por segundo) que otros aceleradores, pueden usar esos TOPS de manera más eficiente gracias al motor de cómputo cuidadosamente diseñado de Zebra, dijo Larzul.

Ludovic Larzul (Imagen:Mipsology)

“Eso es algo que la mayoría de las empresas emergentes de ASIC que aceleran la IA han olvidado:están haciendo una gran pieza de silicio, tratando de incluir más TOPS, pero no han pensado en cómo mapear su red en eso para que sea eficiente ”, Dijo, y señaló que el motor basado en FPGA de Zebra es capaz de procesar más imágenes por segundo que una GPU con 6 veces la cantidad de TOPS.

¿Cómo se logra esto? Si bien Larzul no dio detalles exactos, dijo que no dependen de la poda, ya que la reducción de precisión es demasiado grande para ser aceptable sin reentrenamiento. No utilizan cuantificación extrema (por debajo de 8 bits) por la misma razón.

El motor de Zebra acelera las CNN, que en la actualidad se utilizan principalmente en aplicaciones de procesamiento de imágenes y videos, pero Zebra también se puede aplicar a BERT (el modelo de procesamiento del lenguaje natural de Google), que utiliza conceptos matemáticos similares. Las iteraciones futuras de Zebra pueden cubrir otros tipos de redes neuronales, incluidas LSTM (memoria larga a corto plazo) y RNN (redes neuronales recurrentes), pero esto es más difícil de lograr ya que las RNN son matemáticamente más diversas.

Equipo de EVE

Mipsology se fundó en 2015, con alrededor de 30 personas trabajando en I + D en Francia y un pequeño equipo en California que cubre principalmente el desarrollo empresarial. La compañía ha recibido fondos por un total de $ 7 millones, $ 2 millones de los cuales fueron un premio de un concurso de innovación del gobierno francés en 2019.

El equipo central de Mipsology es de EVE, una empresa de emuladores ASIC adquirida por Synopsys en 2012 para sus productos de verificación asistida por hardware ZeBu (Zero Bug), que en ese momento competía con la plataforma de verificación Palladium de Cadence. Según Larzul, la tecnología EVE fue utilizada por casi todas las principales empresas de ASIC para verificar los ASIC durante el ciclo de diseño; esta tecnología se basó en miles de FPGA conectados entre sí para reproducir el comportamiento ASIC.

Mipsology tiene 12 patentes pendientes y trabaja en estrecha colaboración con Xilinx, además de ser compatible con tarjetas aceleradoras de terceros, como tarjetas Western Digital de factor de forma pequeño (SFF U.2) y tarjetas Advantech como Vega-4001.

>> Este artículo se publicó originalmente el nuestro sitio hermano, EE Times.

Incrustado

- ST:kit de evaluación de elementos seguros con software listo para usar para aplicaciones de TI e IoT

- PPA para aplicaciones de movilidad eléctrica

- Aplicaciones ideales para actuadores neumáticos

- 4 tipos de herramientas para aplicaciones de minería

- Aplicaciones típicas para frenos de pinza

- Aplicaciones militares para aleaciones de bronce

- Aplicaciones para Aluminio Bronce C63200

- ¿Para qué se utiliza Monel?

- Herramientas de corte para mecanizado de precisión

- La importancia de la interoperabilidad en las aplicaciones de software 3D

- ¿Cuál es el código HS para bomba hidráulica?