El procesamiento acústico en tiempo real exitoso requiere una planificación cuidadosa

El procesamiento acústico en tiempo real de baja latencia es un factor clave en muchas aplicaciones de procesamiento integrado, entre ellas el preprocesamiento de voz, el reconocimiento de voz y la cancelación activa de ruido (ANC). A medida que los requisitos de rendimiento en tiempo real aumentan constantemente dentro de estos dominios de aplicaciones, los desarrolladores deben adoptar una mentalidad estratégica para adaptarse adecuadamente a estas necesidades. Dado el rendimiento sustancial que ofrecen muchos sistemas más grandes en chips, puede ser tentador simplemente cargar estos dispositivos con cualquier tarea adicional que surja, pero es importante comprender que la latencia y el determinismo son elementos críticos que pueden conducir fácilmente a un sistema en tiempo real importante. problemas si no se consideran cuidadosamente. Este artículo explorará los problemas que los diseñadores deben considerar al elegir entre un SoC y un DSP de audio dedicado para evitar sorpresas desagradables en sus sistemas acústicos en tiempo real.

Los sistemas acústicos de baja latencia cubren una amplia gama de aplicaciones. Por ejemplo, solo en el espacio automotriz, la baja latencia es fundamental para las zonas de audio personales, la cancelación de ruido de la carretera y los sistemas de comunicación en el automóvil, por nombrar algunos.

Con la tendencia emergente de electrificación de vehículos, ANC se vuelve aún más importante porque no hay motor de combustión que genere un ruido notable. Por lo tanto, los sonidos asociados con la interfaz de automóvil a carretera se vuelven mucho más perceptibles y ofensivos. Reducir este ruido no solo crea una experiencia de conducción más cómoda, sino que también reduce la fatiga del conductor. Existen numerosos desafíos asociados con la implementación de un sistema acústico de baja latencia en un SoC en lugar de en un DSP de audio dedicado. Estos incluyen problemas de latencia, escalabilidad, capacidad de actualización, consideraciones de algoritmos, aceleración de hardware y soporte al cliente. Examinemos cada uno de estos a su vez.

Latencia

El tema de la latencia en los sistemas de procesamiento acústico en tiempo real es importante. Si el procesador no puede mantenerse al día con el movimiento de datos en tiempo real y las demandas computacionales del sistema, pueden producirse caídas de audio inaceptables.

Por lo general, los SoC tienen pequeñas SRAM en el chip y, en consecuencia, deben depender de la caché para la mayoría de los accesos a la memoria local. Esto introduce una disponibilidad no determinista de código y datos, y también aumenta la latencia de procesamiento. Para una aplicación en tiempo real como ANC, esto por sí solo puede ser un factor decisivo. Sin embargo, también existe el hecho de que los SoC ejecutan sistemas operativos en tiempo no real que administran cargas multitarea pesadas. Esto amplifica la característica operativa no determinista del sistema, lo que hace que sea muy difícil admitir un procesamiento acústico relativamente complejo en un entorno multitarea.

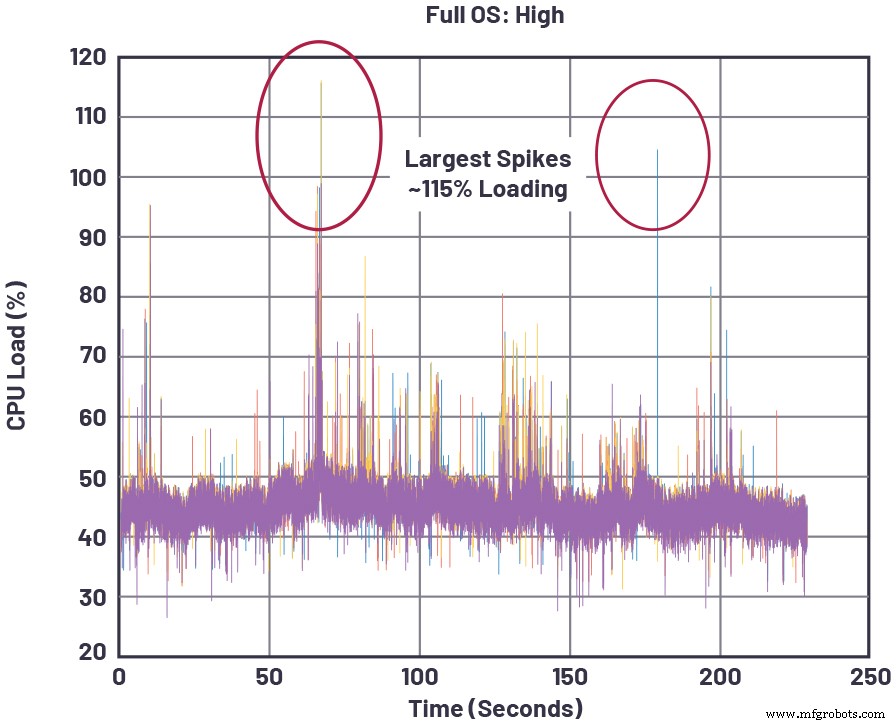

La Figura 1 muestra un ejemplo concreto de un SoC que ejecuta una carga de procesamiento de audio en tiempo real, donde la carga de la CPU aumenta a medida que se atienden las tareas de SoC de mayor prioridad. Estos picos pueden ocurrir, por ejemplo, debido a actividades centradas en SoC, como la representación de medios, la navegación o la ejecución de aplicaciones en el sistema. Siempre que los picos superan el 100% de la carga de la CPU, el SoC ya no funciona en tiempo real, y esto dará como resultado pérdidas de audio.

haz clic para ver la imagen en tamaño completo

Figura 1:Cargas instantáneas de CPU para un SoC representativo que ejecuta un alto procesamiento de memoria de audio además de otras tareas [1]. (Fuente:Analog Devices)

Los DSP de audio, por otro lado, están diseñados para una baja latencia en toda la ruta de procesamiento de la señal, desde la entrada de audio muestreada hasta la salida del altavoz compuesto (por ejemplo, audio + antirruido). La instrucción L1 y la SRAM de datos, la memoria de ciclo único más cercana al núcleo del procesador, es lo suficientemente amplia para admitir muchos algoritmos de procesamiento sin descargar datos intermedios a la memoria fuera del chip. Además, la memoria L2 en el chip (más alejada del núcleo pero con un acceso mucho más rápido que la DRAM fuera del chip) ayuda a proporcionar un búfer para las operaciones de datos intermedias cuando se excede el almacenamiento L1 SRAM. Por último, los DSP de audio suelen ejecutar un sistema operativo en tiempo real (RTOS) que garantiza que los datos entrantes se puedan procesar y enviar a su destino de destino antes de que lleguen nuevos datos de entrada, lo que garantiza que los búferes de datos no se desborden durante la operación en tiempo real.

La latencia real en el arranque del sistema, a menudo medida por la disponibilidad de tiempo de audio, también puede ser una métrica importante, especialmente en sistemas automotrices donde las advertencias audibles deben transmitirse dentro de una determinada ventana desde el inicio. En el mundo de SoC, donde es típico tener una secuencia de arranque larga que implica abrir el sistema operativo para todo el dispositivo, puede ser difícil o imposible cumplir con este requisito de arranque. Por otro lado, un DSP de audio independiente que ejecuta su propio RTOS sin verse afectado por otras prioridades ajenas al sistema se puede optimizar para un arranque rápido que satisfaga cómodamente el requisito de tiempo de audio.

Escalabilidad

Si bien las preocupaciones sobre la latencia son problemáticas para los SoC en aplicaciones como el control de ruido, otra deficiencia clave para los SoC que aspiran a realizar un procesamiento acústico es la escalabilidad. En otras palabras, los SoC que controlan sistemas grandes (como clústeres y unidades de cabecera automotriz) con muchos subsistemas dispares no pueden escalar fácilmente de las necesidades de audio de gama baja a alta porque existe un conflicto constante entre las necesidades de escalabilidad de cada componente del subsistema, lo que requiere compensaciones en la utilización general de SoC. Por ejemplo, si un SoC de cabecera se conecta a un sintonizador remoto y, en los modelos automotrices, ese sintonizador necesita escalar de unos pocos canales a muchos canales, la configuración de cada canal amplificará las preocupaciones en tiempo real mencionadas anteriormente. Esto se debe a que cada característica adicional bajo el control del SoC cambia el comportamiento en tiempo real del SoC y la disponibilidad de recursos de los componentes arquitectónicos clave utilizados por múltiples funciones. Estos recursos incluyen aspectos como el ancho de banda de la memoria, los ciclos del núcleo del procesador y las ranuras de arbitraje de la estructura del bus del sistema.

Aparte de la preocupación por la conexión de otros subsistemas en el SoC multitarea, el subsistema acústico en sí tiene sus propios problemas de escalabilidad. Existe una escala de gama baja a alta (por ejemplo, aumentar la cantidad de canales de micrófono y altavoz en una aplicación ANC), y también está la escala de experiencia de audio, desde la decodificación de audio básica y la reproducción estéreo hasta la virtualización 3D y otras características premium. Aunque estos requisitos no comparten las limitaciones de tiempo real de los sistemas ANC, no obstante, se relacionan directamente con la elección del procesador de audio para un sistema.

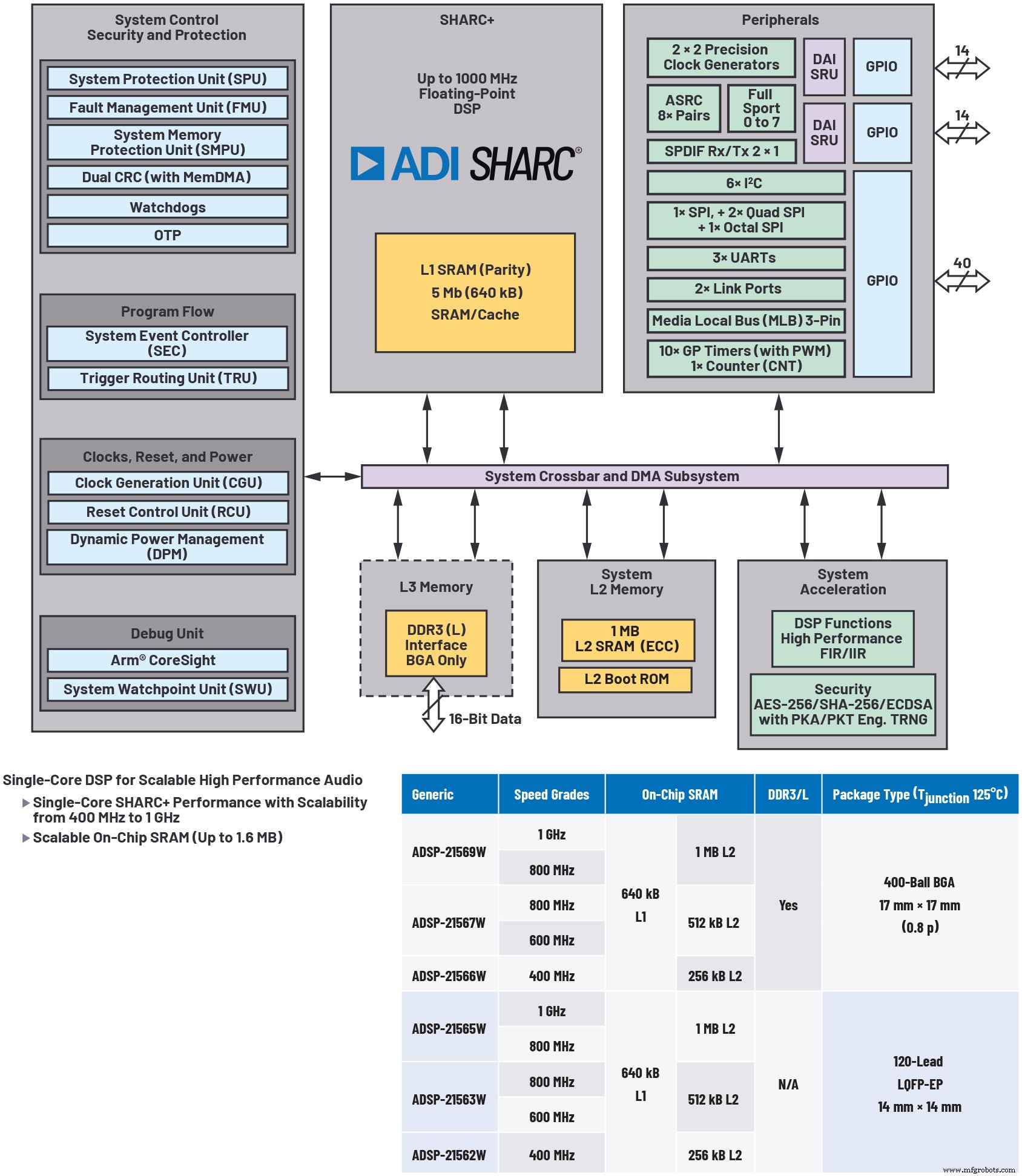

La utilización de un DSP de audio independiente como coprocesador de un SoC ayuda a resolver el problema de escalabilidad del audio, permite el diseño modular del sistema y optimiza el costo (consulte la Figura 2). El SoC puede enfocarse mucho menos en las necesidades de procesamiento acústico en tiempo real del sistema más grande, en lugar de descargar ese procesamiento al DSP de audio de baja latencia. Además, los DSP de audio que ofrecen varios niveles de precio / rendimiento / memoria diferentes en una hoja de ruta completa compatible con códigos y pines ofrecen la máxima flexibilidad para que los diseñadores de sistemas ajusten la oferta de rendimiento de audio para un nivel de producto determinado.

haz clic para ver la imagen en tamaño completo

Figura 2:ilustrativa de un procesador de audio altamente escalable. El uso de un procesador de audio independiente, como el DSP ADSP-2156x que se muestra aquí, ayuda a resolver el problema de escalabilidad del audio, permite el diseño modular del sistema y optimiza el costo. (Fuente:Analog Devices)

Capacidad de actualización

A medida que las actualizaciones de firmware por aire se vuelven más comunes en los vehículos de hoy, la capacidad de actualización para emitir parches críticos o proporcionar nuevas funciones se vuelve cada vez más importante. Esto puede causar problemas importantes para un SoC debido al aumento de las dependencias entre sus diversos subsistemas. Primero, en los SoC, múltiples subprocesos de procesamiento y movimiento de datos compiten por recursos. Esto aumenta la competencia por los MIPS del procesador y la memoria cuando se agregan nuevas funciones, especialmente durante las ráfagas de actividad máxima. Desde la perspectiva del audio, las adiciones de funciones en otros dominios de control de SoC pueden tener un efecto impredecible en el rendimiento acústico en tiempo real. Un efecto secundario de esta situación es que la nueva funcionalidad debe someterse a pruebas cruzadas en todos los planos operativos, lo que da como resultado una miríada de permutaciones entre varios modos operativos de los subsistemas competidores. Por lo tanto, la verificación de software aumenta exponencialmente para cada paquete de actualización.

Visto desde un ángulo diferente, se podría decir que las mejoras en el rendimiento de audio del SoC dependen de los MIPS de SoC disponibles, además de las hojas de ruta de funciones para los otros subsistemas controlados por el SoC.

Desarrollo y rendimiento de algoritmos

Debería ser evidente que, cuando se trata de desarrollar algoritmos acústicos en tiempo real, los DSP de audio están diseñados específicamente para la tarea. Como diferenciador significativo de los SoC, los DSP de audio independientes pueden ofrecer entornos de desarrollo gráfico que permiten a los ingenieros con una experiencia mínima en codificación DSP agregar procesamiento acústico de calidad en sus diseños. Este tipo de herramienta puede reducir los costos de desarrollo al reducir el tiempo de desarrollo sin sacrificar la calidad o el rendimiento.

Como ejemplo, el entorno de desarrollo de audio gráfico SigmaStudio de ADI ofrece una amplia variedad de algoritmos de procesamiento de señales integrados en una interfaz gráfica de usuario intuitiva (GUI), lo que permite la creación de flujos de señales de audio complicados (consulte la Figura 3). También admite la configuración gráfica A2B para el transporte de audio, lo que ayuda en gran medida a catalizar el desarrollo del sistema acústico en tiempo real.

haz clic para ver la imagen en tamaño completo

Figura 3:Los entornos de desarrollo de audio gráfico como SigmaStudio de Analog Devices brindan acceso a una amplia variedad de algoritmos de procesamiento de señales integrados en una interfaz gráfica de usuario intuitiva (GUI), lo que simplifica la creación de flujos de señales de audio complicados. (Fuente:Analog Devices)

Funciones de hardware compatibles con audio

Además de una arquitectura de núcleo de procesador que está diseñada específicamente para cómputos de punto flotante paralelo eficientes y acceso a datos, los DSP de audio a menudo tienen aceleradores multicanal dedicados para primitivas de audio comunes, como transformadas rápidas de Fourier (FFT), respuesta de impulso finita e infinita (FIR e IIR). ) filtrado y conversión asincrónica de frecuencia de muestreo (ASRC). Estos permiten el filtrado de audio en tiempo real, el muestreo y la conversión del dominio de frecuencia fuera de la CPU central, lo que aumenta el rendimiento central efectivo. Además, pueden facilitar un modelo de programación flexible y fácil de usar debido a su arquitectura optimizada y capacidades de gestión de flujo de datos.

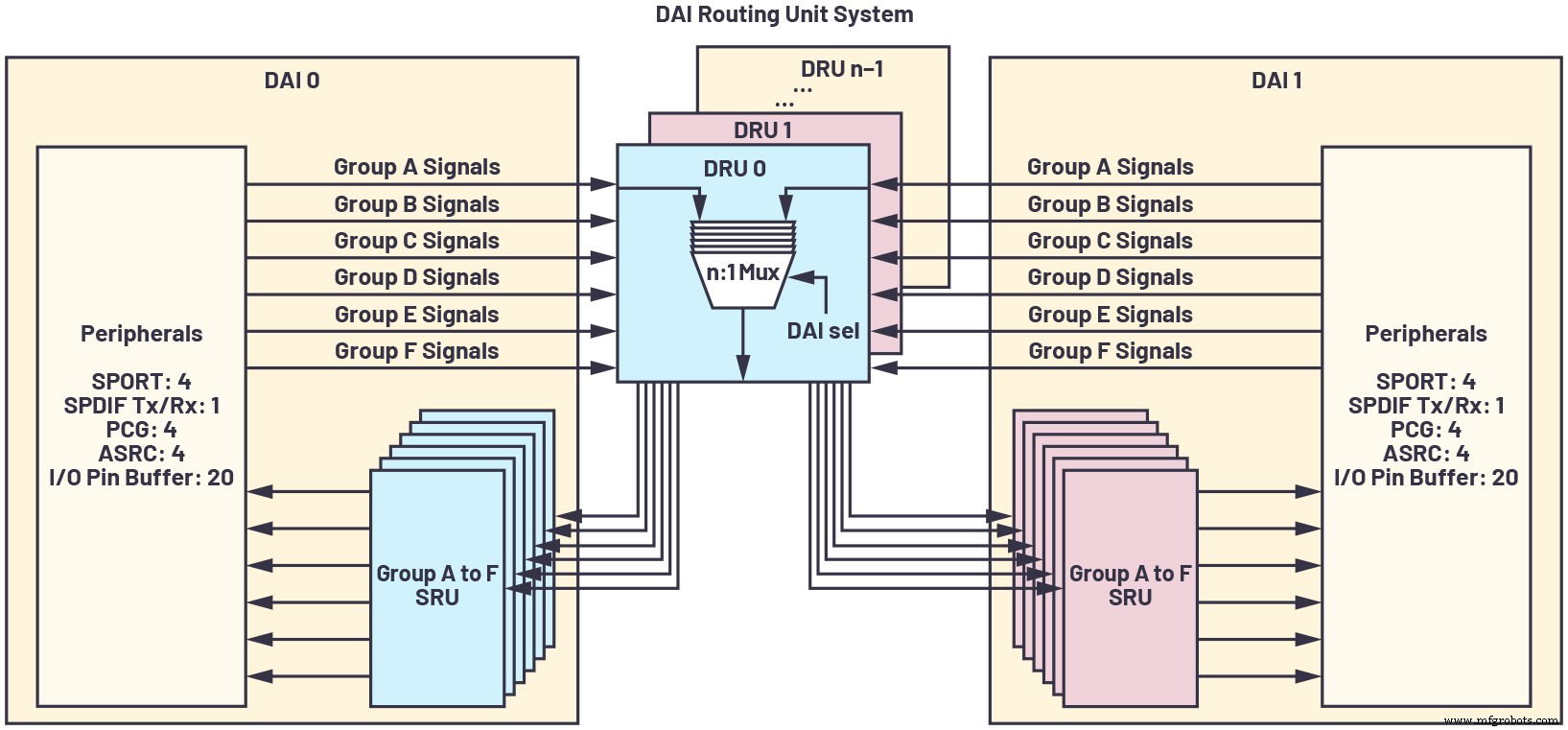

Debido a la proliferación de recuentos de canales de audio, flujos de filtros, frecuencias de muestreo y similares, es importante tener una interfaz de pines configurable al máximo que permita la conversión de frecuencia de muestreo en línea, sincronización de precisión y puertos serie síncronos de alta velocidad para enrutar datos de manera eficiente y evitar latencia adicional o lógica de interfaz externa. La interconexión de audio digital (DAI) de los procesadores de la familia SHARC de ADI ilustra esta capacidad, como se muestra en la Figura 4.

haz clic para ver la imagen en tamaño completo

Figura 4:Una interconexión de audio digital (DAI) es una interfaz de clavija configurable al máximo que permite la conversión de frecuencia de muestreo en línea, sincronización de precisión y puertos serie síncronos de alta velocidad para enrutar datos de manera eficiente y evitar latencia adicional o lógica de interfaz externa. (Fuente:Analog Devices)

Atención al cliente

Un aspecto del desarrollo con un procesador integrado que a menudo se pasa por alto es la asistencia al cliente para el dispositivo.

Aunque los proveedores de SoC promueven la ejecución de algoritmos acústicos en sus productos DSP integrados, esto conlleva varias responsabilidades en la práctica. Por un lado, el soporte de los proveedores suele ser más complejo, ya que la experiencia acústica no suele ser el dominio del desarrollo de aplicaciones de SoC. En consecuencia, tiende a haber un apoyo débil para los clientes que buscan desarrollar sus propios algoritmos acústicos en la tecnología DSP en chip del SoC. Más bien, el proveedor puede ofrecer algoritmos estándar y cobrar una NRE significativa para transferir algoritmos acústicos a uno o más núcleos del SoC. Aun así, no hay garantía de éxito, especialmente si el proveedor no ofrece un marco de software maduro y de baja latencia. Por último, el ecosistema de terceros para el procesamiento acústico basado en SoC tiende a ser bastante frágil, ya que no es un enfoque del SoC, sino más bien una función con soporte oportunista.

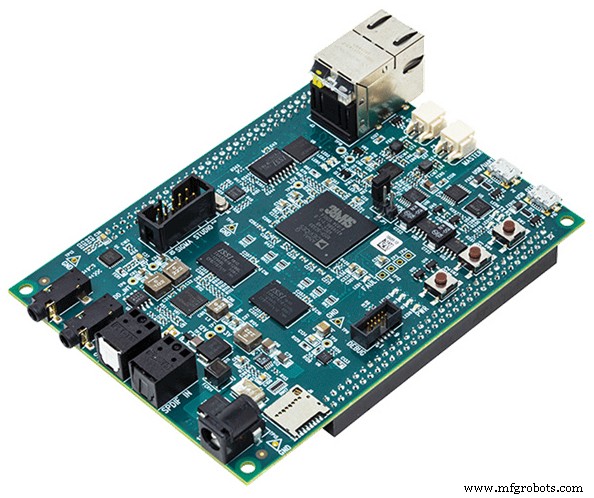

Un DSP de audio especialmente diseñado conlleva un ecosistema mucho más sólido para el desarrollo de sistemas acústicos complejos, desde bibliotecas de algoritmos optimizados y controladores de dispositivos hasta sistemas operativos en tiempo real y herramientas de desarrollo fáciles de usar. Las plataformas de referencia centradas en el audio (como la plataforma del módulo de audio SHARC de ADI, que se muestra en la Figura 5) que aceleran el tiempo de comercialización son una rareza para los SoC, pero bastante comunes en el dominio DSP de audio independiente.

Figura 5:Los DSP suelen proporcionar una plataforma de desarrollo centrada en el audio como la que se muestra aquí Módulo de audio SHARC (SAM). (Fuente:Analog Devices)

El diseño de sistemas acústicos en tiempo real implica una planificación estratégica deliberada de los recursos del sistema y no se puede administrar simplemente asignando el margen de procesamiento sobrante en un SoC multitarea. En cambio, es probable que un DSP de audio independiente optimizado para procesamiento de baja latencia conduzca a una mayor solidez, menor tiempo de desarrollo y una escalabilidad óptima para adaptarse a las necesidades futuras del sistema y niveles de rendimiento.

Referencia

[1] Paul Beckmann. "Procesadores SOC multinúcleo:rendimiento, análisis y optimización". Conferencia internacional de 2017 AES sobre audio automotriz, agosto de 2017.

David Katz tiene 30 años de experiencia en diseño de sistemas analógicos, digitales e integrados. Es director de arquitectura de sistemas para infoentretenimiento automotriz en Analog Devices, Inc. Ha publicado a nivel internacional cerca de 100 artículos de procesamiento integrado y ha presentado varios artículos en conferencias en el campo. Anteriormente, trabajó en Motorola, Inc., como ingeniero de diseño senior en grupos de automatización de fábricas y módem de cable. David tiene un B.S. y un M.Eng. en ingeniería eléctrica de la Universidad de Cornell. Puede ser contactado en [email protected].

David Katz tiene 30 años de experiencia en diseño de sistemas analógicos, digitales e integrados. Es director de arquitectura de sistemas para infoentretenimiento automotriz en Analog Devices, Inc. Ha publicado a nivel internacional cerca de 100 artículos de procesamiento integrado y ha presentado varios artículos en conferencias en el campo. Anteriormente, trabajó en Motorola, Inc., como ingeniero de diseño senior en grupos de automatización de fábricas y módem de cable. David tiene un B.S. y un M.Eng. en ingeniería eléctrica de la Universidad de Cornell. Puede ser contactado en [email protected]. Contenidos relacionados:

- Combinando hardware y software para un mejor audio

- Cómo los procesadores de borde de audio permiten la integración de voz en dispositivos de IoT

- AI encuentra su voz en la cadena de audio

- Las soluciones Adaptive ANC brindan capacidades de audio mejoradas

- Consideraciones de diseño para sistemas de comando de voz de bajo consumo y siempre activos

Para obtener más información sobre Embedded, suscríbase al boletín informativo semanal por correo electrónico de Embedded.

Incrustado

- ST:Las MCU inalámbricas de doble núcleo STM32WB ofrecen un rendimiento en tiempo real de consumo ultrabajo

- Logic-X lanza una nueva marca de productos de procesamiento de sensores COTS

- El reloj en tiempo real Maxim nanoPower extiende la vida útil de la batería en wearables, POS

- La arquitectura del chip AI apunta al procesamiento de gráficos

- El uso de varios chips de inferencia requiere una planificación cuidadosa

- El procesador multinúcleo integra la unidad de procesamiento neuronal

- Los relojes automotrices en tiempo real cuentan con un amplio rango de temperatura

- Seco:sistemas de procesamiento heterogéneos basados en Xilinx Zynq Ultrascale + MPSoCs

- Planificación de movimiento en tiempo real para vehículos autónomos en varias situaciones, en entornos urbanos simulados

- Las iniciativas digitales en el taller se benefician de una planificación cuidadosa

- ¿Su sistema es inteligente? El valor de procesar datos de planta en tiempo real