Diseño incrustado con FPGA:lenguajes de implementación

Nota del editor:a medida que continúan surgiendo algoritmos avanzados para diseños de productos inteligentes, los desarrolladores a menudo se encuentran luchando para implementar sistemas integrados capaces de satisfacer las demandas de procesamiento asociadas de estos algoritmos. Los FPGA pueden ofrecer el rendimiento requerido, pero el diseño con FPGA se ha considerado durante mucho tiempo limitado al ámbito de los expertos en programación de FPGA. Sin embargo, hoy en día, la disponibilidad de FPGA más potentes y entornos de desarrollo más efectivos ha hecho que el desarrollo de FPGA sea ampliamente accesible. En este extracto, Capítulo 4 del libro Architecting High-Performance Embedded Systems, el autor ofrece una revisión completa de los dispositivos FPGA, los lenguajes de implementación y el proceso de desarrollo de FPGA, así como un tutorial detallado de cómo comenzar a implementar FPGA en su propio diseño. El extracto completo se presenta en la siguiente serie de entregas:

Nota del editor:a medida que continúan surgiendo algoritmos avanzados para diseños de productos inteligentes, los desarrolladores a menudo se encuentran luchando para implementar sistemas integrados capaces de satisfacer las demandas de procesamiento asociadas de estos algoritmos. Los FPGA pueden ofrecer el rendimiento requerido, pero el diseño con FPGA se ha considerado durante mucho tiempo limitado al ámbito de los expertos en programación de FPGA. Sin embargo, hoy en día, la disponibilidad de FPGA más potentes y entornos de desarrollo más efectivos ha hecho que el desarrollo de FPGA sea ampliamente accesible. En este extracto, Capítulo 4 del libro Architecting High-Performance Embedded Systems, el autor ofrece una revisión completa de los dispositivos FPGA, los lenguajes de implementación y el proceso de desarrollo de FPGA, así como un tutorial detallado de cómo comenzar a implementar FPGA en su propio diseño. El extracto completo se presenta en la siguiente serie de entregas:

1:Recursos de hardware

2:Lenguajes de implementación (este artículo)

3:Proceso de desarrollo

4:Creación de un proyecto

5:Implementación

Adaptado de Architecting High-Performance Embedded Systems, por Jim Ledin.

Lenguajes de implementación de FPGA

La implementación de un diseño para una FPGA se reduce en última instancia a utilizar uno o más lenguajes similares a la programación de software para definir la funcionalidad del dispositivo.

Los lenguajes tradicionales utilizados para el desarrollo de FPGA son VHDL y Verilog.

Las herramientas de desarrollo de FPGA de la generación actual generalmente admiten ambos lenguajes junto con la capacidad de definir configuraciones del sistema utilizando técnicas de diagramación de bloques. Algunas suites de herramientas también admiten la definición de la funcionalidad FPGA utilizando los lenguajes de programación tradicionales C y C ++.

VHDL

Lenguaje de descripción de hardware VHSIC ( VHDL ), donde VHSIC significa Very Circuito integrado de alta velocidad , tiene una sintaxis que recuerda al lenguaje de programación Ada. VHDL se desarrolló bajo la dirección del Departamento de Defensa de EE. UU. A partir de 1983.

Como Ada, VHDL tiende a ser bastante detallado y estructurado rígidamente. En términos de lenguaje de programación, VHDL está fuertemente tipado. El lenguaje contiene un conjunto predefinido de tipos de datos base, principalmente booleano, bit, bit_vector, carácter, cadena, entero, real, tiempo y matriz. Todos los demás tipos de datos se definen en términos de los tipos base.

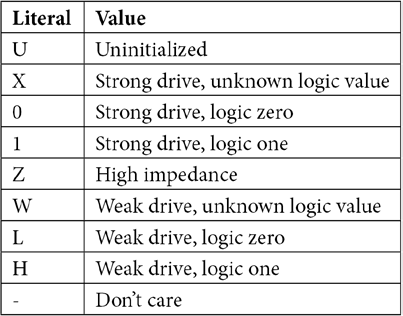

El Instituto de ingenieros eléctricos y electrónicos ha definido un conjunto de bibliotecas VHDL. ( IEEE ) y formalizado como el estándar IEEE 1164, Sistema lógico multivalor para Interoperabilidad del modelo VHDL . Estas bibliotecas definen el conjunto de valores lógicos que se utilizarán en el lenguaje VHDL. Esta biblioteca incluye un tipo llamado std_logic, que representa una señal de 1 bit. Los valores lógicos dentro del tipo std_logic están representados por los caracteres literales que se muestran en la siguiente tabla:

Los valores "fuertes" de 0 y 1 en la figura anterior representan señales conducidas al estado binario especificado. Las señales "débiles" representan señales conducidas en un autobús con múltiples conductores donde cualquier conductor puede imponerse en el autobús, anulando a los otros conductores. El valor Z representa una salida CMOS en el estado de alta impedancia, donde en lugar de conducir el bus a un estado 0 o 1, la salida se desconecta efectivamente del bus y no lo conduce en absoluto. El estado U representa los valores predeterminados para todas las señales. Al realizar la simulación de circuito, se detectará cualquier señal en el estado U, lo que probablemente indica que se está utilizando involuntariamente un valor no inicializado. El estado X está asociado con cables que no tienen salidas que los impulsen. El estado - representa las entradas que no se utilizan y, por lo tanto, no importa en qué estado se encuentren.

Los diseños de circuitos VHDL generalmente comienzan importando las bibliotecas IEEE 1164 a través de las siguientes declaraciones:

biblioteca IEEE;

use IEEE.std_logic_1164.all;

Usaremos VHDL en nuestro ejemplo de proyecto más adelante en este capítulo. Esto no pretende representar una fuerte preferencia por VHDL sobre Verilog. Ambos lenguajes de definición de hardware son totalmente capaces de representar prácticamente cualquier diseño que pueda sintetizarse para una FPGA.

Verilog

El lenguaje de descripción de hardware de Verilog ( HDL ) se introdujo en 1984 y se estandarizó como IEEE 1364 en 2005. En 2009, el estándar Verilog se combinó con SystemVerilog estándar para producir el estándar IEEE 1800-2009. SystemVerilog contiene amplias funciones para realizar la verificación del sistema, además de las características de diseño de hardware presentes en Verilog.

Verilog fue diseñado para parecerse al lenguaje de programación C, incluyendo una precedencia de operador similar y el uso de algunas de las mismas palabras clave de flujo de control, incluyendo if, else, for y while.

Verilog utiliza el concepto de cable para representar estados de señal. Un valor de señal puede tomar cualquiera de los valores 0, 1, no importa (x) o alta impedancia (z), y puede tener una fuerte o débil intensidad de la señal.

Tanto VHDL como Verilog definen subconjuntos de lenguaje que se pueden usar para diseñar circuitos lógicos. Estos subconjuntos se denominan sintetizables subconjuntos de idiomas. Hay disponibles funciones de lenguaje adicionales más allá de los subconjuntos sintetizables para respaldar tareas como la simulación de circuitos. Veremos un ejemplo de esto más adelante en este capítulo.

Las construcciones de lenguaje no sintetizables tienden a comportarse más como lenguajes de programación de software tradicionales. Por ejemplo, un bucle for no sintetizable itera a través de un bloque de código secuencialmente el número especificado de veces, al igual que en un lenguaje de programación normal. Un bucle for sintetizable, por otro lado, se desenrolla efectivamente para generar una colección de construcciones de hardware replicadas que se ejecutan en paralelo representando cada iteración del bucle.

Diagramas de bloques

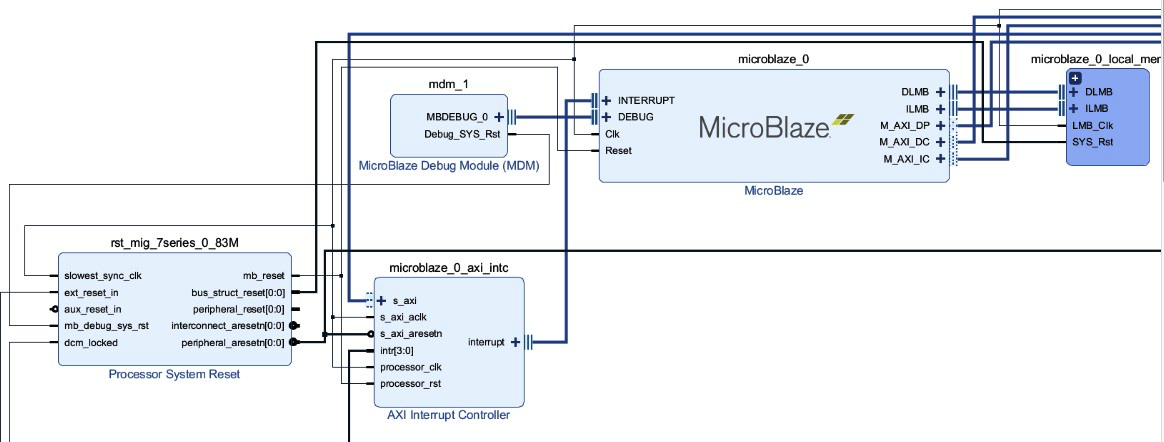

En un nivel de abstracción por encima de los HDL basados en texto, los conjuntos de herramientas de desarrollo de FPGA modernos admiten la configuración rápida de diseños de sistemas que incorporan componentes lógicos complejos como microprocesadores y dispositivos de E / S sofisticados que utilizan un formato de estructura de bloques. Figura 4.2 es un ejemplo de una parte de un diagrama de bloques para un diseño de FPGA de Xilinx que incorpora un procesador suave MicroBlaze:

haz clic para ver la imagen en tamaño completo

Figura 4.2 - Diagrama de bloques que contiene un microprocesador suave MicroBlaze

El procesador MicroBlaze es un núcleo de procesador provisto con el conjunto de herramientas Xilinx Vivado para su uso en diseños FPGA en familias de procesadores, incluido Artix-7.

Si bien el uso de diagramas de bloques proporciona una forma visualmente intuitiva de organizar la instanciación e interconexión de elementos lógicos complejos en un diseño FPGA, es importante recordar que detrás del diagrama, la herramienta de desarrollo genera código VHDL o Verilog para definir los componentes y sus conexiones. El diagrama de bloques es simplemente una interfaz de usuario para administrar la configuración de estos componentes.

Después de desarrollar un diagrama de bloques, puede examinar el código HDL generado, que estará contenido en archivos asociados con el proyecto. En el diagrama de la Figura 4.2 , se genera un archivo llamado design_1_microblaze_0_0_stub.vhdl a partir del diagrama. Este archivo comienza con el siguiente código VHDL:

biblioteca IEEE;

use IEEE.STD_LOGIC_1164.ALL;

diseño de entidad_1_microblaze_0_0 es

Puerto (

Clk:en STD_LOGIC;

Restablecer:en STD_LOGIC;

Interrupción:en STD_LOGIC;

Interrupt_Address:en STD_LOGIC_VECTOR (0 a 31);

Interrupt_Ack:out STD_LOGIC_VECTOR (0 a 1);

Instr_Addr:out STD_LOGIC_VECTOR (0 a 31);

Instr:en STD_LOGIC_VECTOR (0 a 31);

Este código comienza con una referencia a la biblioteca estándar IEEE 1164, luego define una interfaz para el procesador MicroBlaze que expone las señales que esperaría en un microprocesador, incluido el reloj del sistema, el reinicio, la solicitud de interrupción y las entradas vectoriales de interrupción; salidas de dirección de instrucción y reconocimiento de interrupciones; y un bus para las instrucciones recuperadas de la memoria.

Este código utiliza los tipos de datos de la biblioteca IEEE 1164 para señales de un solo bit (STD_LOGIC) y para señales de bus de múltiples bits (STD_LOGIC_VECTOR).

El código de la lista define la interfaz del procesador MicroBlaze, pero no contiene la definición HDL del procesador en sí. Los diseños HDL complejos para componentes como microprocesadores se consideran propiedad intelectual valiosos ( IP ) y las entidades comerciales que desarrollan estos diseños a menudo toman medidas para asegurarse de que no se utilicen sin las licencias adecuadas. Cuando los proveedores distribuyen la propiedad intelectual para que la utilicen sus clientes, es posible que se proporcione en un formato compilado que sea opaco para los usuarios finales. Esto permite a los usuarios incorporar la propiedad intelectual en sus diseños, pero no pueden examinar el HDL utilizado para desarrollarlo. Esto es conceptualmente similar a los desarrolladores de software que publican una biblioteca en forma compilada pero no proporcionan el código fuente.

C / C ++

Varios proveedores ofrecen herramientas de software que traducen los lenguajes de programación tradicionales de alto nivel, a menudo C y C ++, al código HDL para su uso en el desarrollo de FPGA. Este enfoque puede resultar atractivo si tiene un algoritmo complejo en C o C ++ que le gustaría acelerar en una implementación de FPGA. Estas herramientas también permiten a los desarrolladores de software que están familiarizados con C / C ++ comenzar inmediatamente a implementar el código para el uso de FPGA sin necesidad de aprender uno de los HDL.

Si bien las herramientas de desarrollo de FPGA para estos lenguajes de alto nivel son capaces de optimizar significativamente la implementación FPGA resultante del algoritmo de código C / C ++, todavía existe una cierta desconexión en el sentido de que el modelo de ejecución de C / C ++ implica la ejecución secuencial de declaraciones mientras el entorno FPGA nativo consta de componentes de hardware paralelos. El diseño de FPGA resultante del código C / C ++ típicamente se asemeja a una colección de máquinas de estado que administran la ejecución secuencial de las operaciones definidas en las declaraciones del lenguaje de programación. Dependiendo de la disponibilidad de oportunidades para la ejecución paralela dentro del código C / C ++, una implementación de FPGA puede proporcionar una mejora significativa del rendimiento en comparación con ejecutar el mismo código en un procesador tradicional.

En los conjuntos de herramientas de desarrollo de FPGA modernos, todos los métodos de implementación de FPGA descritos en esta sección (VHDL, Verilog, diagramas de bloques y C / C ++) se pueden combinar en un solo diseño, si es necesario. Debido a esto, un miembro del equipo puede preferir trabajar en VHDL mientras que otro usa Verilog. Puede haber razones de gestión de proyectos para desalentar el uso de múltiples HDL dentro de un solo proyecto, pero los lenguajes en sí funcionan juntos en un solo diseño sin problemas. Una razón por la que un gerente de proyecto puede querer evitar el uso de múltiples HDL es que el sostenimiento futuro del esfuerzo requerirá la participación de desarrolladores con habilidades en ambos idiomas.

De manera similar, es posible definir una arquitectura de alto nivel para un proyecto en términos de un diagrama de bloques y luego implementar la funcionalidad detallada del subsistema utilizando el HDL de su elección. En el mismo diseño, también es posible integrar HDL generado a partir de un algoritmo C / C ++. Los arquitectos y desarrolladores de sistemas integrados deben considerar cuidadosamente las implicaciones y seleccionar el método de implementación apropiado para cada parte de un diseño de FPGA.

La siguiente sección presentará los pasos en el proceso de desarrollo estándar de FPGA.

Reproducido con permiso de Packt Publishing. Copyright © 2021 Packt Publishing

Jim Ledin es el director ejecutivo de Ledin Engineering, Inc. Jim es un experto en diseño, desarrollo y pruebas de software y hardware integrados. También tiene experiencia en evaluación de ciberseguridad de sistemas integrados y pruebas de penetración. Tiene un B.S. Licenciado en ingeniería aeroespacial de la Universidad Estatal de Iowa y un M.S. Licenciatura en ingeniería eléctrica e informática del Instituto de Tecnología de Georgia. Jim es un ingeniero eléctrico profesional registrado en California, un profesional certificado en seguridad del sistema de información (CISSP), un hacker ético certificado (CEH) y un probador de penetración certificado (CPT).

Jim Ledin es el director ejecutivo de Ledin Engineering, Inc. Jim es un experto en diseño, desarrollo y pruebas de software y hardware integrados. También tiene experiencia en evaluación de ciberseguridad de sistemas integrados y pruebas de penetración. Tiene un B.S. Licenciado en ingeniería aeroespacial de la Universidad Estatal de Iowa y un M.S. Licenciatura en ingeniería eléctrica e informática del Instituto de Tecnología de Georgia. Jim es un ingeniero eléctrico profesional registrado en California, un profesional certificado en seguridad del sistema de información (CISSP), un hacker ético certificado (CEH) y un probador de penetración certificado (CPT). Contenidos relacionados:

- Diseño integrado con FPGA:recursos de hardware

- Las herramientas de código abierto ayudan a simplificar la programación FPGA

- Implementación de algoritmos de punto flotante en FPGA o ASIC

- Las herramientas de software migran el código de la GPU a FPGA para aplicaciones de inteligencia artificial

- Los FPGA desplazan a los ASIC en el ADAS basado en la visión de Subaru Eyesight

- Cómo los FPGA basados en flash simplifican los requisitos de seguridad funcional

- Aprovechar los beneficios de los FPGA instantáneos

- Configuración de FPGA usando flash NOR de alta velocidad

- Cómo está evolucionando la tecnología FPGA para cumplir con los nuevos requisitos del sistema de rango medio

Para obtener más información sobre Embedded, suscríbase al boletín informativo semanal por correo electrónico de Embedded.

Incrustado

- Qué es la programación del sistema integrado y sus lenguajes

- Qué es el diseño de sistemas integrados:pasos en el proceso de diseño

- Convertir macrodatos en datos inteligentes con IA incorporada

- Soluciones de diseño y desafíos de implementación del puerto USB tipo C

- Las tendencias clave de la industria están dando forma al diseño integrado

- Acelerador FPGA para cámaras MIPI de visión integrada

- La plataforma de código abierto apunta a IoT con Linux incorporado

- Clientron:TPV multifuncional con impresora integrada

- El kit de diseño mide la presión arterial con un sensor óptico

- FPGA de grado de defensa debuta con acceso anticipado

- Todo con aditivo