El chip de inferencia de hardware apunta a aplicaciones automotrices

AImotive, con sede en Hungría, un desarrollador de tecnologías de conducción automatizada basadas en software y hardware, ha comenzado a enviar su propiedad intelectual (IP) de motor de inferencia de hardware de red neuronal (NN) aiWare3 a sus clientes principales.

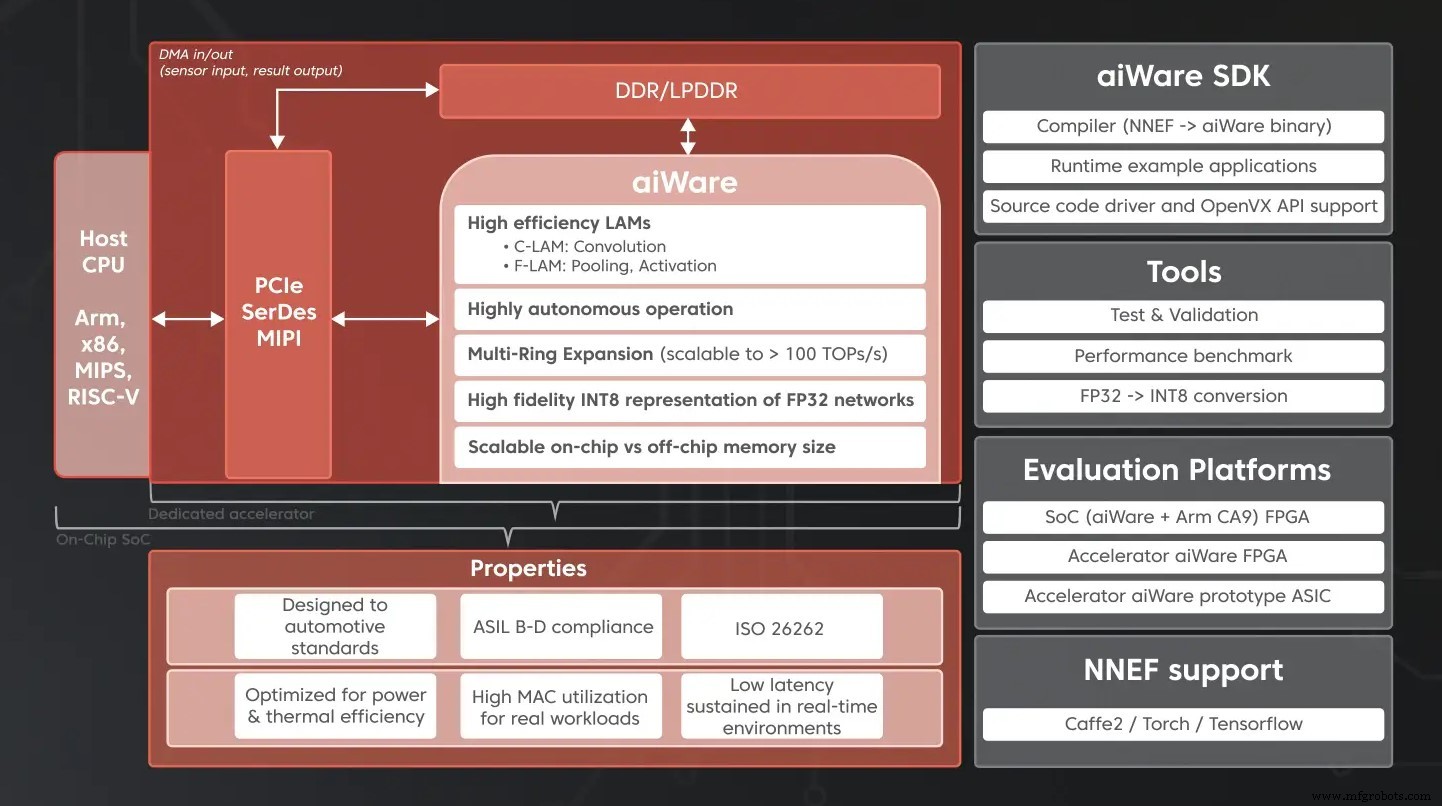

Su núcleo IP aiWare3P, que se anunció el año pasado, ofrece un acelerador NN de hardware para aplicaciones de visión automotriz de alta resolución y como un componente dentro de los subsistemas certificados ISO26262 ASIL A, B y superiores. El núcleo, que se puede implementar dentro de un sistema en chip (SoC), o como un acelerador NN independiente, se proporciona como RTL completamente sintetizable; su microarquitectura de bajo nivel está diseñada para usar mucho menos CPU de host o recursos de memoria compartida que otros aceleradores NN de hardware.

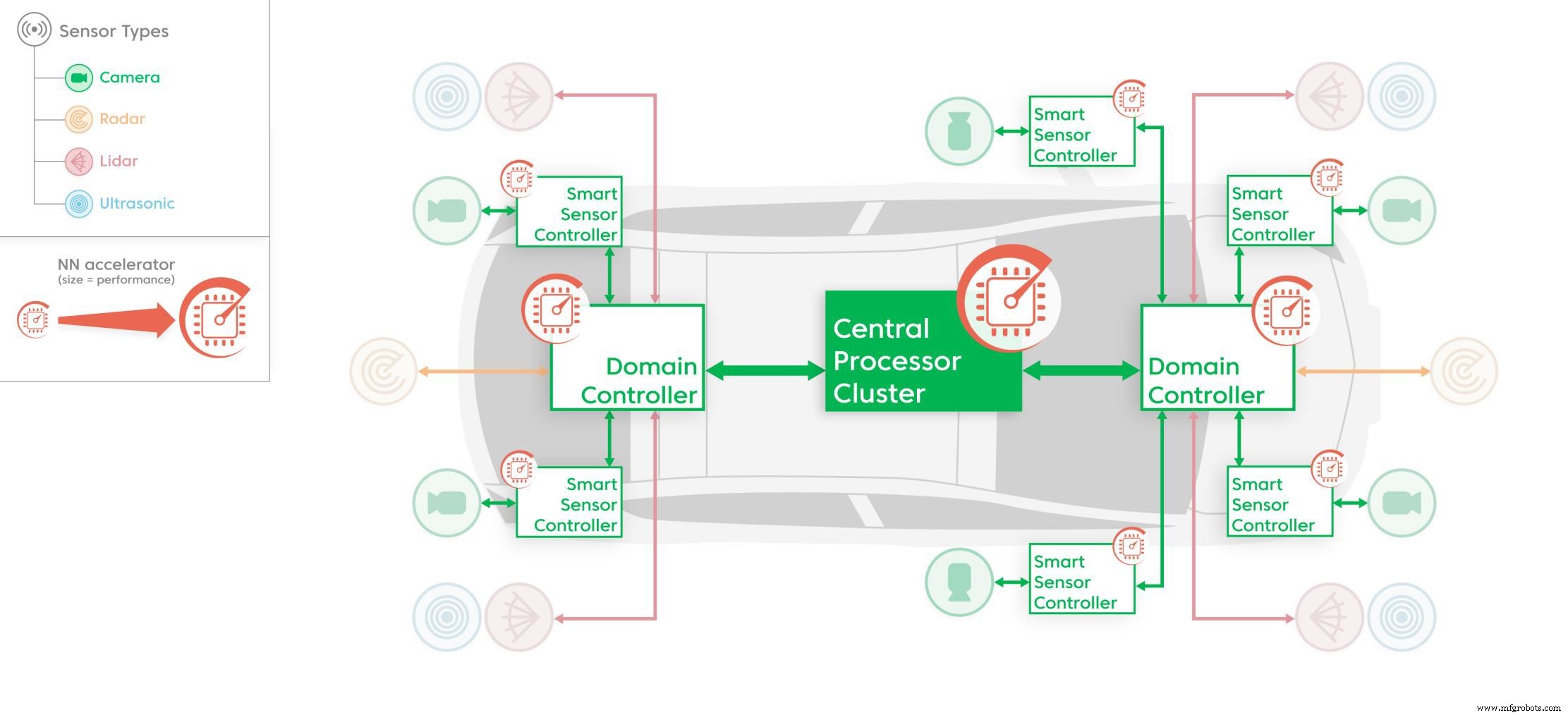

Aceleradores NN dedicados como el aiWare3P IP utilizado en varias partes de la plataforma electrónica del vehículo (Fuente:AImotive)

Aceleradores NN dedicados como el aiWare3P IP utilizado en varias partes de la plataforma electrónica del vehículo (Fuente:AImotive)

Hablando con EE Times Europe Tony-King Smith, el asesor ejecutivo de la empresa, dijo que la mayoría de los reproductores de chips hablan en términos académicos sobre las diferencias entre la oferta de AIMotive y otras soluciones, sobre los aceleradores basados en GPU y SoC, probados en un entorno de laboratorio, lo que realmente no se traduce bien. al mundo real. “La diferencia crucial es que es necesario comprender los principios de las redes neuronales en lugar del acelerador. En nuestra solución no hay DSP ni NOC (red en chip). aiWare solo está diseñado para inferencia automotriz, por lo que podemos proporcionar baja latencia desde la entrada hasta la salida ". Añadió que las mejoras en la salida RTL del nuevo núcleo significan que libera el subsistema principal de la CPU, y el núcleo se puede conectar a cualquier acelerador SoC.

El núcleo IP aiWare3P incorpora características que dan como resultado un rendimiento mejorado, un menor consumo de energía, una mayor descarga de la CPU del host y un diseño más simple para diseños de chips más grandes. Cada núcleo ofrece hasta 16 TMAC / s (> 32 TOPS) a 2GHz, con implementaciones de múltiples núcleos y chips capaces de entregar hasta 50+ TMAC / s (> 100 INT8 TOPS), útil para cámaras múltiples o heterogéneas aplicaciones ricas en sensores. El núcleo está diseñado para la operación de temperatura extendida AEC-Q100 e incluye características que permiten a los usuarios lograr la certificación ASIL-B y superior.

La escalabilidad del rendimiento del núcleo IP a más de 50 TMAC / s (> 100 TOPS) por chip y la inferencia sostenida de baja latencia es el resultado de su microarquitectura de bajo nivel. Utiliza un diseño de base patentado para una gestión de flujo de datos altamente determinista, con una arquitectura centrada en la memoria altamente paralela que ofrece hasta 100 veces más ancho de banda de memoria en el chip que otros aceleradores NN de hardware, lo que garantiza una eficiencia sostenida de hasta el 95% para los DNN complejos utilizados con grandes entradas como múltiples cámaras HD.

Al admitir NNEF de Khronos, así como entradas ONNX estándar abiertas, aiWare SDK compila directamente binarios sin necesidad de programación de bajo nivel de DSP o MCU. Incluye herramientas automatizadas para la cuantificación de FP32 a INT8 con poca o ninguna pérdida de precisión, junto con una cartera creciente de sofisticadas herramientas de análisis de rendimiento DNN. Estos últimos están diseñados para ayudar a los ingenieros de software e inteligencia artificial a migrar y transformar NN capacitados en un laboratorio en soluciones eficientes en tiempo real que se ejecutan en plataformas de hardware de producción automotriz impulsadas por aiWare.

Los componentes básicos de un acelerador de IA automotriz, incluida la IP de hardware aiWare (Fuente:AImotive)

Los componentes básicos de un acelerador de IA automotriz, incluida la IP de hardware aiWare (Fuente:AImotive)

Marton Feher, vicepresidente senior de ingeniería de hardware de AImotive, dijo:“Nuestra versión aiWare3P lista para producción reúne todo lo que sabemos sobre la aceleración de redes neuronales para aplicaciones de inferencia de IA automotrices basadas en visión. Ahora contamos con una de las soluciones de aceleración NN más eficientes y convincentes de la industria automotriz para la producción de volumen L2 / L2 + / L3 AI ".

El hardware IP aiWare3P se está implementando en una gama de soluciones de producción L2 / L2 +, además de ser adoptado para estudios de aplicaciones de sensores heterogéneos más avanzados. Los clientes incluyen Nextchip para su próximo Apache5 Imaging Edge Processor y ON Semiconductor para su proyecto de colaboración con AImotive para demostrar capacidades avanzadas de fusión de sensores heterogéneos.

AImotive dijo que lanzará una actualización completa de sus resultados de referencia pública en el primer trimestre de 2020 basada en el núcleo IP aiWare3P. Esto es parte de su compromiso con la evaluación comparativa abierta utilizando evaluaciones comparativas bien controladas que reflejen aplicaciones reales, como entradas de alta resolución para cámaras, en lugar de evaluaciones comparativas públicas poco realistas que utilizan entradas de 224 × 224.

No es necesaria la intervención de la CPU del host

Las nuevas características de la IP de hardware aiWare3P incluyen soporte para una cartera mucho mayor de funciones integradas de activación y agrupación pre-optimizadas, lo que garantiza que el 100% de la mayoría de los NN se ejecuten dentro del núcleo aiWare3P sin ninguna intervención de la CPU del host; compresión de datos en tiempo real, lo que reduce los requisitos de ancho de banda de la memoria externa, especialmente para tamaños de entrada más grandes y redes más profundas; y acoplamiento cruzado avanzado entre motores de convolución C-LAM y motores de función F-LAM, para aumentar la eficiencia de ejecución superpuesta e intercalada.

La microarquitectura física basada en mosaicos permite una implementación física más sencilla de grandes núcleos aiWare al minimizar las difíciles restricciones de tiempo en cualquier nodo de proceso; y la gestión de datos lógica basada en mosaicos permite una escalabilidad de carga de trabajo eficiente hasta el máximo de 16 TMAC / s por núcleo, sin la necesidad de cachés, NOC u otros enfoques complejos basados en procesadores de múltiples núcleos que crean cuellos de botella, reducen el determinismo y consumen más energía y área de silicio El aiWare3P RTL se enviará a todos los clientes a partir de enero de 2020, y un SDK actualizado incluye un compilador mejorado y nuevas herramientas de análisis de rendimiento para la estimación fuera de línea y el análisis detallado del hardware de destino en tiempo real.

Incrustado

- Infineon lanza la serie de energía integrada TLE985x para aplicaciones automotrices

- La arquitectura del chip AI apunta al procesamiento de gráficos

- Los aceleradores de hardware sirven aplicaciones de IA

- El sensor Hall apunta a sistemas automotrices críticos para la seguridad

- Se estrena el procesador de radar de imágenes automotrices de 30 fps

- EKF:plataforma de caja resistente para montaje en pared para aplicaciones ferroviarias, automotrices e industriales

- Portwell:el sistema de 19 ”apunta a aplicaciones de videowall

- Fibra de carbono en aplicaciones automotrices

- Compuestos de PPA endurecidos y estabilizados al calor para aplicaciones automotrices exigentes

- Tecnologías SGL Carbon destinadas a aplicaciones aeroespaciales y de automoción

- Robots en la fabricación de automóviles:7 aplicaciones principales