Contadores asincrónicos

En la sección anterior, vimos un circuito que usaba un flip-flop J-K que contaba hacia atrás en una secuencia binaria de dos bits, de 11 a 10 a 01 a 00.

Dado que sería deseable tener un circuito que pudiera contar hacia adelante y no solo hacia atrás, valdría la pena volver a examinar una secuencia de conteo hacia adelante y buscar más patrones que puedan indicar cómo construir dicho circuito.

Como sabemos que las secuencias de conteo binario siguen un patrón de división de frecuencia de octava (factor de 2), y que los multivibradores flip-flop JK configurados para el modo "alternar" son capaces de realizar este tipo de división de frecuencia, podemos imaginar un circuito compuesto por varios flip-flops JK, conectados en cascada para producir cuatro bits de salida.

El principal problema al que nos enfrentamos es determinar cómo para conectar estos flip-flops para que se muevan en el momento adecuado para producir la secuencia binaria adecuada.

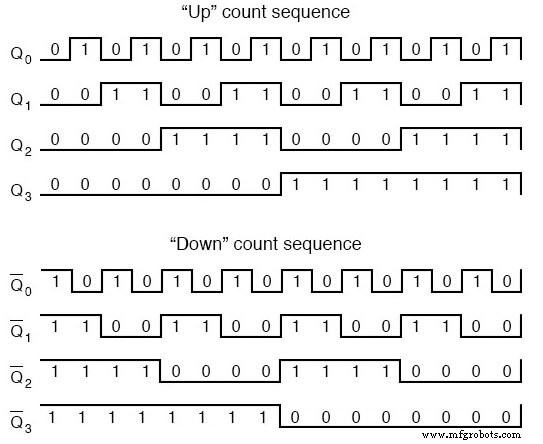

Examine la siguiente secuencia de conteo binario, prestando atención a los patrones que preceden al "cambio" de un bit entre 0 y 1:

Tenga en cuenta que cada bit en esta secuencia de cuatro bits cambia cuando el bit anterior (el bit que tiene un significado menor, o peso de posición), cambia en una dirección particular:de 1 a 0.

Las flechas pequeñas indican aquellos puntos en la secuencia donde un bit cambia, la punta de la flecha apunta al bit anterior pasando de un estado "alto" (1) a un estado "bajo" (0):

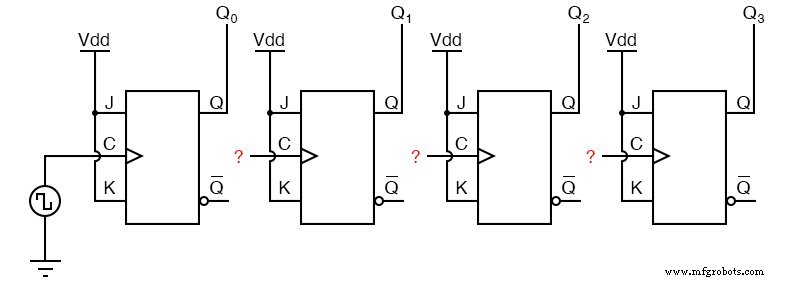

Comenzando con cuatro flip-flops JK conectados de tal manera que siempre estén en el modo "alternar", necesitamos determinar cómo conectar las entradas del reloj de tal manera que cada bit sucesivo alterne cuando el bit anterior cambie de 1 a 0.

Las salidas Q de cada flip-flop servirán como los respectivos bits binarios del recuento final de cuatro bits:

Si usamos flip-flops con activación de borde negativo (símbolos de burbuja en las entradas del reloj), simplemente podríamos conectar la entrada del reloj de cada flip-flop a la salida Q del flip-flop anterior, de modo que cuando el bit anterior cambia de 1 a 0, el "flanco descendente" de esa señal "sincronizaría" el siguiente flip-flop para alternar el siguiente bit:

Contador "ascendente" de cuatro bits

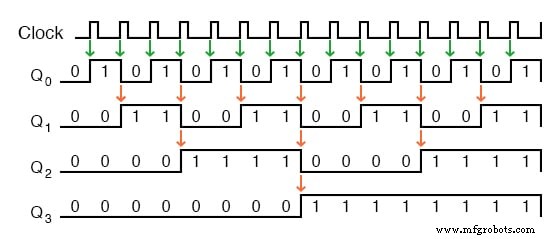

Este circuito produciría las siguientes formas de onda de salida, cuando se "sincroniza" mediante una fuente repetitiva de pulsos de un oscilador:

El primer flip-flop (el que tiene la Q 0 salida), tiene una entrada de reloj activada por flanco positivo, por lo que alterna con cada flanco ascendente de la señal de reloj.

Observe cómo la señal del reloj en este ejemplo tiene un ciclo de trabajo menor al 50%.

He mostrado la señal de esta manera con el propósito de demostrar cómo la señal de reloj no necesita ser simétrica para obtener bits de salida confiables y "limpios" en nuestra secuencia binaria de cuatro bits.

En el primer circuito flip-flop que se muestra en este capítulo, utilicé la señal del reloj como uno de los bits de salida.

Sin embargo, esta es una mala práctica en el diseño de contadores, ya que requiere el uso de una señal de onda cuadrada con un ciclo de trabajo del 50% (tiempo "alto" =tiempo "bajo") para obtener una secuencia de conteo donde todos y cada uno de los pasos hace una pausa durante la misma cantidad de tiempo.

Sin embargo, el uso de un flip-flop J-K para cada bit de salida nos libera de la necesidad de tener una señal de reloj simétrica, lo que permite el uso de prácticamente cualquier variedad de formas de onda altas / bajas para incrementar la secuencia de conteo.

Como lo indican todas las demás flechas en el diagrama de pulsos, cada bit de salida sucesivo se alterna mediante la acción del bit anterior que pasa de "alto" (1) a "bajo" (0).

Este es el patrón necesario para generar una secuencia de conteo "ascendente".

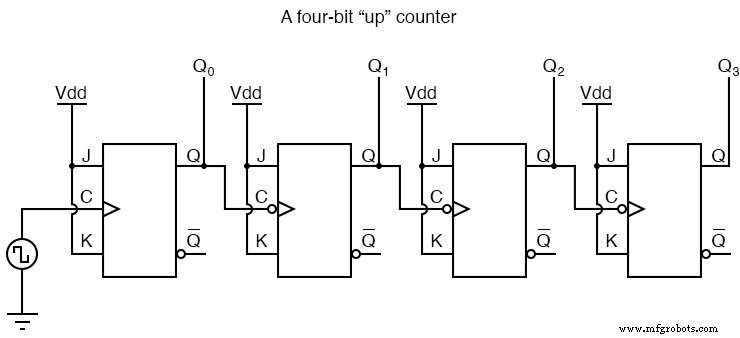

Una solución menos obvia para generar una secuencia "ascendente" usando flip-flops activados por flanco positivo es "cronometrar" cada flip-flop usando la salida Q ’del flip-flop anterior en lugar de la salida Q.

Dado que la salida Q 'siempre será el estado exactamente opuesto de la salida Q en un flip-flop JK (no hay estados inválidos con este tipo de flip-flop), una transición de alto a bajo en la salida Q irá acompañada de una transición de bajo a alto en la salida Q '.

En otras palabras, cada vez que la salida Q de un flip-flop cambia de 1 a 0, la salida Q 'del mismo flip-flop pasará de 0 a 1, proporcionando el pulso de reloj positivo que necesitaríamos para alternar un flip-flop activado por borde positivo en el momento correcto:

Contador alternativo de cuatro bits "ascendente"

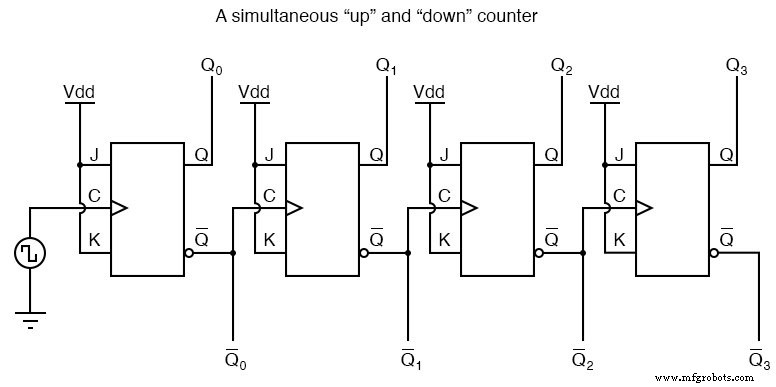

Una forma en que podríamos expandir las capacidades de cualquiera de estos dos circuitos contadores es considerar las salidas de Q como otro conjunto de cuatro bits binarios.

Si examinamos el diagrama de pulsos de dicho circuito, vemos que las salidas Q 'generan una baja -secuencia de conteo, mientras que las salidas Q generan un up -secuencia de conteo:

Contador simultáneo de "arriba" y "abajo"

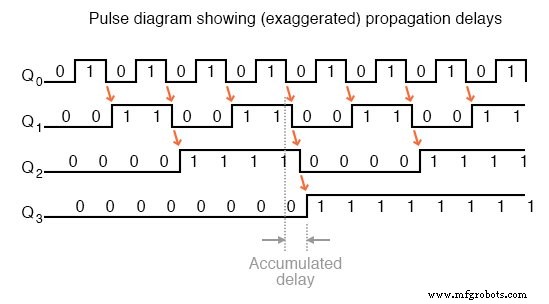

Desafortunadamente, todos los circuitos contadores mostrados hasta ahora comparten un problema común:la ondulación efecto.

Este efecto se ve en ciertos tipos de sumadores binarios y circuitos de conversión de datos, y se debe a retrasos de propagación acumulativos entre puertas en cascada.

Cuando la salida Q de un flip-flop cambia de 1 a 0, ordena al siguiente flip-flop que cambie.

Si el próximo cambio de flip-flop es una transición de 1 a 0, ordenará al flip-flop posterior que cambie también, y así sucesivamente.

Sin embargo, dado que siempre hay una pequeña cantidad de retardo de propagación entre el comando para alternar (el pulso del reloj) y la respuesta de alternancia real (las salidas Q y Q 'cambian de estado), cualquier flip-flops subsiguientes que se alternen alternará algún tiempo después el primer flip-flop ha cambiado.

Por lo tanto, cuando varios bits se alternan en una secuencia de conteo binario, no todos se alternarán exactamente al mismo tiempo:

Desventaja del circuito contador asíncrono:retardo de propagación

Como puede ver, cuantos más bits se alternen con un pulso de reloj dado, más severo será el tiempo de retardo acumulado de LSB a MSB.

Cuando se produce un pulso de reloj en un punto de transición de este tipo (por ejemplo, en la transición de 0111 a 1000), los bits de salida se "ondularán" en secuencia de LSB a MSB, ya que cada bit sucesivo alterna y ordena al siguiente bit que cambie también. , con una pequeña cantidad de retardo de propagación entre cada cambio de bit.

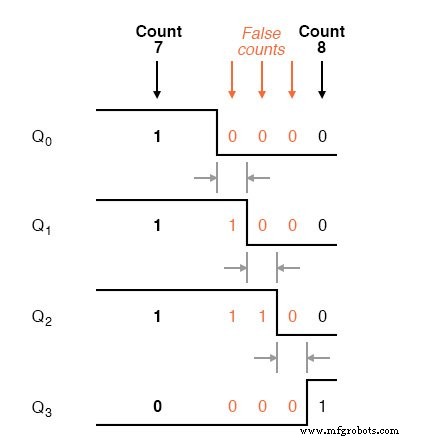

Si observamos de cerca este efecto durante la transición de 0111 a 1000, podemos ver que habrá falso recuentos de salida generados en el breve período de tiempo en el que tiene lugar el efecto "dominó":

En lugar de realizar una transición limpia de una salida "0111" a una salida "1000", el circuito del contador fluctuará muy rápidamente de 0111 a 0110 a 0100 a 0000 a 1000, o de 7 a 6 a 4 a 0 y luego a 8. Este comportamiento le otorga al circuito contador el nombre de contador de ondulaciones o contador asíncrono .

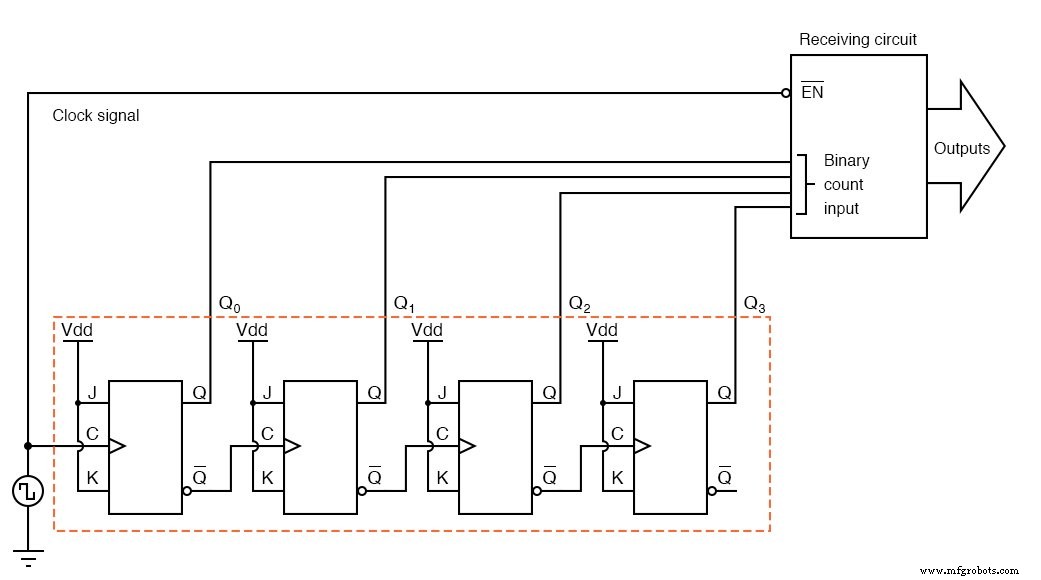

Circuito contador de señales estroboscópicas

En muchas aplicaciones, este efecto es tolerable, ya que la ondulación ocurre muy, muy rápidamente (la amplitud de los retrasos se ha exagerado aquí para ayudar a comprender los efectos).

Si todo lo que quisiéramos hacer fuera activar un conjunto de diodos emisores de luz (LED) con las salidas del contador, por ejemplo, esta breve ondulación no tendría ninguna consecuencia.

Sin embargo, si quisiéramos utilizar este contador para controlar las entradas "selectas" de un multiplexor, indexar un puntero de memoria en un circuito de microprocesador (computadora) o realizar alguna otra tarea en la que las salidas falsas pudieran causar errores espurios, no sería aceptable .

Hay una forma de utilizar este tipo de circuito contador en aplicaciones sensibles a salidas falsas generadas por ondas, e implica un principio conocido como estroboscópico .

La mayoría de los circuitos decodificadores y multiplexores están equipados con al menos una entrada llamada "habilitar".

Las salidas de dicho circuito estarán activas solo cuando la entrada de habilitación se active.

Podemos usar esta entrada de habilitación para estroboscópico el circuito que recibe la salida del contador de ondulación de modo que se deshabilita (y por lo tanto no responde a la salida del contador) durante el breve período de tiempo en el que las salidas del contador pueden estar ondulando, y se habilita solo cuando ha pasado suficiente tiempo desde el último pulso de reloj que toda ondulación habrá cesado.

En la mayoría de los casos, la señal estroboscópica puede ser el mismo pulso de reloj que impulsa el circuito contador:

Con una entrada de habilitación activa baja, el circuito de recepción responderá a la cuenta binaria del circuito contador de cuatro bits solo cuando la señal del reloj sea "baja".

Tan pronto como el pulso del reloj se vuelve "alto", el circuito receptor deja de responder a la salida del circuito contador.

Dado que el circuito contador se activa por flanco positivo (según lo determinado por el primero entrada de reloj flip-flop), toda la acción de conteo tiene lugar en la transición de baja a alta de la señal de reloj, lo que significa que el circuito receptor se desactivará justo antes de que ocurra cualquier cambio en los cuatro bits de salida del circuito contador.

El circuito de recepción no se habilitará hasta que la señal del reloj vuelva a un estado bajo, que debería ser lo suficientemente largo después toda la ondulación ha dejado de ser "segura" para permitir que el nuevo recuento tenga efecto en el circuito de recepción.

El parámetro crucial aquí es el tiempo "alto" de la señal del reloj:debe ser al menos tan largo como el período de ondulación máximo esperado del circuito contador.

De lo contrario, la señal del reloj habilitará prematuramente el circuito de recepción, mientras todavía se produce alguna ondulación.

Desventaja del circuito contador asíncrono:velocidad limitada

Otra desventaja del circuito contador asíncrono o rizado es la velocidad limitada.

Si bien todos los circuitos de puerta están limitados en términos de frecuencia de señal máxima, el diseño de circuitos contadores asíncronos agrava este problema al hacer que los retrasos de propagación sean aditivos.

Por lo tanto, incluso si se utiliza luz estroboscópica en el circuito de recepción, un circuito contador asíncrono no puede sincronizarse a ninguna frecuencia superior a la que permite que transcurra el mayor retardo de propagación acumulado posible mucho antes del siguiente pulso.

La solución a este problema es un circuito contador que evita la ondulación por completo.

Un circuito contador de este tipo eliminaría la necesidad de diseñar una función "estroboscópica" en cualquier circuito digital que utilice la salida del contador como entrada, y también disfrutaría de una velocidad de funcionamiento mucho mayor que su equivalente asíncrono.

Este diseño de circuito contador es el tema de la siguiente sección.

REVISAR:

- Se puede hacer un contador "ascendente" conectando las entradas de reloj de los flip-flops J-K activados por flanco positivo a las salidas Q ’de los flip-flops anteriores. Otra forma es utilizar flip-flops activados por borde negativo, conectando las entradas de reloj a las salidas Q de los flip-flops anteriores. En cualquier caso, las entradas J y K de todos los flip-flops están conectadas a V cc o V dd para estar siempre "alto".

- Los circuitos contadores hechos de flip-flops J-K en cascada donde cada entrada de reloj recibe sus pulsos de la salida del flip-flop anterior exhiben invariablemente un efecto dominó , donde se generan recuentos de salida falsos entre algunos pasos de la secuencia de recuento. Estos tipos de circuitos contadores se denominan contadores asíncronos o contadores de ondas .

- Luz estroboscópica es una técnica aplicada a los circuitos que reciben la salida de un contador asíncrono (rizado), de modo que los falsos recuentos generados durante el tiempo de rizado no tengan ningún efecto negativo. Básicamente, habilitar La entrada de dicho circuito está conectada al pulso de reloj del contador de tal manera que se habilita solo cuando las salidas del contador no cambian, y se inhabilitará durante los períodos de cambio de las salidas del contador donde se produce la ondulación.

HOJAS DE TRABAJO RELACIONADAS:

- Hoja de trabajo del contador de ondulaciones

Tecnología Industrial